汽車音響導航系統中DDR高速信號的PCB設計(2)

2012年02月06日 10:51 來源:《科技創新導報》 作者:王文靜 我要評論(0)

為控制傳輸線的阻抗及延時等的影響, 要先確定以下的布線設計標準:

*高速信號線條寬度,以保證傳輸線特性阻抗值:差分信號Zo 100Ω,其他信號Zo≒50Ω。

*為減少傳輸線間的串擾,確定最小間距值。實際布線時要盡可能加大間距。

*可用過孔的孔直徑及過孔焊盤直徑:

①Build-up積層激光沖壓孔②內層盲埋孔(L2到L5使用)③通孔(L1到L6用)④各種過孔焊盤間最小間距。

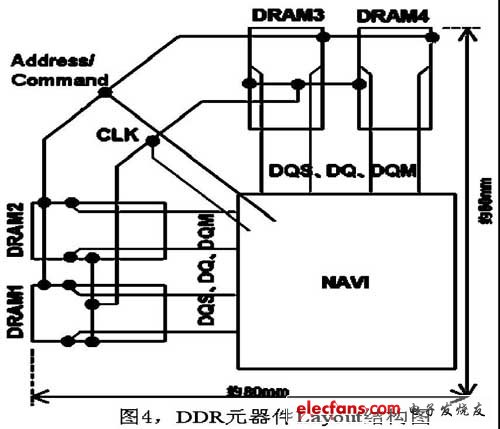

3.3 DDR SDRAM器件的布局結構圖

DDR的數據傳送通常是一個發射端對應多個接收端的結構, 為實現數據的同步傳送,延遲時間的控制尤為重要。在構建器件Layout的時候重點考慮傳輸線分歧節點的選定,各段傳輸長度相等等要求。如圖4,將DDR相關電路中的元器件都放在同一個面上, 并通過" 星型及Y 型拓撲結構"實現CLK、Data數據組,及Address/Command等各數據組之間的等長布線控制。

3.4 高頻信號的布線優先順序

依照設計要求的嚴格程度從最重要的信號線開始布起,順序為:

CLK→Data→Address/Command

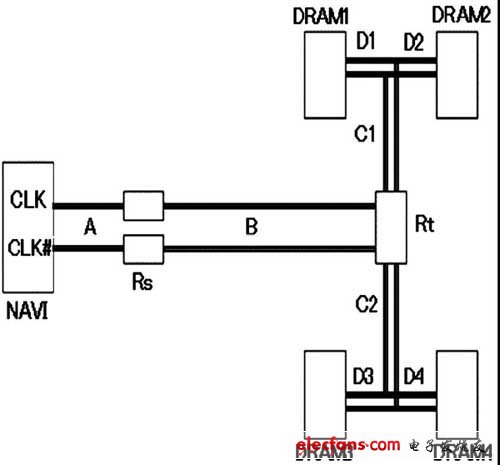

3.5 CLK差分信號的布線方法

針對DDR200中使用的CLK差分信號,布線拓撲圖如圖5 .布線注意點如下:

①差分阻抗要實現100Ω。

② 差分對CLK與CLK# 要等長布線,但總長度不要過長。

即CLK( A - B - C 1 - D 1 ) = CLK( A - B -C1-D2)= CLK( A - B - C 2 - D 3 ) = CLK( A - B -C2-D4)3.6 DATA組的布線方法。

圖5 CLK布線拓撲圖

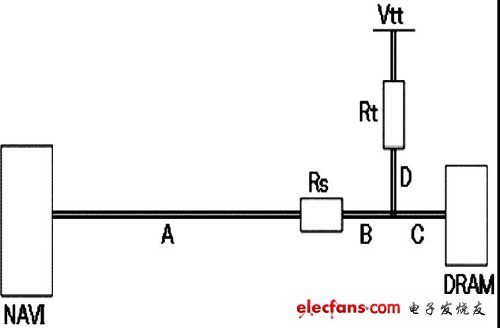

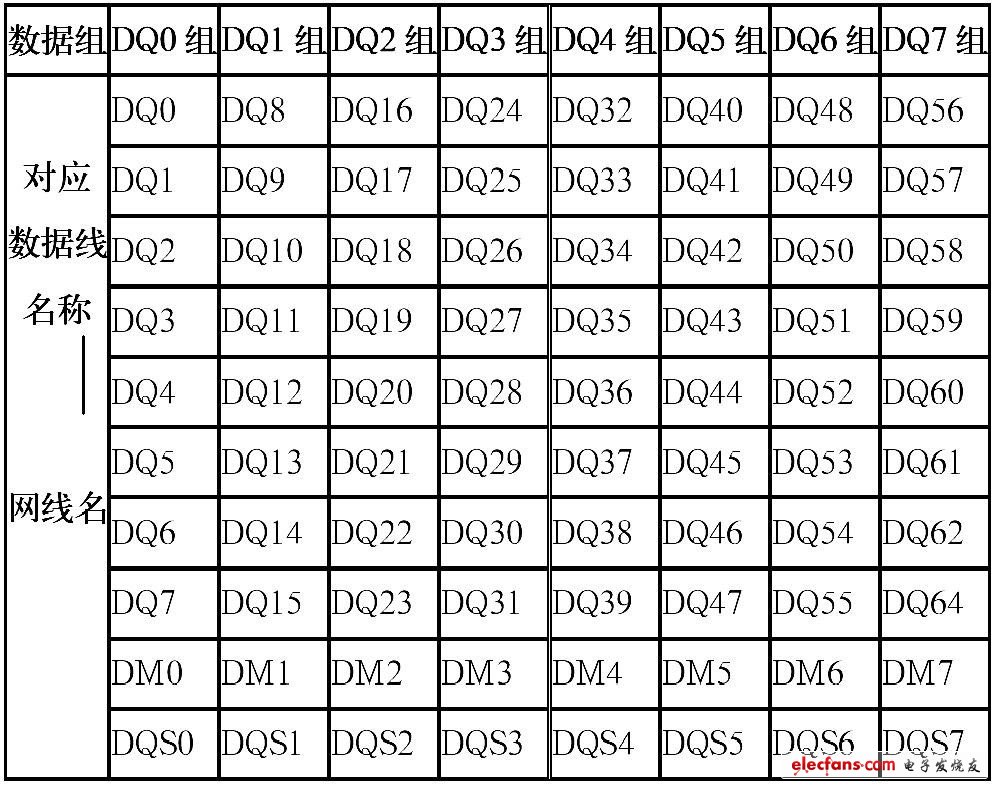

如圖6, 標明了DATA組所選的布線拓撲圖。布線注意點如下:

① 所有D A T A 信號從N A V I - C P U出發到每個D R A M 的長度都要相等( 即A - B - C段)。

②等長布線的誤差可以按同一Bit列及各組Bit間的誤差來控制,如表2。

圖6 DATA數據組的布線拓撲圖

表2

本文導航

- 第 1 頁:汽車音響導航系統中DDR高速信號的PCB設計(1)

- 第 2 頁:DDR SDRAM信號的布線標準

- 第 3 頁:Address/Command的布線方法