從字面上理解上升沿和下降沿是一個(gè)變量變化的時(shí)刻和一個(gè)無(wú)窮小的時(shí)間。但是plc程序中最小的時(shí)間單位是掃描周期,所以所謂的邊沿就是一個(gè)掃描周期。

?

?上例中使用的bTrig變量都是用來(lái)讓下面的程序執(zhí)行一個(gè)掃描周期的,也可以理解為執(zhí)行bTrig的上升沿,和下面的編程效果一樣:

?

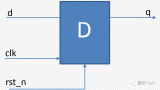

?上升功能塊R_TRIG的功能實(shí)際上是檢測(cè)輸入變量,當(dāng)輸入變量從低電平變?yōu)楦唠娖綍r(shí),在第一掃描周期輸出高電平,然后輸出低電平。即,輸出一個(gè)掃描周期。

?

?與上升沿相同,下降沿檢測(cè)輸入變量從高到低變化的第一個(gè)掃描周期。

?

?為了理解的上升沿和下降沿的含義,我們可以靈活地將其應(yīng)用到程序中,比如讓程序執(zhí)行一個(gè)掃描周期,檢測(cè)一個(gè)變量的上升/下降沿,通過(guò)設(shè)置我們上面例子中的IF語(yǔ)句來(lái)重置一個(gè)變量,或者在案例中執(zhí)行一個(gè)條件后立即更改判斷變量的值,等等。

?

?本文原創(chuàng)首發(fā) m.1cnz.cn 源自 www.jcpeixun.com 轉(zhuǎn)載請(qǐng)注明出處,謝謝。

編輯:ymf

上升沿和下降沿是什么意思?

- plc(453901)

- 高電平(20884)

相關(guān)推薦

stm32外部中斷的邊沿檢測(cè)時(shí),對(duì)上升沿或者下降沿是否有要求?

請(qǐng)問(wèn)各位大佬,stm32外部中斷的邊沿檢測(cè)時(shí),對(duì)上升沿或者下降沿是否有要求,必須小于或者大于多少時(shí)間,或者在多少時(shí)間內(nèi)必須上升或者下降多少V才算觸發(fā)。在spec中只看到了最小是10ns就可以,同時(shí)邊沿檢測(cè)的電平是GPIO的VIH和VIL嗎?

2024-03-20 08:31:04

使用HAL庫(kù)配置TIM2采集PWM測(cè)量頻率和脈沖寬度,如果將邊沿極性配置為上升+下降沿?

使用HAL庫(kù)配置TIM2采集PWM測(cè)量頻率和脈沖寬度,如果將邊沿極性配置為上升+下降沿,就可以一個(gè)通道測(cè)量頻率和占空比了,但是如何在HAL_TIM_IC_CaptureCallback中分辨此次中斷是由上升沿產(chǎn)生的,還是由下降沿產(chǎn)生的呢?

2024-03-12 06:52:38

HMC955LC4B

HMC955LC4B是一款1:2解復(fù)用器,支持高達(dá)32 Gbps的數(shù)據(jù)傳輸速率。該解復(fù)用器使用半速率時(shí)鐘的上升沿和下降沿對(duì)01-02序列中的數(shù)據(jù)進(jìn)行采樣,并在上升沿上將數(shù)據(jù)鎖存到差分輸出。該解復(fù)用器

2024-03-03 13:22:40

示波器探頭的工作原理與多功能應(yīng)用詳解

容性負(fù)載相當(dāng)于在被測(cè)電路上并聯(lián)了一個(gè)電容,對(duì)被測(cè)信號(hào)有濾波的作用,影響被測(cè)信號(hào)的上升下降時(shí)間,影響傳輸延遲,影響傳輸互連通道的帶寬。

2024-02-26 10:23:59 621

621

621

621

串行通信協(xié)議的帶寬是指什么?

在SPI和I2C等串行通信協(xié)議,兩者帶寬不一樣,這里的帶寬是指什么,傳輸速率還是其他什么?如果要求很高的傳輸速率,那么要求發(fā)送端要能很快的發(fā)送數(shù)據(jù),要有很短的上升沿下降沿時(shí)間,高低位電平也維持很短

2024-02-08 18:04:50

上升沿和下降沿是什么意思 上升沿和下降沿有何作用

上升沿和下降沿是什么意思 上升沿和下降沿有何作用? 上升沿和下降沿是在數(shù)字電路和信號(hào)處理中常用的概念,用于描述信號(hào)從低電平到高電平或從高電平到低電平的過(guò)程。 在數(shù)字電路中,信號(hào)通常是以離散的高電平

2024-02-06 14:50:04 1231

1231

1231

1231為什么脈沖數(shù)字信號(hào)的波形中其上升沿和下降沿展開(kāi)后會(huì)有邊沿震蕩

為什么脈沖數(shù)字信號(hào)的波形中,其上升沿和下降沿展開(kāi)后會(huì)有邊沿震蕩,求解釋 脈沖數(shù)字信號(hào)的波形中,上升沿和下降沿展開(kāi)后會(huì)出現(xiàn)邊沿震蕩的現(xiàn)象。這個(gè)現(xiàn)象通常是由信號(hào)傳輸過(guò)程中的反射、傳導(dǎo)和輻射等因素產(chǎn)生

2024-02-06 14:49:41 245

245

245

245d觸發(fā)器有幾個(gè)穩(wěn)態(tài) 觸發(fā)器上升沿下降沿怎么判斷

的上升沿和下降沿。 一、SR觸發(fā)器 SR觸發(fā)器是最基本的觸發(fā)器之一,通過(guò)它可以實(shí)現(xiàn)存儲(chǔ)器、寄存器等功能。 SR觸發(fā)器有兩個(gè)輸入:S和R,以及兩個(gè)輸出:Q和Q'。在SR觸發(fā)器中,有四種不同的輸入組合,分別是: S=0,R=0:保持狀態(tài),穩(wěn)態(tài)

2024-02-06 13:36:55 366

366

366

366plc中常用的編寫(xiě)程序的語(yǔ)言有哪些 plc中上升沿和下降沿怎么用

梯形圖是PLC中最常用和最廣泛支持的編程語(yǔ)言。它以線(xiàn)圖的形式展現(xiàn),使用繼電器邏輯圖形符號(hào)來(lái)表示邏輯關(guān)系和控制流程。

2024-01-10 15:04:17 143

143

143

143關(guān)于雅特力AT32F403A XMC復(fù)用模式驅(qū)動(dòng)SRAM芯片

復(fù)用模式寫(xiě)時(shí)序圖

SRAM寫(xiě)時(shí)序參數(shù),看-55的

SRAM寫(xiě)時(shí)序1,有刪減

.SRAM寫(xiě)時(shí)序2

鎖存器74LVC273參數(shù),算上上升沿和下降沿,延遲至少11ns

其中sram

2024-01-04 10:46:19

使用LT8705過(guò)程中上下功率MOS管的死區(qū)時(shí)間最小是多少?

您好!

我請(qǐng)教一個(gè)關(guān)于LT8705死區(qū)時(shí)間的問(wèn)題:客戶(hù)在使用LT8705過(guò)程中想確認(rèn)上下功率MOS管的死區(qū)時(shí)間最小是多少?目前客戶(hù)測(cè)試結(jié)果只有30ns左右。而根據(jù)MOS的上升沿和下降沿從20ns到40ns不等,有直通的風(fēng)險(xiǎn),請(qǐng)問(wèn)LT8705是怎么調(diào)節(jié)死區(qū)時(shí)間防止直通的?謝謝!!

2024-01-03 06:23:18

AD9266輸出數(shù)據(jù)的沿和時(shí)鐘的沿為什么是對(duì)齊的?

AD9266輸出數(shù)據(jù)是在輸出時(shí)鐘的上升沿和下降沿處都有數(shù)據(jù),我的電路的是二進(jìn)制補(bǔ)碼輸出,10k的偏置電阻選用0.1%,電壓0.5v,輸出的DCS的時(shí)鐘沒(méi)有任何問(wèn)題,頻率和沿都很穩(wěn)定,但是輸出的數(shù)據(jù)的沿和時(shí)鐘的沿是對(duì)齊的,這個(gè)和數(shù)據(jù)手冊(cè)的說(shuō)明不同!!!糾結(jié)了很久,跪求可能的原因!!!

2023-12-22 08:12:03

怎么確定AD9923A的VPAT_NUM和VSEQ_NUM這兩個(gè)寄存器的值呢?

本人剛接觸關(guān)于CCD的知識(shí),正在利用AD9923A調(diào)試ICX209AK,但在配置寄存器時(shí)遇到了一些問(wèn)題,想問(wèn)問(wèn)各位做過(guò)類(lèi)似項(xiàng)目的:

1.對(duì)于CCD所需的H1、H2、RG等信號(hào),怎么確定它的上升沿

2023-12-22 07:58:47

使用AD9266遇到的問(wèn)題求解

使用?2.ad9266是CMOS DDR數(shù)據(jù)輸出,通過(guò)管腳配置成二進(jìn)制補(bǔ)碼形式,DDR數(shù)據(jù)送到fpga,fpga選用xilinx的XC6SLX75,fpga內(nèi)部在ad9266輸出的ad_dco時(shí)鐘的上升沿和下降沿

2023-12-22 06:59:24

ad9942 Hcounter在VD_X下降沿的后第七個(gè)cli上升沿置0,這里的作用是是什么?

問(wèn)題1 如下圖,Hcounter 在VD_X下降沿的后第七個(gè)cli上升沿置0,這里的作用是是什么,為什么在第七個(gè)位置置0?Hcounter 在ad9942內(nèi)部那些信號(hào)或者序列會(huì)使用到? 有沒(méi)有VD

2023-12-21 06:08:03

AD2S1200串行輸出波形為什么在上升沿就變化了?

應(yīng)該是在下降沿才會(huì)有數(shù)據(jù)變化的啊,上圖中有在上升沿就變化了,這是什么原因啊???

急急急!!!

2023-12-20 06:14:13

AD9781或是AD9783芯片的DCOP/DCON信號(hào)有什么用?

/DCON信號(hào)是AD給FPGA發(fā)信數(shù)據(jù)使用的,如上升沿時(shí)FPGA發(fā)送I路信號(hào),下降沿時(shí)FPGA發(fā)送Q路信號(hào),此時(shí)上升沿與下降沿需要在I或Q路信 號(hào)的中間位置么,就是保證上升沿與下降沿時(shí),I和Q路信號(hào)有

2023-12-18 06:41:34

AD7764啟動(dòng)采樣的時(shí)鐘是MCLK還是SCO,如果是SCO,是上升沿啟動(dòng)還是下降沿啟動(dòng)?

最近在使用AD7764,有幾個(gè)不懂的地方想請(qǐng)教一下:

1.AD7764啟動(dòng)采樣的時(shí)鐘是MCLK還是SCO,如果是SCO,是上升沿啟動(dòng)還是下降沿啟動(dòng)?

2.根據(jù)datasheet操作指引,上電后

2023-12-15 07:05:23

adcmp604的上升沿和下降沿時(shí)間怎么做到更短?

我再用adcmp604的時(shí)候,上升沿和下降沿在10多個(gè)ns,比規(guī)格書(shū)上給的長(zhǎng)好多,怎么能做到更短?

2023-12-08 08:11:17

關(guān)于AD6688采樣單音信號(hào)時(shí)比較奇怪的現(xiàn)象

的2211.84MHz,當(dāng)我給一個(gè)2211.84MHz的正弦信號(hào)時(shí),我期待得到的是一條直線(xiàn),因?yàn)轭l率被移動(dòng)到了DC了。但是采集回來(lái)的數(shù)據(jù)卻很奇怪,在一段時(shí)間會(huì)是固定的,但是另一端時(shí)間會(huì)有上升沿和下降沿

2023-12-01 07:09:14

AD8561單+5V供電,方波輸入,仿真下降沿比上升沿延時(shí)大是為什么?

AD8561單+5V供電,方波輸入,仿真下降沿比上升沿延時(shí)大,如果雙電源則延時(shí)則一樣,實(shí)際應(yīng)用是否也是這樣?官網(wǎng)的pspice模型

2023-11-24 06:17:21

i.MX-6ULL --ElfBoard SPI接口介紹

主設(shè)備。一主多從情況如下圖:

SPI 具有 4 種工作方式,時(shí)鐘極性(CPOL)和相位(CPHA)共同決定讀取數(shù)據(jù)的方式,比如信號(hào)上升沿讀取數(shù)據(jù)還是信號(hào)下降沿讀取數(shù)據(jù),并且一個(gè)片選信號(hào)可以設(shè)置一種模式

2023-11-21 10:19:05

AD817運(yùn)放輸出大約1V的振鈴怎樣處理?

用AD817運(yùn)放搭建的負(fù)反饋電路中,空載測(cè)試輸出波形在上升沿和下降沿會(huì)出現(xiàn)1V多的振鈴,應(yīng)該怎樣處理能把振林消除

2023-11-17 15:07:28

ada4870是否可以用作直流線(xiàn)性電源?

100pf-10nf。

目前,我們已經(jīng)驗(yàn)證的電路采用了類(lèi)似于線(xiàn)性電源的結(jié)構(gòu),如圖所示。

現(xiàn)在存在的問(wèn)題是:圖1中,三極管射級(jí)輸出的直流電平存在較大的紋波,同時(shí)推完電路輸出方波的上升沿和下降沿存在

2023-11-17 14:10:15

用AD8009放大500uv的方波,電壓抬升怎么優(yōu)化?

您好:

我希望放大一個(gè)500uv的1PPS方波,需要比較好的上升沿和下降沿性能,選用了AD8009,放大了300倍,測(cè)試后發(fā)現(xiàn)電壓被抬高很多,是否是Vos引起的?

閱讀相關(guān)帖子,我現(xiàn)在覺(jué)得我的設(shè)計(jì)有

2023-11-14 06:07:04

ADL5303光電二極管放大電路,低輸入光抖動(dòng)如何消除?

您好!

我使用ADL5303做光電二極管放大電路,因?yàn)轫憫?yīng)速度的原因使用RC濾波電路會(huì)導(dǎo)致信號(hào)上升沿和下降沿時(shí)間變長(zhǎng),所以C118和C122都不能焊接,在低輸入光時(shí)Vlog端有出現(xiàn)520KHZ、1MHZ、1.5MHZ的抖動(dòng),使用多種方法仍然無(wú)法消除,想尋求解決抖動(dòng)的方法,謝謝!

2023-11-13 06:30:13

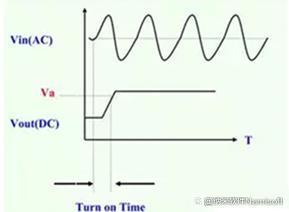

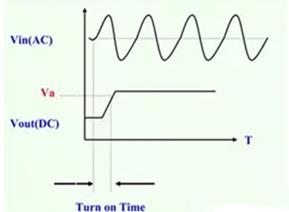

使用ATECLOUD電源測(cè)試系統(tǒng)測(cè)試啟動(dòng)延遲和上升/下降時(shí)間

在集成電路中經(jīng)常會(huì)使用電源模塊來(lái)保證電路的穩(wěn)壓輸出,所以電源模塊的應(yīng)用十分的廣泛

2023-11-09 17:33:41 576

576

576

576

SPI的MISO管腳的波形上升沿和下降沿都有很大的弧度是什么原因?

示波器測(cè)量SPI通訊的CS,CLKMOSIMISO四顆線(xiàn)的信號(hào),發(fā)現(xiàn)其他都很好,只有MISO的信號(hào)上升沿和下降沿都是有很大弧度的,是什么原因,如何解決?

2023-11-08 06:19:01

納米軟件電源模塊測(cè)試之啟動(dòng)延遲和上升/下降時(shí)間

電源模塊的啟動(dòng)延遲指從施加啟動(dòng)輸入電壓到輸出電壓達(dá)到電壓額定值時(shí)所需的時(shí)間,上升時(shí)間是指電源模塊從歸零待機(jī)狀態(tài)到啟動(dòng)狀態(tài)所需的時(shí)間,下降時(shí)間指的是電源模塊從工作狀態(tài)到歸零待機(jī)狀態(tài)所需的時(shí)間。

2023-10-09 15:50:04 307

307

307

307

51單片機(jī)如何實(shí)現(xiàn)上升壓和下降沿中斷?

如何用一個(gè)外部中斷口實(shí)現(xiàn)上升壓和下降沿都進(jìn)入中斷函數(shù)

2023-10-07 09:05:55

STC8系列單片機(jī)技術(shù)參考手冊(cè)

、增強(qiáng)型 PWM、增強(qiáng)型 PWM 異常檢測(cè)、ADC 模數(shù)轉(zhuǎn)換中斷、LVD 低壓檢測(cè)、SPI 中斷、I2C 中斷、比較器中斷喚醒。STOP 模式可以由 INT0/INT1 端口上升沿/下降沿、INT2

2023-09-26 07:36:13

求分享K210裸機(jī)開(kāi)發(fā)的寄存器手冊(cè)

K210芯片使用PWM時(shí),無(wú)法指定對(duì)齊下降沿或者上升沿,從0計(jì)數(shù)到loadcount2翻轉(zhuǎn)為低,然后從0計(jì)數(shù)到channel[N].loadcount再翻轉(zhuǎn)為高,無(wú)法通過(guò)current_value

2023-09-15 07:36:14

異步時(shí)鐘同步疑惑

?也就是說(shuō)采樣異步時(shí)鐘域信號(hào)時(shí)不打拍有什么后果?

另外,當(dāng)高速時(shí)鐘采樣慢速上升沿或下降沿時(shí),采樣結(jié)果抖動(dòng)怎么處理?比如DS18B20長(zhǎng)線(xiàn)驅(qū)動(dòng)時(shí),波形上升沿和下降沿被長(zhǎng)線(xiàn)的線(xiàn)間電容牽制導(dǎo)致波形邊沿變化緩慢 ,采用打2拍方式能否有用?

此圖采樣到緩慢上升沿時(shí),采樣結(jié)果抖動(dòng)波形。

2023-09-12 20:39:18

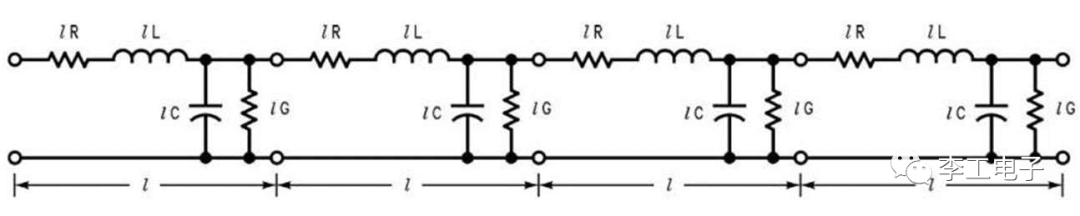

走線(xiàn)什么時(shí)候必須作為傳輸線(xiàn)考慮?

簡(jiǎn)單地說(shuō),傳輸線(xiàn)是由兩條有一定長(zhǎng)度的導(dǎo)線(xiàn)組成。如果信號(hào)在導(dǎo)線(xiàn)上的傳輸時(shí)間大于信號(hào)的跳變沿(上升沿/下降沿)時(shí)間的一半,則該走線(xiàn)判定為傳輸線(xiàn)。

2023-09-06 14:49:28 215

215

215

215

N9H20K51 gpio觸發(fā)后一直未進(jìn)中斷是為什么?

輸入模式

gpio_setintmode (GPIO_PORTE, BIT11, 1, 1);//設(shè)置中斷模式上升沿 和下降沿

gpio_setsrcgrp(GPIO_PORTE,BIT11

2023-09-04 07:40:57

求助,在STM32上RTT可以使用IO中斷模擬I2C從機(jī)接收數(shù)據(jù)嗎?

使用IO中斷在SCL上升沿和下降沿接收解析SDA的狀態(tài)讀取IIC數(shù)據(jù),RTT的IO中斷可以及時(shí)響應(yīng)嗎?

2023-09-03 09:49:08

有源晶振的電氣參數(shù):波形上升下降時(shí)間

晶振的輸出波形為單端輸出(Sine/Clipped Sine, CMOS/TTL) 和差分輸出(LVPECL, LVDS, HCSL)。差分輸出可以滿(mǎn)足高速數(shù)據(jù)傳輸,應(yīng)用于高速計(jì)算機(jī),數(shù)字通信系統(tǒng),雷達(dá),測(cè)量?jī)x器,頻率合成器等。

2023-08-25 11:01:08 619

619

619

619

RTL設(shè)計(jì)規(guī)范有哪些?一個(gè)RTL用例設(shè)計(jì)介紹

D觸發(fā)器結(jié)構(gòu)如下圖所示,先有時(shí)鐘上升沿,然后才有D的值賦給Q,沒(méi)有上升沿Q值保持不變,時(shí)序邏輯在時(shí)鐘上升沿/下降沿后才變化

2023-08-18 10:23:36 1149

1149

1149

1149

M0518LD2設(shè)置上升沿中斷,但卻也相應(yīng)了下降沿中斷是為什么?

M0518LD2 外部中斷初始化時(shí)設(shè)置PD6為上升沿中斷,但經(jīng)查看波形發(fā)現(xiàn) PD6在下降沿時(shí)也觸發(fā)了中斷,不知為何?

2023-08-18 06:13:40

ARM MultiTrace用戶(hù)指南

·支持4位、8位和16位的數(shù)據(jù)端口寬度。

·支持半速率跟蹤時(shí)鐘,可在時(shí)鐘上升沿和下降沿捕獲數(shù)據(jù)。

·SoC電壓可以在1.0至3.3V的范圍內(nèi)。

·軌跡信息以10 ns的分辨率進(jìn)行時(shí)間標(biāo)記。

·多重跟蹤

2023-08-16 06:11:46

【筆記本維修入門(mén)教程】第二章:第8集. 上升沿和下降沿的概念解釋 - 第3節(jié) #硬聲創(chuàng)作季

筆記本電路維修

充八萬(wàn)發(fā)布于 2023-08-14 17:21:00

【筆記本維修入門(mén)教程】第二章:第8集. 上升沿和下降沿的概念解釋 - 第2節(jié) #硬聲創(chuàng)作季

筆記本電路維修

充八萬(wàn)發(fā)布于 2023-08-14 17:20:11

【筆記本維修入門(mén)教程】第二章:第8集. 上升沿和下降沿的概念解釋 - 第1節(jié) #硬聲創(chuàng)作季

筆記本電路維修

充八萬(wàn)發(fā)布于 2023-08-14 17:19:20

淺析PLC的上升沿與下降沿

有網(wǎng)友留言說(shuō):上升沿就是在信號(hào)從斷開(kāi)到接通的那一瞬間接通,下降沿就是在信號(hào)從接通到斷開(kāi)的那一瞬間接通。但是現(xiàn)在的問(wèn)題它的實(shí)際用處是用在哪一些情況。我身邊也有PLC可以做個(gè)什么實(shí)驗(yàn)來(lái)體驗(yàn)一下呢?

2023-07-26 09:24:30 1470

1470

1470

1470HMC855LC5是一款串行器

HMC855LC5是一款1:4解復(fù)用器,設(shè)計(jì)用于高達(dá)28 Gbps數(shù)據(jù)解串應(yīng)用。 該器件使用半速率時(shí)鐘的上升沿和下降沿來(lái)采樣輸入數(shù)據(jù)序列D0-D3,并將數(shù)據(jù)鎖存至差分輸出。 片上生成1/4速率時(shí)鐘

2023-07-11 09:43:06

HMC854LC5是一款串行器

HMC854LC5是一款4:1多路復(fù)用器,設(shè)計(jì)用于28 Gbps數(shù)據(jù)串行應(yīng)用。 多路復(fù)用器在輸入時(shí)鐘的上升沿鎖存四個(gè)差分輸入。 該器件使用半速率時(shí)鐘的上升沿和下降沿來(lái)串行傳輸數(shù)據(jù)。 片上生成1/4

2023-07-11 09:39:21

HMC955LC4B是一款串行器

HMC955LC4B是一款1:2解復(fù)用器,支持高達(dá)32 Gbps的數(shù)據(jù)傳輸速率。該解復(fù)用器使用半速率時(shí)鐘的上升沿和下降沿對(duì)01-02序列中的數(shù)據(jù)進(jìn)行采樣,并在上升沿上將數(shù)據(jù)鎖存到差分輸出。該解復(fù)用器

2023-07-11 09:32:57

HMC954LC4B是一款復(fù)用器

HMC954LC4B是一款2:1多路復(fù)用器,設(shè)計(jì)用于32 Gbps數(shù)據(jù)串行應(yīng)用。 多路復(fù)用器在輸入時(shí)鐘的上升沿鎖存兩個(gè)差分輸入。 該器件使用半速率時(shí)鐘的上升沿和下降沿來(lái)串行傳輸數(shù)據(jù)

2023-07-11 09:30:01

關(guān)于N76E003的輸入捕獲的一些知識(shí),不看后悔

的方式,支持雙邊沿,上升沿,下降沿,具體按照實(shí)際需求來(lái)

(5) 設(shè)置CAPCR,這個(gè)是關(guān)鍵的步驟,設(shè)置這個(gè)之后在發(fā)生了捕獲事件之后就會(huì)直接將定時(shí)器的值清0,重新開(kāi)始計(jì)時(shí),這樣的好處是我們完全可以不去

2023-06-25 08:42:33

N76E003開(kāi)啟外部中斷,持續(xù)進(jìn)入中斷后,程序就無(wú)法再進(jìn)入中斷怎么解決?

外部中斷配置的是兩個(gè)外部中斷的上升沿、下降沿都觸發(fā)

2023-06-15 06:16:02

ECSPI不是和標(biāo)準(zhǔn)的SPI重合嗎?

根據(jù) IMX6ULLRM,它讀取當(dāng)相位控制 (ECSPI_CONREG[PHA]) 位置位時(shí),發(fā)送數(shù)據(jù)將在 SCLK 的上升沿移出,接收數(shù)據(jù)在 SCLK 的下降沿鎖存。最高有效位在第一個(gè) SCLK

2023-06-08 09:44:27

西門(mén)子1200上升沿和下降沿的操作流程

通過(guò)上面的這個(gè)程序,我們就得到了上升沿信號(hào)和下降沿信號(hào)。比如說(shuō),當(dāng)形參“I_請(qǐng)求1”的實(shí)參”I0.0”從0變1時(shí),那么形參“上升沿信號(hào)”就變?yōu)榱?。此時(shí),我們就可以用這個(gè)形參=1的信號(hào)來(lái)做事情了。

2023-06-01 16:49:57 2846

2846

2846

2846

如何從ISR的上升沿讀取GPIO?

我在 GPIO_INTR_ANYEDGE 上配置了一個(gè) GPIO ISR。

我想在 ISR 中知道它是上升沿還是下降沿。

怎么做?

如果我只是在 ISR 中讀取 GPIO 狀態(tài),它幾乎總是 0,即使

2023-05-30 10:37:08

開(kāi)關(guān)電源MOSFET關(guān)斷緩沖電路

Q關(guān)斷,集電極電壓開(kāi)始上升到2Vdc,電容C限制集電極電壓的上升速度,并減小上升電壓和下降電流的重疊,減低開(kāi)關(guān)管Q的損耗。

2023-05-30 09:18:01 732

732

732

732

是否可以讓FSYNC數(shù)據(jù)在上升沿而不是下降沿觸發(fā)限定符?

31 位。我們計(jì)劃使用限定符來(lái)同步 32 位數(shù)據(jù)和 FSYNC。是否可以讓 FSYNC 數(shù)據(jù)在上升沿而不是下降沿觸發(fā)限定符?

2023-05-24 10:30:57

IMX8MN如果我們配置GPT在上升沿/下降沿觸發(fā)中斷,如何知道中斷是由下降沿還是上升沿觸發(fā)?

以獲得一個(gè)數(shù)組,其中包含每個(gè) 0 和 1 轉(zhuǎn)換的持續(xù)時(shí)間

我的想法是在輸入捕獲模式下使用 GPT 1,配置為觸發(fā)上升沿和下降沿的中斷,并在中斷中獲取位 (0/1) 的持續(xù)時(shí)間并將其存儲(chǔ)在數(shù)組中

2023-05-12 06:35:59

請(qǐng)問(wèn)verilog可以對(duì)同一個(gè)時(shí)鐘進(jìn)行上升沿和下降沿采樣嗎?

請(qǐng)問(wèn)verilog可以對(duì)同一個(gè)時(shí)鐘進(jìn)行上升沿和下降沿采樣嗎?

2023-05-10 11:11:12

在時(shí)序電路里如何利用一個(gè)信號(hào)的上升沿和下降沿采樣數(shù)據(jù)呢?

外部輸入一個(gè)周期信號(hào)和一個(gè)數(shù)據(jù),我要利用這個(gè)周期信號(hào)的上升沿和下降沿采樣數(shù)據(jù)。除了利用高頻時(shí)鐘去檢測(cè)周期信號(hào)的上升沿和下降沿變換外,還有什么方法?

2023-05-10 10:36:28

在時(shí)序電路里如何利用一個(gè)信號(hào)的上升沿和下降沿采樣數(shù)據(jù)呢?

外部輸入一個(gè)周期信號(hào)和一個(gè)數(shù)據(jù),我要利用這個(gè)周期信號(hào)的上升沿和下降沿采樣數(shù)據(jù)。除了利用高頻時(shí)鐘去檢測(cè)周期信號(hào)的上升沿和下降沿變換外,還有什么方法?

2023-05-10 10:35:59

是否有可能在不添加/使用FTM1模塊和其他通道的情況下為PWM的每個(gè)上升沿或下降沿束獲得中斷/回調(diào)?

我正在使用S32K32118 EVB和S32DS.3.5

通過(guò)S32 配置工具,我在 FTM0、CH0 上創(chuàng)建了一個(gè) PWM 波形。

我想知道是否有可能在不添加/使用 FTM1 模塊和其他通道的情況下為 PWM 的每個(gè)上升沿或下降沿(或至少在新周期開(kāi)始/結(jié)束時(shí))獲得中斷/回調(diào) 。

2023-05-04 08:27:26

安捷倫AFG3102波形發(fā)生器

長(zhǎng)達(dá)128K的任意波形。在脈沖波形上可以單獨(dú)設(shè)置上升沿和下降沿時(shí)間。可以將外部信號(hào)連接,并疊加到輸出信號(hào)中。雙通道型號(hào)輸出可生成兩個(gè)完全相同或截然不同的信號(hào)。所有

2023-04-18 10:05:02

CH32V103基礎(chǔ)教程9-輸入捕獲

捕獲可對(duì)輸入信號(hào)的上升沿、下降沿或者雙邊沿進(jìn)行捕獲,其捕獲原理為:當(dāng)發(fā)生并捕獲信號(hào)跳變沿之后,計(jì)數(shù)器(CNT)值將被鎖存到捕獲比較寄存器(CCR)中,將前后兩次捕獲到的CCR寄存器中的值相減,即可計(jì)算出頻率或者脈寬。如果捕獲脈寬時(shí)長(zhǎng)超過(guò)捕獲定時(shí)器的周期,會(huì)發(fā)生溢出,此時(shí)需要進(jìn)行額外處理。

2023-04-14 16:17:39

KEA8 KBI下降沿和上升沿問(wèn)題求解

我正在FRDM - KEAZ128 上開(kāi)發(fā)新代碼,我需要在下降沿和上升沿攔截單個(gè)引腳上的中斷,但從文檔來(lái)看,似乎只能使用下降沿或上升沿。它是否正確?如果沒(méi)有辦法在兩個(gè)邊緣設(shè)置 IRQ,唯一的其他方法是使用 ACMP 外圍設(shè)備或“更智能”的方法可用?

2023-03-23 07:53:32

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論