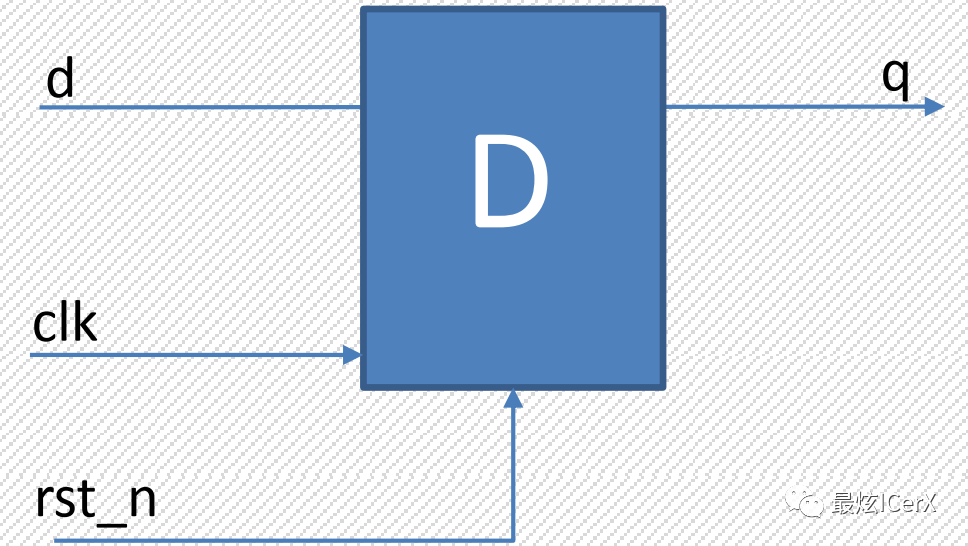

1、D觸發器及代碼

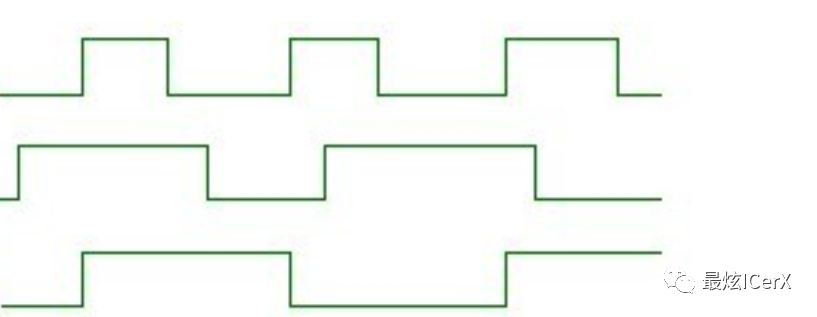

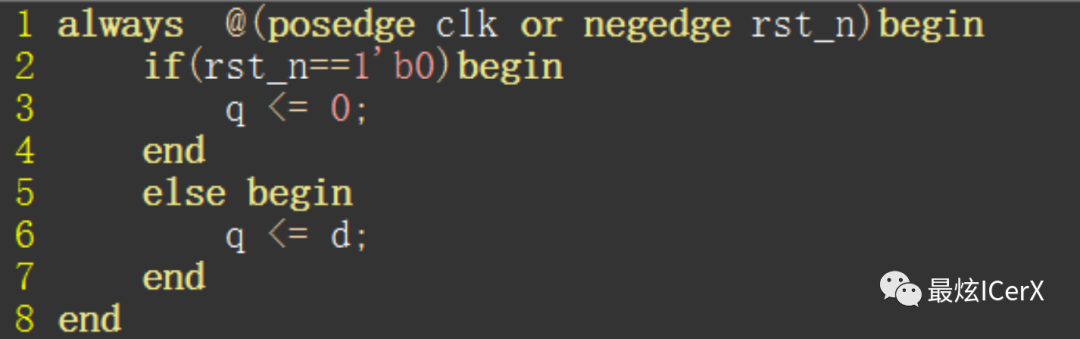

D觸發器結構如下圖所示,先有時鐘上升沿,然后才有D的值賦給Q,沒有上升沿Q值保持不變,時序邏輯在時鐘上升沿/下降沿后才變化

? ? ?

? ? ?

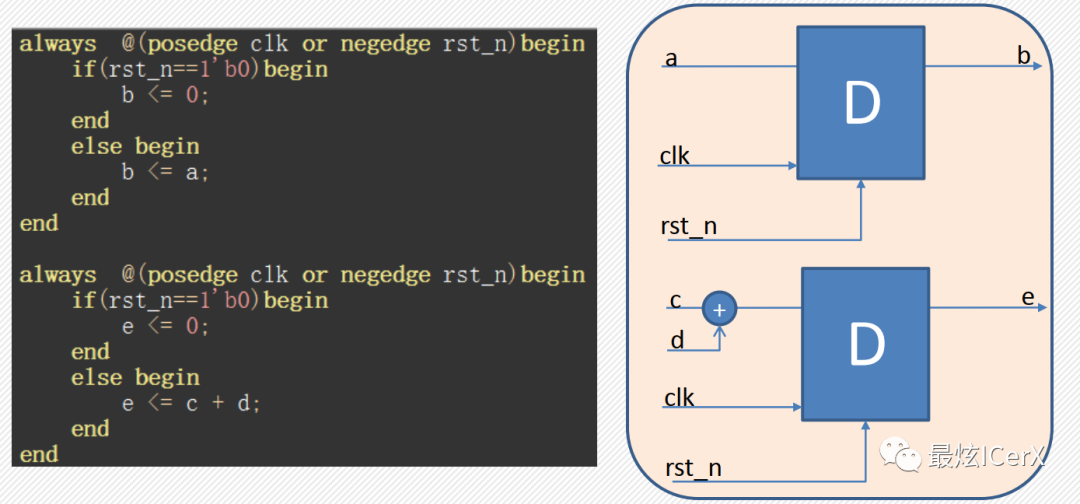

2、硬件設計思維

如下圖所示,一個always對應一個D觸發器,一個信號,always,模塊就是一個元器件

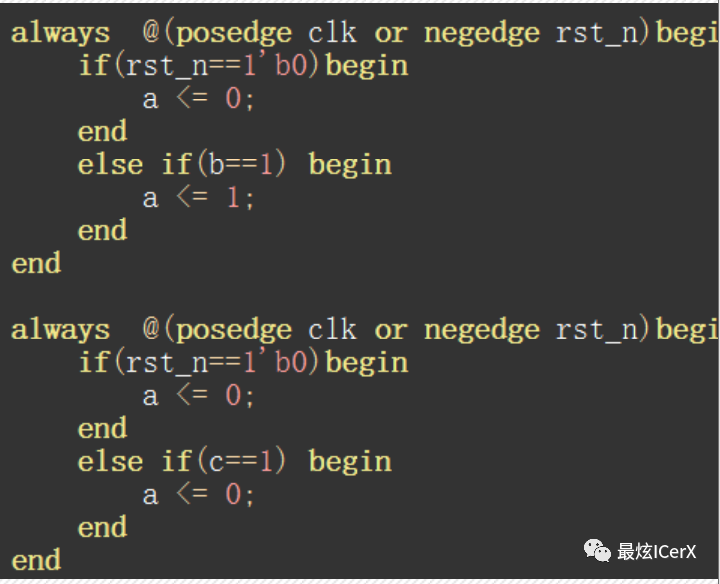

如下圖所示,一個信號不能在多個always中設計,一個信號在一個always

??

??

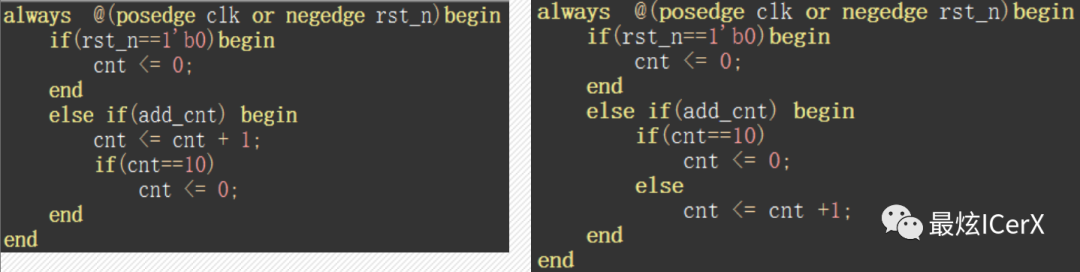

如下圖對比,左邊為軟件思維描述過程,右邊是硬件思維是描述功能,

硬件設計思路應逐個定義好每個信號/元器件的功能,然后連接,根據每個信號的功能畫波形,來實現最終目標

3、一個RTL用例設計

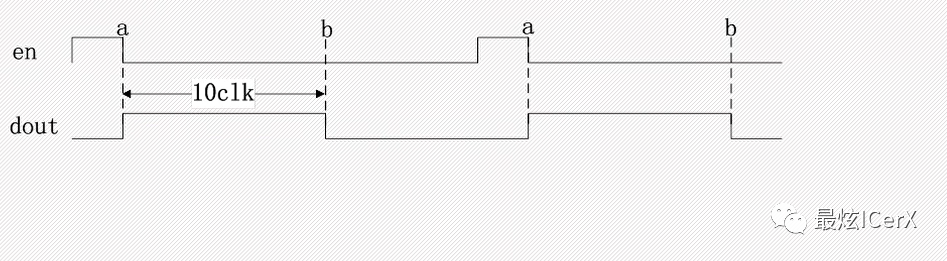

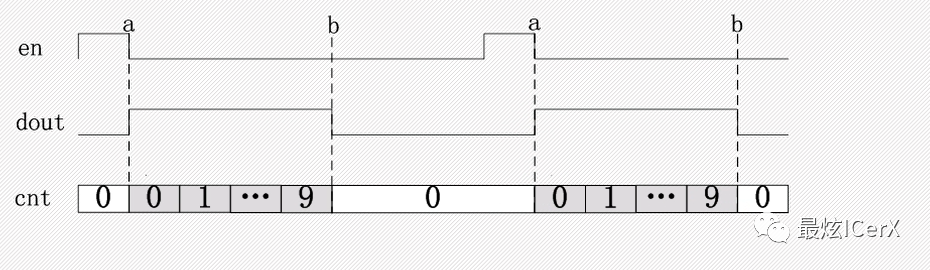

計數器用例,要求:當收到en后,dout產生一個寬度為10個時鐘周期的高電平脈沖,信號示意如下,這是一個計數器用例,硬件設計步驟分解如下

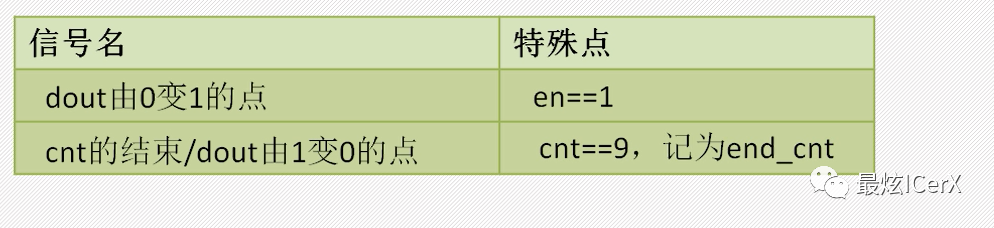

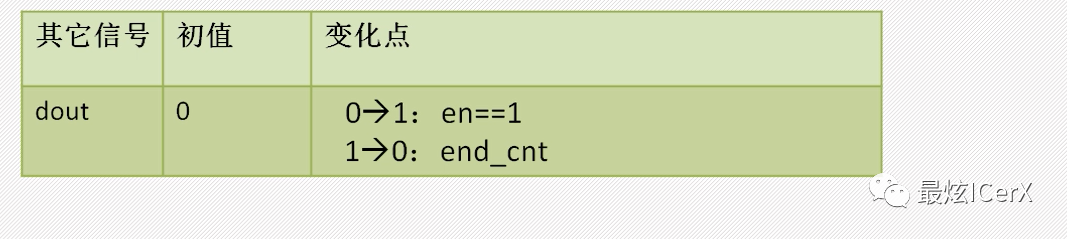

第一步明確功能,確定信號真值表。

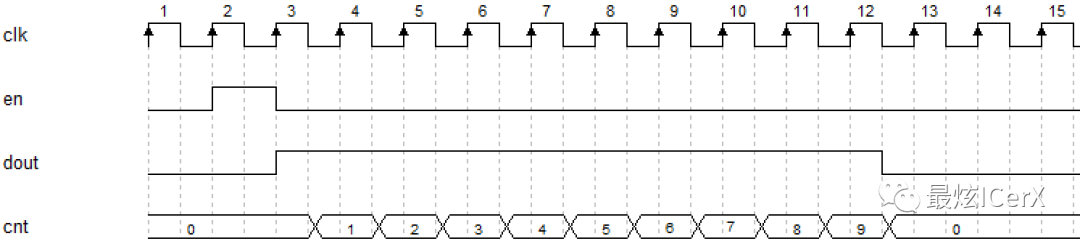

第二步畫出功能波形,通過Timegen繪制如下信號波形,詳細用法可閱讀軟件---TimeGen安裝與使用,本用例所有信號都是在時鐘上升沿過后進行判斷的,下圖en是在clk第三個上升沿時完成判斷,記住先有時鐘再有信號。

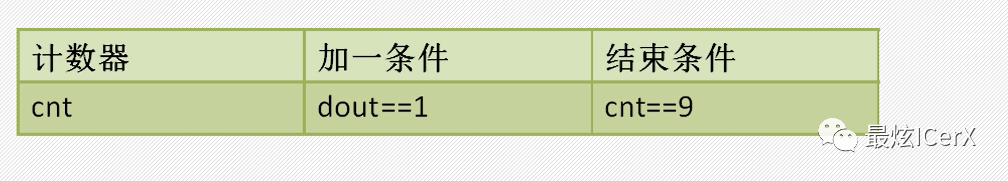

第三步明確計數器結構,本設計計數器默認都是從0開始計數

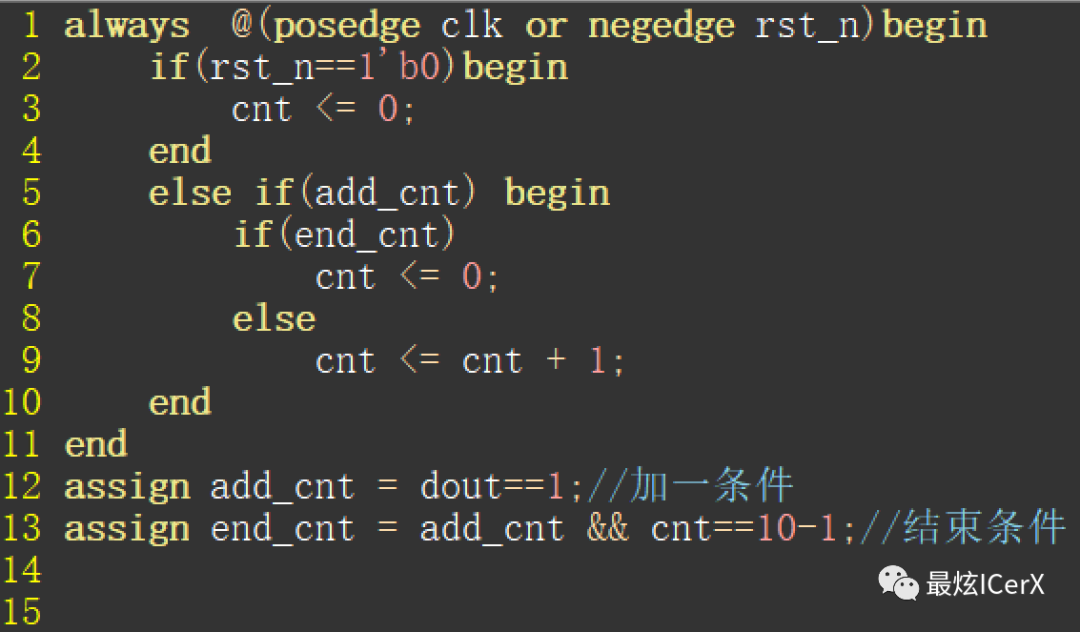

第四步明確計數器結構,確定設計中的加一及結束條件,代碼如下,下面代碼可作為計數器代碼通用模板

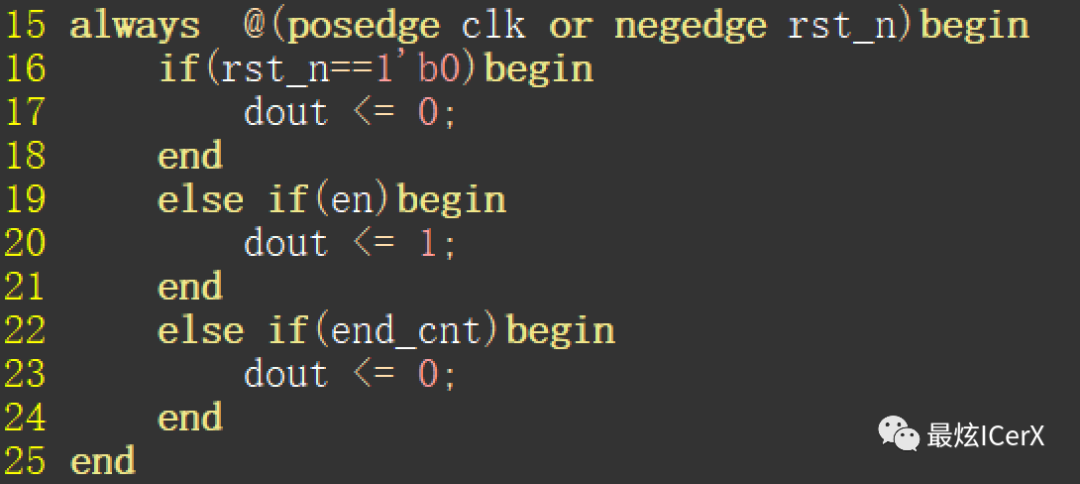

第五步定義特殊點,編寫輸出信號變化情況,如下代碼

第六步完整性檢查

第七步編寫計數器代碼,見上述計數器代碼

第八步功能代碼,見上述輸出信號dout代碼,補全其它代碼

總結設計,規范硬件設計思路,第一步-->第二步......,按照步驟實現,檢查設計過程。本設計中首先畫出信號波形,接著確定計數器結構,接著確定計數器加一與結束條件,接著確定輸出信號變低,變高時間點及條件,最后寫計數器代碼,輸出信號代碼,接口定義。接下來會繼續介紹Verilog設計規范及對應用例。

審核編輯:劉清

-

計數器

+關注

關注

32文章

2256瀏覽量

94715 -

RTL

+關注

關注

1文章

385瀏覽量

59853 -

D觸發器

+關注

關注

3文章

164瀏覽量

47961 -

時序邏輯電路

+關注

關注

2文章

94瀏覽量

16565 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8281

原文標題:RTL設計規范

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RTL8139C RTL8139C-LF RTL8139CL RTL8139CL-LF

RTL設計規范有哪些?一個RTL用例設計介紹

RTL設計規范有哪些?一個RTL用例設計介紹

評論