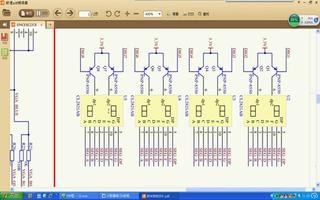

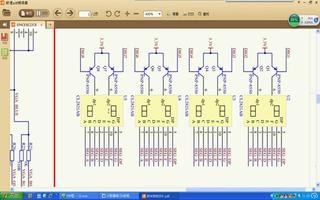

74161設計12進制計數器,1.74161為十六進制計數器,設計十二進制計數器時1片就可以滿足要求。2.新建BDF文件及保存工程同前篇。3.將所需要的元器件和引腳拖入區域內并完成連接,如圖1所示圖1十二進制計數器連接圖4.建立VWF文件,仿真后得到結果如圖2

2021-07-22 06:33:31

FSL總線IP核及其在MicroBlaze系統中的應用

2015-01-18 21:01:20

你好我正在嘗試將microblaze連接到一個新的custimized IP。我可以使用FSL總線嗎?我可以使用vivado連接它們嗎?我應該在IP HDL代碼和微網格中做什么樣的更改以及它們的接口?有什么文件可以幫助我?

2020-04-21 10:19:36

`光子計數探測器混合像素探測器,為您的實驗室精心準備PILATUS混合像素探測器的設計是X射線探測領域的一次革命性成果,其能夠實現最好的數據質量。該探測器將單光子計數和混合像素技術這兩項關鍵技術

2014-03-03 19:21:07

計數器及時序電路原理及實驗 一、實驗目的1、了解時序電路的經典設計方法(D觸發器、JK觸發器和一般邏輯門組成的時序邏輯電路)。 &

2009-10-10 11:47:02

使用計數器計數不成功,有個老師指導說“每次是能計數器, 計數器值會清零 "就說了這幾句,奈何我太菜了 無法理解怎么弄。有大神指導下如何實現計數操作

2020-05-31 22:35:28

計數器是什么?如何使用計數器?計數器有哪些應用呢?

2022-02-28 11:08:08

剛開始接觸Multisim,我用的是Multisim14,今天畫了一個電路圖 實現十進制計數器顯示的功能,但仿真是報錯 Transient time point calculation did not converge ,找不出原因,希望大家幫我找找錯在哪里了哈

2016-08-14 20:18:15

剛開始接觸Multisim,我用的是Multisim14,今天畫了一個電路圖 實現十進制計數器顯示的功能,但仿真是報錯 Transient time point calculation did not converge ,找不出原因,希望大家幫我找找錯在哪里了哈

2016-08-14 20:18:16

; 2、掌握中規模集成計數器的使用及功能測試方法 3、運用集成計數計構成1/N分頻器二、 實驗原理計數器是一個用以實現計數

2009-10-11 10:00:11

五十一進制計數器的仿真與設計。能否有大佬能給出原理圖,設計方案,個模塊功能。磕頭了

2019-03-02 16:28:38

目錄C51定時器計數器電路圖定時/計數器的結構和工作原理相關寄存器C51定時器計數器電路圖定時/計數器的結構和工作原理定時/計數器的實質是加1計數器(16位),由高8位和低8位兩個寄存器TH1

2022-01-24 07:04:15

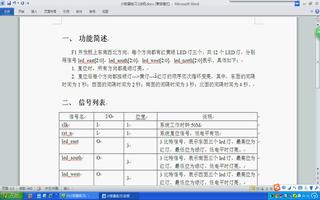

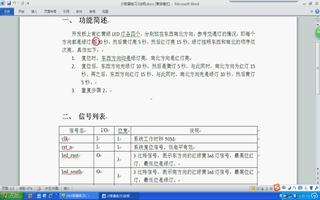

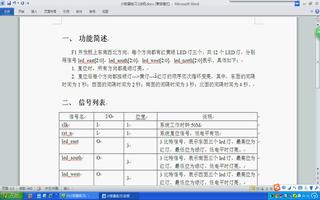

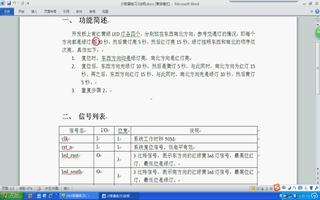

實驗目的1.1 計數器設計目的1) 每隔 1s,計數器增 1;能以數字形式顯示時間。2) 熟練掌握計數器的各個部分的結構。3) 計數器間的級聯。4) 不同芯片也可實現六十進制。1.2 計數器設計組成

2021-07-29 07:17:33

[url=]ISE中應用MicroBlaze軟核[/url]

2015-12-14 13:22:42

`自動門模擬(難度等級:★★)(1)設計任務采用計數器模塊控制實現模擬自動門的運行。(2)基本要求采用事件結構完成相應功能。采用圖片來模擬自動門的打開和關閉。指示燈顯示開門或關門的狀態。顯示進入

2019-12-27 21:34:06

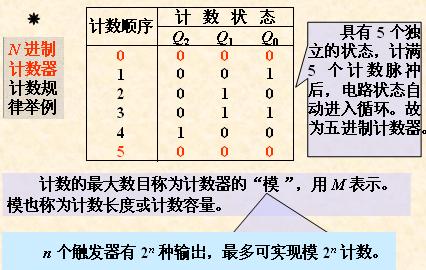

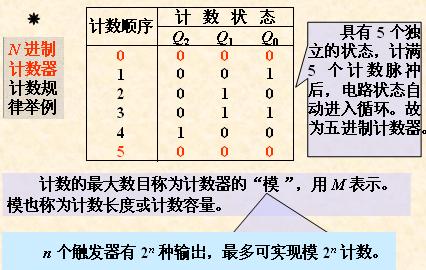

N進制計數器的實現 一、用集成計數器可以實現任意進制的計數器二、集成計數器控制功能的歸類三、集成計數器的級聯擴展四、復位法組成任意進制加法計數器五、置位法組成任意進制加法計數器六

2008-07-05 13:41:26

labview如何加一計數器的例子,實現單擊計數?

2017-02-15 14:42:25

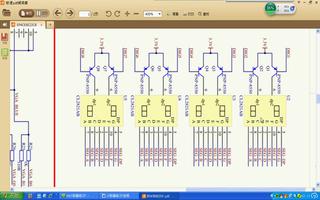

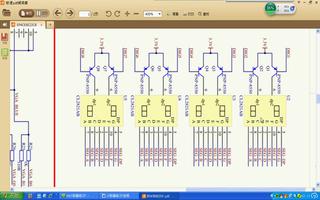

。這里實現了例化設計好的計數器IP核,且將其進行兩級級聯。分析綜合無誤后點擊RTL viewer可以看如圖5-15所示的原理圖。圖5-15 兩級級聯的計數器原理圖為了測試仿真編寫測試激勵文件,新建

2016-12-22 23:37:00

/*名稱:用計數器中斷實現 100 以內的按鍵計數 說明:本例用 T0 計數器中斷實現按鍵技術,由于計數寄存器初值為 1,因此 P3.4 引腳的每次負跳變都會觸發 T0 中斷,實現計數值累加

2012-02-24 09:36:02

Insrtction System Computer)優化結構和Harvard總線結構,廣泛適用于Spartan、Virtex和Artix等系列的FPGA。MicroBlaze軟核嵌入式處理器是高度可定制的IP核

2020-10-16 16:28:50

請問給位大神,只用觸發器和簡單的邏輯門怎樣設計一個同步清零的二十進制的計數器

2013-10-16 22:00:52

。這里實現了例化設計好的計數器IP核,且將其進行兩級級聯。分析綜合無誤后點擊RTL viewer可以看如圖5-15所示的原理圖。圖5-15 兩級級聯的計數器原理圖為了測試仿真編寫測試激勵文件,新建

2019-03-04 06:35:13

最近在看《現代操作系統》,他提到了時鐘維持實際時間,在每個時鐘滴答將計數器加1即可實現。但要注意位溢出(32位計數器),可以通過以下方法解決:使用64位計數器:缺點是這種方法使得計數器加一操作的代價很高,1s內維護很多次計數器。我不太懂紅色字體的意思

2018-05-04 11:36:41

單片機計數器計數怎么用匯編實現,最好能舉個例子,感激不盡~~~主要是中斷怎么應用

2011-04-28 10:08:19

1、實現一個24進制加法計數器的設計本實驗設計實現一個24進制的加法計數器,它由晶體振蕩器、分頻器、計數器和數碼管顯示器組成,圖6.1是該加法計數器的示意圖。晶體振蕩器產生穩定的50MHz的脈沖信號

2022-07-05 15:14:27

基于FPGA的嵌入式系統的開發工具包。本文介紹基于SoPC的波形發生器在EDK工具包下的設計與實現。本設計采用嵌入式軟處理器核 MicroBlaze以及自主編寫的包括實現DDS在內的多種IP Core

2009-06-25 08:12:37

UART內部可劃分為哪幾個模塊?這些模塊有什么功能?基于APB總線的UART接口軟核該如何去設計?

2021-06-18 08:20:15

本文的應用背景為某一工業測控系統,該系統采用FPGA實現測量數據的采集和控制信號的輸出,通過定制PCI接口IP實現一個32位目標設備的PCI總線接口轉換。PCI核選用AlteraPCI編譯器所包括

2018-12-04 10:35:21

大家好!我目前正在研究的項目需要一個計數器,該計數器具有基于兩個非周期時鐘/計數方向信號的增量或遞減其值的能力(與只需要與一個時鐘/計數方向對一起工作的通用計數器形成對比)。我可以想到幾種在ARM核

2019-10-25 12:47:24

定時/計數器實現功能:(1)定時功能:定時/計數器說明(最高單次計時時間是71毫秒=65535*1.085us,1.085us是機器周期):使用51定時/計數器步驟:定時/計算器控制寄存器:設置定時

2021-12-01 07:17:27

什么是定時/計數器呢?定時/計數器的模式有哪些?定時/計數器是怎樣去實現定時1ms的任務呢?

2022-01-21 07:26:54

定時器與計數器的操作是如何去實現的?定時器與計數器的結果是怎樣讀取得到的?

2022-01-19 06:46:09

怎么實現加減計數器?想要一個電路圖加上說明本人初學者 請大家多多指教

2015-03-08 20:19:38

怎么實現基于單片機和FPGA的多功能計數器的設計?

2021-05-14 06:57:15

目標:獲取一段時間內的單光子計數器的計數值。當前思路是:使用延遲脈沖信號發生器發送脈沖信號給數據采集卡PCIE-6374的Trigger端,使其觸發計數器進行計數。問題:怎樣設置DAQ助手?或者怎樣去學習設置?沒有百度到相關的方法,懇請大家幫助。

2020-12-25 20:02:01

嗨,大家好,我正在使用Vivado 2014.4有沒有辦法使用Vivado本身為Microblaze創建FSL接口?如果是,我可以使用此FSL將FIFO連接到MB嗎?請建議。謝謝你們,提前。謝謝&問候,專一

2020-04-06 17:25:00

處理器間通信和中斷方面仍需進一步的研究。本文在處理器間通信和中斷控制方面進行了深入的研究。MicroBlaze是一個被優化過的可以在Xilinx公司FPGA中運行的軟核處理器,可以和其他外設IP核一起完成

2021-03-16 07:44:35

所搭的IP軟核的通訊協議與總線支持的通訊協議(ICB)不同怎么轉換?

2023-08-17 07:05:35

求解大神,如何用基本邏輯門和觸發器實現6進制加法計數器等...還有12進制加法計數器

2012-11-29 18:40:22

計數器(Counter)由基本的計數單元和控制門所組成,是在數字系統中對脈沖的個數進行計數,以實現測量、計數和控制功能,且兼有分頻功能的儀器。計數器按進位制不同,分為二進制計數器和十進制計數器;按

2021-12-08 08:32:28

我已經搭建好了軟核microblaze,但是用sdk編程卻看不懂,請教大俠如何學習在sdk內編程?

2014-03-04 17:15:00

我要用計數器計數編碼器的脈沖,單片機的IO口不夠,但有還有SCI或SPI的總線接口!

2012-02-07 11:06:03

我們調用ip核生成一個4位計數器后想用該計數器模塊生成一個8位的計數器,這里就需要級聯兩個計數器這個是counter模塊:module counter ( cin, clock, cout, q

2021-11-11 07:41:25

頂層為原理圖的能顯示16進制減法計數器設計1.用VHDL設計一個二選一電路,并用ModelSim Simulator 仿真驗證。 要求該二選一電路能實現16進制數的兩位數據串行輸出(或稱動態輸出

2009-10-11 08:51:38

這里我們所講的開發板是CT107D,頻率計數器這一部分,比較容易。物理連接上,只需要把單片機開發版上的P34管腳和SIGNAL用跳線連接即可。下面,我們將直接進入代碼分析和頻率計數器的實現原理分析

2022-02-23 07:36:22

15-1.實現定時的方法15-2.定時器/計數器的結構和工作原理 15-3.定時器/計數器的控制15-4.定時器/計數器的工作方式 15-5.定時器/計數器應用 軟件定時軟件延時不占用硬

2009-03-23 12:17:51 48

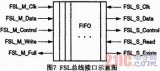

48 本文對 MicroBlaze 的幾種主要總線接口摘要進行比較,詳細分析、介紹FSL 總線的結構、特點、工作原理和配置方法。通過一個矢量漢字還原的應用實例,具體描述在FPGA片上系統設

2009-11-30 15:08:04 11

11 近紅外單光子探測器 SPD4近紅外單光子探測器SPD4是基于InGaAs雪崩光電二極管的超靈敏探測儀器。可以探測范圍覆蓋900 nm~1700 nm波段的光子,最高可達30%的量子效率,最低至1.0

2023-03-16 13:48:40

計數器的級連使用

一個十進制計數器只能顯示0~9十個數,為了擴大計數器范圍,常用多個十進制計數器級連使用。

2007-11-22 12:53:25 3379

3379

60進制計數器,由于24進制、60進制計數器均由集成計數器級聯構成,且都包含有基本的

2008-06-30 00:00:41 15784

15784

計數器

計數器的作用與分類

計數器(Counter)用于計算輸入脈沖個數,還常用于分頻、定時等。

2009-09-30 18:30:15 1414

1414

環形計數器和扭環形計數器

移位寄存器也可以構成計數器,稱為移位型計數器。它有兩種結構:環形計數器和扭環形計數器。

2010-01-12 14:07:46 9173

9173 什么是二進制計數器,二進制計數器原理是什么?

計數器是數字系統中用得較多的基本邏輯器件。它不僅能記錄輸入時鐘脈沖的個數,還可以實現

2010-03-08 13:16:34 30351

30351 計數器,計數器的工作原理是什么?

在數字系統中使用最多的時序電路是計數器。計數器不僅能用于對時鐘脈沖進行計數還可以用于分頻、定時,產生

2010-03-08 13:50:14 59934

59934 MicroBlaze 核是嵌入在Xilinx FPGA之中的屬于32位RISC Harvard架構軟處理器核。針對Xilinx MicroBlaze軟處理器的核間互連,實現多處理器核之間的快速通信的目的,采用了PLB和FSL總線混連的方法,

2011-07-20 17:22:21 68

68 所謂門光子計數器就是針對單自旋量子調控實驗研究中對單個光子探測的需求所研制的。光子計數IP核與Mieroblaze軟核之間通過FSL總線進行通訊,并且對FSL總線上的FIFO緩沖進行了深度擴充

2011-08-13 15:11:29 1411

1411

目的是利用嵌入在Xilinx FPGA中的MicroBlaze核實現基于AXI總線的雙核嵌入式系統設計以及共享實現LED燈的時控.

2012-03-09 14:17:01 91

91 計數器是常用的時序邏輯電路器件,文中介紹了以四位同步二進制集成計數器74LS161和異步二-五-十模值計數器74LS290為主要芯片,設計實現了任意模值計數器電路,并用Multisim軟件進行了

2013-07-26 11:38:41 134

134 計數器原理圖介紹。計數器原理圖介紹。計數器原理圖介紹

2015-12-25 09:37:05 14

14 集成計數器實現N進制計數集成計數器實現N進制計數集成計數器實現N進制計數

2016-06-08 14:28:43 0

0 計數是一種最簡單基本的運算,計數器就是實現這種運算的邏輯電路,計數器在數字系統中主要是對脈沖的個數進行計數,以實現測量、計數和控制的功能,同時兼有分頻功能,計數器是由基本的計數單元和一些控制門所組成

2017-09-25 10:13:37 8

8 AXI總線的MicroBlaze雙核SoPC系統設計

2017-10-31 08:54:44 8

8 集成計數器常見的是多位二進制計數器及十進制計數器,當需要實現其它進制計數器時,通常利用現有的集成計數器進行適當的連接而構成。對于當設計要求沒有限定計數器的狀態編碼時電路設計的靈活性問題已有文獻進行

2017-11-09 16:36:16 81

81 。系統采用的是一種基于MicroBlaze系統FSL總線的可擴展計數器設計架構,該架構能夠靈活的添加不同的計數功能,并通過統一的FSL總線和Microblaze CPU與PC通信。在該架構的基礎上實現了針對量子單自旋調控實驗中常用的計數模式。

2017-11-24 16:56:39 548

548

端,可以串接計數器使用。單片161可以實現16以內任意進制的加法計數功能。實現60進制加法計數器需要2片161,它們之間的連接方式又分同步和異步兩種。下面一起來看看怎么實現的。

2018-01-18 10:56:39 353099

353099

計數是一種最簡單基本的運算,計數器就是實現這種運算的邏輯電路,計數器在數字系統中主要是對脈沖的個數進行計數,以實現測量、計數和控制的功能,同時兼有分頻功能,計數器是由基本的計數單元和一些控制門所組成

2018-02-24 15:31:08 45454

45454 問題1:如何用Verilog實現這個計數器?針對上述功能的計數器,應該如何用Verilog實現?

2018-05-16 15:16:13 6102

6102

計數是一種最簡單基本的運算,計數器就是實現這種運算的邏輯電路,計數器在數字系統中主要是對脈沖的個數進行計數,以實現測量、計數和控制的功能,同時兼有分頻功能,計數器是由基本的計數單元和一些控制門所組成

2019-01-24 14:35:40 63341

63341 計數器

2019-09-03 06:11:00 3556

3556

計數器

2019-09-03 06:10:00 2856

2856

計數器

2019-09-03 06:09:00 2484

2484

計數器

2019-09-03 06:08:00 1809

1809

計數器

2019-09-03 06:06:00 2556

2556

計數器

2019-09-03 06:03:00 2329

2329

計數器

2019-09-03 06:02:00 1921

1921

計數器

2019-09-03 06:01:00 2799

2799

計數器

2019-09-02 06:10:00 5240

5240

計數器的工作是通過每個時鐘脈沖將計數器的內容提前一個計數來計數。當被時鐘輸入激活時推進其數字或狀態序列的計數器被稱為以“遞增計數”模式操作。同樣,當被時鐘輸入激活時減少其數字或狀態序列的計數器被稱為以“倒計數”模式操作。在UP和DOWN模式下工作的計數器稱為雙向計數器。

2019-06-23 07:47:00 12721

12721

什么是計數器芯片? 一般來說,計數器芯片就是用來實現計數這種最基礎運算的邏輯電路,計數器在數字系統中主要是對脈沖的個數進行計數,以實現測量、計數和控制的功能,同時兼有分頻功能,計數器是由基本的計數

2021-07-13 14:09:37 12366

12366 計數器(Counter)由基本的計數單元和控制門所組成,是在數字系統中對脈沖的個數進行計數,以實現測量、計數和控制功能,且兼有分頻功能的儀器。計數器按進位制不同,分為二進制計數器和十進制計數器

2021-11-25 18:06:07 32

32 扭環形計數器,約翰遜計數器,每次狀態變化時僅有一個觸發器發生翻轉,譯碼不存在競爭冒險,在n(n≥3)位計數器中,使用2n個狀態,有2^n-2n個狀態未使用;

2022-06-15 09:27:57 1971

1971 本方案是一個基于 FPGA ?的十進制計數器。共陽極 7 段顯示器上的 0 到 9 十進制計數器,硬件在 Xilinx Spartan 6 FPGA 板上實現。

2022-12-20 14:52:25 2

2 S7-1200的計數器為IEC計數器,用戶程序中可以使用的計數器數量僅受CPU的存儲器容量限制。

2023-01-29 09:31:56 6124

6124 在數字電子產品中,計數器是由一系列觸發器組成的時序邏輯電路。顧名思義,計數器用于計算輸入在負或正邊沿轉換中出現的次數。根據觸發觸發器的方式,計數器可以分為兩類:同步計數器和異步計數器。了解這兩種計數器的工作原理以及它們之間的區別。

2023-03-25 17:31:07 18646

18646

同步計數器和異步計數器是兩種常見的數據結構,它們都用于控制對共享資源的訪問。它們的主要作用是實現多個線程之間的同步和并發控制。盡管它們都被用于同步的目的,但它們有很多不同的特點和用例。 同步計數器

2023-12-15 10:49:43 512

512 計數器是一種被廣泛應用于各個領域的實用工具,在我們的日常生活中隨處可見。無論是進行時間統計,協助工作任務的完成,還是用于科學研究和編程技術,在各個領域都起到了重要的作用。本文將詳細介紹計數器

2024-02-03 10:04:14 588

588

電子發燒友App

電子發燒友App

評論