計(jì)數(shù)器在數(shù)字系統(tǒng)中主要是對(duì)脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測(cè)量、計(jì)數(shù)和控制的功能,同時(shí)兼有分頻功能.

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1629文章

21744瀏覽量

603611 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2256瀏覽量

94607 -

測(cè)量

+關(guān)注

關(guān)注

10文章

4864瀏覽量

111351

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

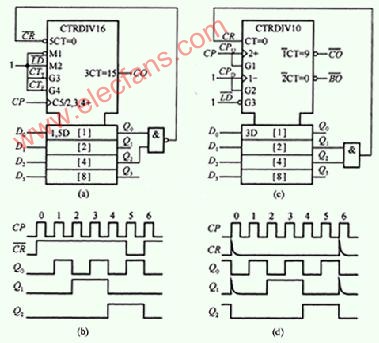

利用復(fù)位端構(gòu)成的模6計(jì)數(shù)器電路

利用復(fù)位端構(gòu)成的模6計(jì)數(shù)器電路

利用集成計(jì)數(shù)器的預(yù)置端和復(fù)位端可以構(gòu)成任意模計(jì)數(shù)器。下圖所示依次是利用

發(fā)表于 01-12 13:54

?5567次閱讀

基于FPGA的PWM計(jì)數(shù)器改進(jìn)設(shè)計(jì)

簡(jiǎn)單改變FPGA計(jì)數(shù)器規(guī)格使作為DAC功能PWM計(jì)數(shù)器的紋波降低。

發(fā)表于 04-06 11:11

?1981次閱讀

集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)

集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)集成計(jì)數(shù)器

發(fā)表于 06-08 14:28

?0次下載

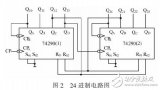

24進(jìn)制計(jì)數(shù)器的設(shè)計(jì)

集成計(jì)數(shù)器常見(jiàn)的是多位二進(jìn)制計(jì)數(shù)器及十進(jìn)制計(jì)數(shù)器,當(dāng)需要實(shí)現(xiàn)其它進(jìn)制計(jì)數(shù)器時(shí),通常利用現(xiàn)有的集成

發(fā)表于 11-09 16:36

?81次下載

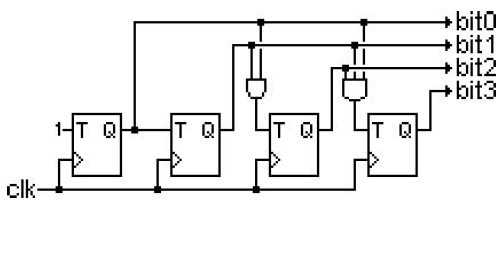

FPGA基礎(chǔ)應(yīng)用計(jì)數(shù)器的實(shí)例詳細(xì)說(shuō)明

該計(jì)數(shù)器從0 計(jì)數(shù)到4294967295,然后回滾到0 并重新開(kāi)始計(jì)數(shù)。它只需要FPGA 上一點(diǎn)點(diǎn)的資源就可以迅速完成計(jì)數(shù),這都多虧了

發(fā)表于 12-11 17:26

?12次下載

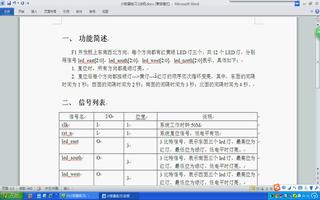

基于FPGA的十進(jìn)制計(jì)數(shù)器

本方案是一個(gè)基于 FPGA ?的十進(jìn)制計(jì)數(shù)器。共陽(yáng)極 7 段顯示器上的 0 到 9 十進(jìn)制計(jì)數(shù)器,硬件在 Xilinx Spartan 6 FPGA

發(fā)表于 12-20 14:52

?2次下載

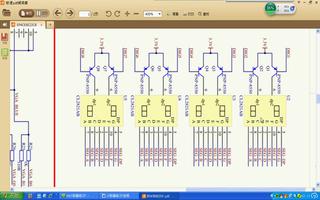

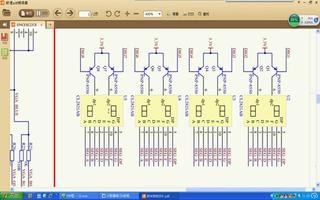

利用FPGA實(shí)現(xiàn)計(jì)數(shù)器的設(shè)計(jì)(1)

利用FPGA實(shí)現(xiàn)計(jì)數(shù)器的設(shè)計(jì)(1)

評(píng)論