靜態(tài)時(shí)序分析包括建立時(shí)間分析和保持時(shí)間分析。建立時(shí)間設(shè)置不正確可以通過(guò)降低芯片工作頻率解決,保持時(shí)間設(shè)置不正確芯片無(wú)法正常工作。

2022-08-22 10:38:24 3289

3289 建立時(shí)間(setup time)和保持時(shí)間(hold time)是時(shí)序分析中最重要的概念之一,深入理解建立時(shí)間和保持時(shí)間是進(jìn)行時(shí)序分析的基礎(chǔ)。

2023-06-21 10:44:01 884

884

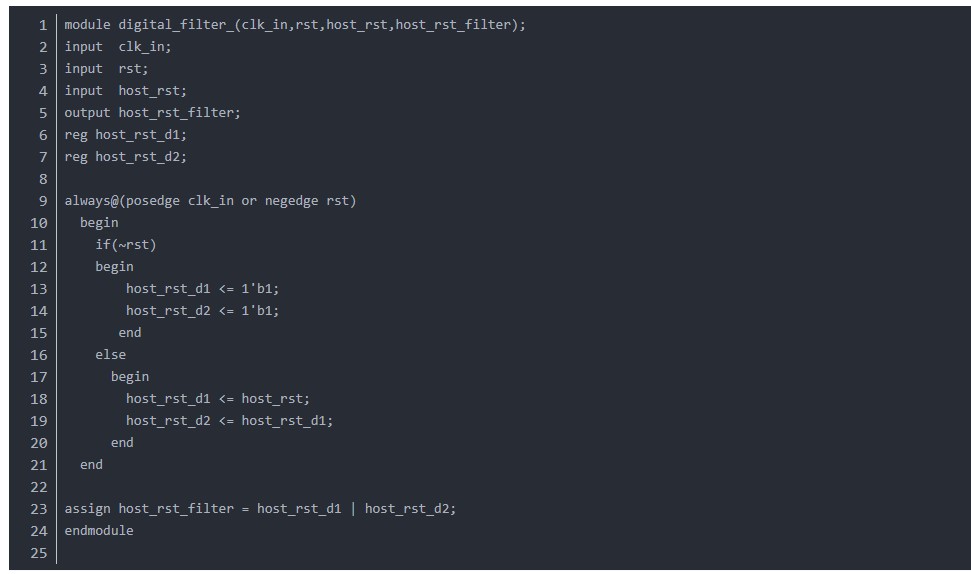

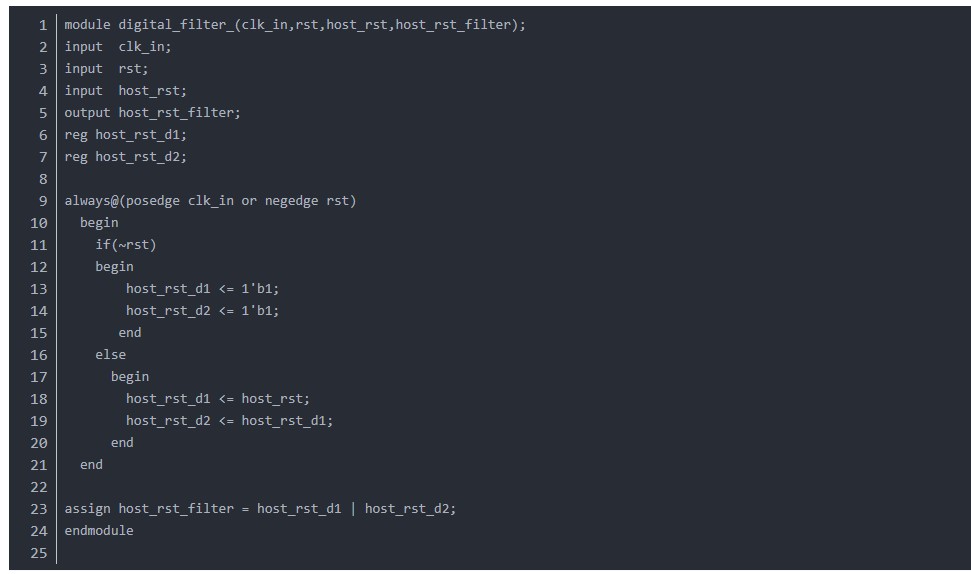

今天有個(gè)小伙伴遇到一個(gè)問(wèn)題,就是在vivado里面綜合后看到的建立時(shí)間和保持時(shí)間裕量都是inf,我們來(lái)看看怎么解決這個(gè)問(wèn)題。

2023-07-30 10:26:02 649

649

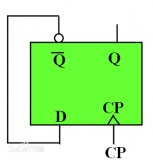

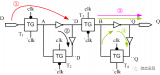

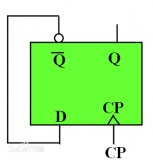

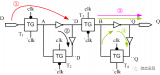

我理解這個(gè)D觸發(fā)正常運(yùn)轉(zhuǎn)要滿足四個(gè)約束,第一個(gè)是建立時(shí)間,第二個(gè)是保持時(shí)間,第三個(gè)是對(duì)于最后一個(gè)傳輸門(mén)的關(guān)斷時(shí)間的控制,第四個(gè)是[時(shí)鐘周期]() 約束。

2023-12-04 15:44:02 352

352

筆試真題:1、什么是建立時(shí)間、保持時(shí)間,如果setup time violation或者hold time violation 應(yīng)該怎么做?(10分)答案:建立時(shí)間:是指在觸發(fā)器的時(shí)鐘信號(hào)采樣邊沿

2018-11-26 14:39:04

Setup/Hold Time ProblemConclusionIf the Setup/Hold time error happen on the Input Register (Example

2008-09-11 09:23:30

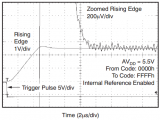

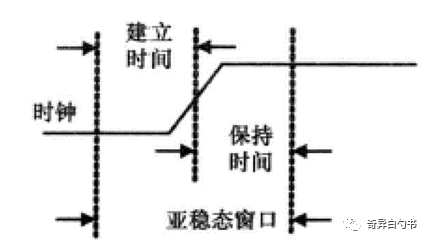

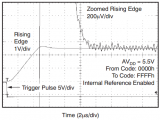

如圖,建立時(shí)間和保持時(shí)間都是針對(duì)的時(shí)鐘沿,如圖所示,時(shí)鐘沿有一個(gè)上升的過(guò)程,圖中虛線與clk上升沿的交點(diǎn)是什么?幅值的50%?還是低電平(低于2.5V)往高電平(高于2.5V)跳轉(zhuǎn)的那個(gè)點(diǎn)?

2018-11-29 00:20:02

本帖最后由 虎子哥 于 2015-3-12 21:24 編輯

建立時(shí)間(Setup Time):是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果建立時(shí)間不夠,數(shù)據(jù)將不能在這個(gè)時(shí)鐘

2015-03-10 23:19:03

ADC時(shí)延和建立時(shí)間的區(qū)別是什么?以及ADC時(shí)延和建立時(shí)間將會(huì)如何影響您的應(yīng)用電路?

2021-04-12 07:19:18

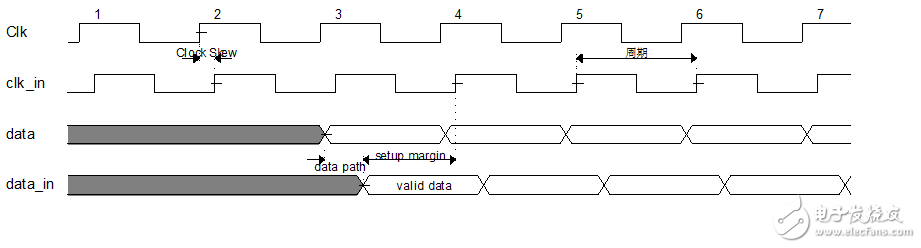

建立時(shí)間和保持時(shí)間本文節(jié)選自特權(quán)同學(xué)的圖書(shū)《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 在這個(gè)波形中,我們看到clk_r3的前后

2015-07-17 12:02:10

FPGA設(shè)計(jì)中的時(shí)序分析及異步設(shè)計(jì)注意事項(xiàng)建立時(shí)間(setup time):是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果建立時(shí)間不夠,數(shù)據(jù)將不能在這個(gè)時(shí)鐘上升沿被打入觸發(fā)器;保持

2009-12-07 10:14:33

幾天前量測(cè)了下intel 南橋發(fā)出到一個(gè)電源控制器的I2C信號(hào),發(fā)現(xiàn)數(shù)據(jù)建立時(shí)間(hold time)只有150ns左右,I2C協(xié)議里面所說(shuō)至少300ns,這個(gè)問(wèn)題該怎么解決啊 求大神指導(dǎo)建立時(shí)間有

2013-12-08 00:38:24

I2C的 ip核總線中保持時(shí)間hold是不是決定了SDA數(shù)據(jù)在SCL低電平的哪個(gè)時(shí)候開(kāi)始變化的,保持時(shí)間hold是不是可以幾乎不用,只要建立時(shí)間setup

2015-12-07 14:34:09

PLL jitter 對(duì)建立時(shí)間和保持時(shí)間有什么樣的影響?哪位大神給解答下

2015-10-30 11:16:30

簡(jiǎn)單的來(lái)分析一下數(shù)據(jù)的建立時(shí)間和保持時(shí)間應(yīng)該滿足怎樣的關(guān)系才能保證被時(shí)鐘lcd_clk穩(wěn)定的鎖存到ADV7123芯片中。首先,我們需要來(lái)看看這個(gè)實(shí)例的時(shí)鐘launch edge和latch edge

2019-04-10 06:33:34

在為ad7610選擇一個(gè)單電源的驅(qū)動(dòng)放大器,手冊(cè)中推薦的ad8021是雙電源,建立時(shí)間參數(shù)為:Settling Time to 0.01% VO = 1 V step, RL = 500 Ω 23

2023-11-17 06:22:37

的 setup-time 和hold-time 是正值還是負(fù)值,為什么?問(wèn)題 a:建立時(shí)間:觸發(fā)器在時(shí)鐘沿來(lái)到前,其數(shù)據(jù)輸入端的數(shù)據(jù)必須保持不變的時(shí)間;保持時(shí)間:觸發(fā)器在時(shí)鐘沿來(lái)到后,其數(shù)據(jù)輸入端的數(shù)據(jù)必須保持不變的時(shí)間

2012-03-15 10:41:40

Multicycle =4,那么其建立時(shí)間向后延伸4個(gè)周期,Setup time=(24ns-2ns)=22nsMulticycle Hold=1,同樣這里檢查兩個(gè)保持時(shí)間關(guān)系Hold Check1:空心箭頭

2015-03-17 17:43:52

我想了解 time() 命令。

每次我啟動(dòng) esp8266 模塊時(shí),我都必須使用 time.setup() 命令。

有沒(méi)有其他方法即使停電也只能保持運(yùn)行時(shí)間?

謝謝

2023-06-01 13:10:43

什么是同步邏輯和異步邏輯?同步電路和異步電路的區(qū)別在哪?為什么觸發(fā)器要滿足建立時(shí)間和保持時(shí)間?

2021-09-28 08:51:33

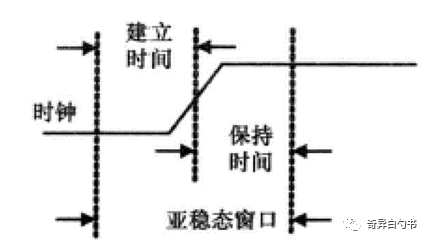

什么是同步邏輯和異步邏輯?同步電路和異步電路的區(qū)別在哪?為什么觸發(fā)器要滿足建立時(shí)間和保持時(shí)間?什么是亞穩(wěn)態(tài)?為什么兩級(jí)觸發(fā)器可以防止亞穩(wěn)態(tài)傳播?

2021-08-09 06:14:00

什么叫建立時(shí)間,保持時(shí)間,和恢復(fù)時(shí)間

2017-04-08 16:52:35

setip 建立時(shí)間 holdup 保持時(shí)間 建立時(shí)間是指, 時(shí)鐘邊緣前,數(shù)據(jù)信號(hào)保持不變的的時(shí)間,保持時(shí)間 是指時(shí)鐘跳變邊緣數(shù)據(jù)信號(hào)數(shù)據(jù)信號(hào)保持不變的時(shí)間。

2019-08-02 11:54:27

保持穩(wěn)定不變的時(shí)間。輸入數(shù)據(jù)信號(hào)應(yīng)提前時(shí)鐘上升沿(如上升沿有效)T 時(shí)間到達(dá)芯片,這個(gè) T就是建立時(shí)間通常所說(shuō)的 SetupTime。如不滿足 Setup Time,這個(gè)數(shù)據(jù)就不能被這一時(shí)鐘打入觸發(fā)器,只有在下一個(gè)時(shí)鐘上升沿到來(lái)時(shí),數(shù)據(jù)才能被打入觸發(fā)器。保持時(shí)間(Hold Time)是

2021-12-21 07:39:55

,建立時(shí)間為10ns。 AFTER約束基本上表示從輸入時(shí)鐘到達(dá)輸入引腳的時(shí)間到數(shù)據(jù)熄滅的時(shí)間的最大時(shí)間,時(shí)鐘的上升沿可以是約束中指定的時(shí)間的最大值。這看起來(lái)不是設(shè)置時(shí)間。它也不是時(shí)候。如何使用此AFTER

2019-04-09 13:16:27

。這種方法把準(zhǔn)確性和精確度建立在波形生成器和采樣保持電路的相對(duì)速度上。 受測(cè)器件的步進(jìn)輸入 本文中,建立時(shí)間是指使用某個(gè)理想步進(jìn)輸入,到受測(cè)器件(DUT)進(jìn)入并維持在某個(gè)規(guī)定誤差范圍(終值對(duì)稱)內(nèi)

2012-07-30 17:36:20

關(guān)于數(shù)字IC的建立時(shí)間以及保持時(shí)間你想知道的都在這

2021-09-18 07:24:40

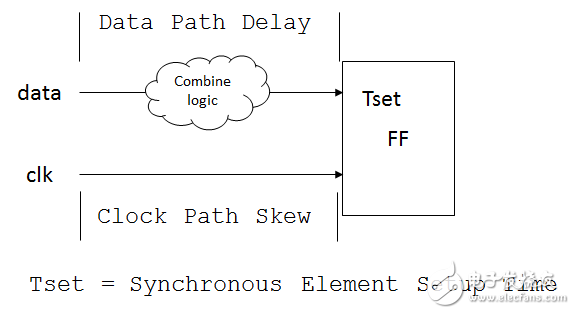

之差,即Tskew=Tc2d-Tc2s。 二、建立時(shí)間和保持時(shí)間建立時(shí)間(Setup Time)常用Tsu表示,指的是在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)和使能信號(hào)穩(wěn)定不變的時(shí)間,如果建立時(shí)間不夠

2018-04-03 11:19:08

如果DFF的hold時(shí)間不滿足,通常可以通過(guò)降低時(shí)鐘運(yùn)行速度來(lái)解決( )A 是B 不是解析:建立時(shí)間:即時(shí)鐘有效沿來(lái)臨之前數(shù)據(jù)需要保持穩(wěn)定的最小周期,以便數(shù)據(jù)在隨時(shí)鐘信號(hào)采樣時(shí)是準(zhǔn)確的。保持時(shí)間

2021-07-29 06:10:52

一個(gè)較高水平。關(guān)鍵詞:FPGA 數(shù)字電路 時(shí)序 時(shí)延路徑 建立時(shí)間 保持時(shí)間1 數(shù)字電路設(shè)計(jì)中的幾個(gè)基本概念:1.1 建立時(shí)間和保持時(shí)間:建立時(shí)間(setup time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿

2012-10-26 17:24:58

建立時(shí)間測(cè)量的采樣保持方法測(cè)試裝置存在哪些局限性?

2021-04-09 06:08:05

怎么解釋setup time和hold time的定義和在時(shí)鐘信號(hào)延遲時(shí)的變化呢?

2023-05-10 11:46:59

建立時(shí)間(Setup Time)是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)之前,數(shù)據(jù)保持穩(wěn)定不變的時(shí)間。 輸入信號(hào)應(yīng)該提前時(shí)鐘上升沿(如上升沿有效)Tsu時(shí)間到達(dá)芯片,這個(gè) Tsu就是建立時(shí)間。如果不滿足建立時(shí)間

2021-07-26 07:36:01

請(qǐng)問(wèn),對(duì)于觸發(fā)器的時(shí)鐘信號(hào),建立時(shí)間和保持時(shí)間有要求嗎?剛看到一個(gè)門(mén)控時(shí)鐘產(chǎn)生毛刺的反例,(如下圖)想到了這個(gè)問(wèn)題。若此時(shí)鐘信號(hào)毛刺極小,有沒(méi)有可能被觸發(fā)器忽略呢?為什么呢?如果有可能小到什么程度會(huì)被忽略呢?

2012-01-27 18:44:58

有句話這樣寫(xiě)道“純粹的建立時(shí)間Tsu是15.951ns'中扣除launch edge time(5ns)和network delay(3.081),所以是7.87ns。而同樣地,可以得到保持時(shí)間Th

2013-10-22 22:26:12

我做了一個(gè)PID用來(lái)控制圓盤(pán)的角度,現(xiàn)在需要顯示圓盤(pán)轉(zhuǎn)到45度和120度時(shí)的 rise time(上升時(shí)間)和settling time(建立時(shí)間)。但不知道怎么弄,求大神們指導(dǎo)

2013-12-02 17:34:54

本帖最后由 gk320830 于 2015-3-5 18:27 編輯

setup/hold time 是測(cè)試芯片對(duì)輸入信號(hào)和時(shí)鐘信號(hào)之間的時(shí)間要求。建立時(shí)間是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間。保持時(shí)間是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以后,數(shù)據(jù)穩(wěn)定不變的時(shí)間。

2014-04-12 16:40:18

在AD80370的datasheet里面有SYSREF± Setup and Hold Timing 這個(gè)時(shí)序圖,但是為什么圖中標(biāo)示的holdup time是負(fù)值,如果這樣的話那device

2018-10-09 16:09:24

在為ad7610選擇一個(gè)單電源的驅(qū)動(dòng)放大器,手冊(cè)中推薦的ad8021是雙電源,建立時(shí)間參數(shù)為:Settling Time to 0.01% VO = 1 V step, RL = 500 Ω 23

2018-08-01 09:25:24

16444_[。只有降低SPI頻率到20MHz才ok。(2)問(wèn)題分析:通過(guò)示波器測(cè)量,發(fā)現(xiàn)DM9051的cs建立時(shí)間和保持時(shí)間很緊張,其它信號(hào)質(zhì)量和時(shí)序ok,需要增加cs的建立時(shí)間和保持時(shí)間來(lái)試試。(3

2023-02-15 06:55:16

T2max,最小為T(mén)2min。問(wèn),觸發(fā)器D2的建立時(shí)間T3和保持時(shí)間應(yīng)滿足什么條件

2019-09-09 17:19:55

Setup/Hold Time Problem ,Correct Waveform

We fix the simulation error. But do we really fix

2008-09-11 09:23:29 20

20 該文簡(jiǎn)要討論了環(huán)路性能(建立時(shí)間,相位噪聲和雜散信號(hào))和環(huán)路參數(shù)(帶寬,相位裕度等)的相互關(guān)系。提出并分析了一種自適應(yīng)的具有快速建立時(shí)間的鎖相環(huán)結(jié)構(gòu)及其關(guān)鍵模塊(鑒相

2010-04-23 08:33:53 20

20 If the Setup/Hold time error happen on the Input Register (Example 1)

–run the Setup/Hold

2010-07-19 16:40:12 31

31 基本概念:線與邏輯、鎖存器、緩沖器、建立時(shí)間、緩沖時(shí)間

基本概念:線與邏輯、鎖存器、緩沖器、建立時(shí)間、緩沖時(shí)間

標(biāo)簽/分類(lèi):

2007-08-21 15:17:27 1169

1169 什么是Setup 和Holdup時(shí)間?

a) 什么是Setup 和Holdup時(shí)間? 建立時(shí)間(setup time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果建立時(shí)間不夠,數(shù)

2007-09-11 22:53:41 10559

10559 a) 什么是Setup 和Holdup時(shí)間? 建立時(shí)間(setup time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果建立時(shí)間不夠,數(shù)據(jù)將不能在這個(gè)時(shí)鐘上升沿被打入

2007-09-11 22:53:59 14690

14690 a) 什么是Setup 和Holdup時(shí)間? 建立時(shí)間(setup time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果建立時(shí)間不夠,數(shù)據(jù)將不能在這個(gè)時(shí)鐘上升沿

2007-09-11 22:54:34 5806

5806 a) 什么是Setup 和Holdup時(shí)間? 建立時(shí)間(setup time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果建立時(shí)間不夠,數(shù)據(jù)將不能在這個(gè)時(shí)鐘上升沿

2007-09-11 22:55:37 9628

9628 時(shí)延和建立時(shí)間setup在ADC電路中的區(qū)別:對(duì)于大多數(shù) ADC 用戶來(lái)說(shuō),“時(shí)延”和“建立時(shí)間”這兩個(gè)術(shù)語(yǔ)有時(shí)可以互換。但對(duì)于 ADC 設(shè)計(jì)人員而言,他們非常清楚

2007-11-22 23:33:07 1430

1430 什么是TIME

英文原義:Time Server Protocol

中文釋義:標(biāo)準(zhǔn)時(shí)間服務(wù)器協(xié)議

注 解:這

2010-02-23 11:25:19 864

864 下面是一些基本的數(shù)字電路知識(shí)問(wèn)題,請(qǐng)簡(jiǎn)要回答之。 (1) 什么是Setup 和Hold 時(shí)間? 答:Setup/Hold Time 用于測(cè)試芯片對(duì)輸入信號(hào)和時(shí)鐘信號(hào)之間的時(shí)間要求。建立時(shí)間(Setup Time)是指觸發(fā)器

2011-07-26 17:35:59 5319

5319 FPGA設(shè)計(jì)一個(gè)很重要的設(shè)計(jì)是時(shí)序設(shè)計(jì),而時(shí)序設(shè)計(jì)的實(shí)質(zhì)就是滿足每一個(gè)觸發(fā)器的建立(Setup)/保持(Hold)時(shí)間的要求。 建立時(shí)間(Setup Time):是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)

2011-10-28 10:21:26 92

92 今天,我們將介紹兩種相關(guān)的動(dòng)態(tài)參數(shù) — 壓擺率與建立時(shí)間。如欲了解更多有關(guān)靜態(tài)和動(dòng)態(tài)參數(shù)的不同之處,敬請(qǐng)參閱本文。

2018-07-10 16:14:00 5294

5294

報(bào)告中關(guān)于time borrowing的處理方式。 下面的時(shí)鐘信號(hào)周期為10,占空比為50%: 同時(shí)我們引入一個(gè)簡(jiǎn)單的電路,如下所示: 為了更容易理解,我們假設(shè)每個(gè)觸發(fā)器的建立時(shí)間和保持時(shí)間均為“0”。 同樣假設(shè)時(shí)鐘偏移和時(shí)鐘延遲也為“0”。 F1在時(shí)刻0得到數(shù)據(jù),F(xiàn)2在時(shí)刻10對(duì)數(shù)據(jù)進(jìn)行了采樣。

2018-10-02 07:54:03 748

748 建立時(shí)間和保持時(shí)間建立時(shí)間( setup time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果建立時(shí)間不夠,數(shù)據(jù)將不能在這個(gè)時(shí)鐘上升沿被打入觸發(fā)器

2020-09-08 17:28:08 4

4 1、下面是一些基本的數(shù)字電路知識(shí)問(wèn)題,請(qǐng)簡(jiǎn)要回答之。 (1)什么是 Setup和 Hold 時(shí)間?答:Setup/Hold Time 用于測(cè)試芯片對(duì)輸入信號(hào)和時(shí)鐘信號(hào)之間的時(shí)間要求。建立時(shí)間

2020-09-16 17:12:38 19506

19506

1、什么是Setup 和Holdup時(shí)間? 答:Setup/hold time 是測(cè)試芯片對(duì)輸入信號(hào)和時(shí)鐘信號(hào)之間的時(shí)間要求。 建立時(shí)間是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間。輸入

2020-09-28 11:18:31 2161

2161 建立時(shí)間(Setup Time) 和保持時(shí)間( Hold time )。建立時(shí)間是指在時(shí)鐘邊沿前,數(shù)據(jù)信號(hào)需要保持不變的時(shí)間。保持時(shí)間是指時(shí)鐘跳變邊沿后數(shù)據(jù)信號(hào)需要保持不變的時(shí)間。見(jiàn)圖1。如果不滿足

2020-10-27 16:26:00 11

11 建立時(shí)間(setup time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果建立時(shí)間不夠,數(shù)據(jù)將不能在這個(gè)時(shí)鐘上升沿被打入觸發(fā)器;保持時(shí)間(hold time)是指在觸發(fā)器的時(shí)鐘

2021-01-13 17:00:29 19

19 本篇仿真介紹放大器的建立時(shí)間,也稱為上升時(shí)間。它是高速放大電路、或在SARADC驅(qū)動(dòng)電路設(shè)計(jì)時(shí),需要謹(jǐn)慎評(píng)估的參數(shù)。

2021-02-15 16:37:00 5258

5258

答:Setup/Hold Time 用于測(cè)試芯片對(duì)輸入信號(hào)和時(shí)鐘信號(hào)之間的時(shí)間要求。建立時(shí)間(Setup Time)是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)能夠保持穩(wěn) 定不變的時(shí)間。輸入數(shù)據(jù)信號(hào)應(yīng)提

2021-02-23 08:00:00 6

6 AN-359:運(yùn)算放大器的建立時(shí)間

2021-04-29 15:28:46 3

3 Setup/hold time 是測(cè)試芯片對(duì)輸入信號(hào)和時(shí)鐘信號(hào)之間的時(shí)間要求。

2021-06-21 15:13:35 10524

10524

1、什么是Setup 和Holdup時(shí)間? 答:Setup/hold time 是測(cè)試芯片對(duì)輸入信號(hào)和時(shí)鐘信號(hào)之間的時(shí)間要求。 建立時(shí)間是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間。輸入

2021-11-09 11:37:14 1041

1041 TAS Address Setup time 地址設(shè)置時(shí)間TAH Address Hold time 地址保持時(shí)間TDSW Data Setup Time 數(shù)據(jù)設(shè)置時(shí)間

2022-01-14 09:28:18 10

10 時(shí)間裕量包括建立時(shí)間裕量和保持時(shí)間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。什么意思呢?即保持最低要求的建立時(shí)間或保持時(shí)間所多出的時(shí)間,那么“裕量”越多,意味著時(shí)序約束越寬松。

2022-08-04 17:45:04 657

657 做數(shù)字電路設(shè)計(jì)的可能都見(jiàn)過(guò)圖一所示的setup和hold時(shí)間檢查,從圖中可以明顯看出,setup time檢查下一個(gè)沿,而hold time檢查同一個(gè)沿。那么這是為什么呢 ?

2022-11-21 10:30:30 2717

2717 在Place Design之后再去看Hold Time,如果此時(shí)Hold Time的違例比較小(比如-0.05ns),還是不需要理會(huì)的

2023-01-11 09:05:41 2397

2397 時(shí)間裕量包括建立時(shí)間裕量和保持時(shí)間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。

2023-02-06 11:06:03 256

256 平常我們編寫(xiě)程序的時(shí)候用到最多的指令也許就是定時(shí)器指令了,有時(shí)候我們需要通過(guò)人機(jī)界面修改定時(shí)器的設(shè)定時(shí)間。但是許多人機(jī)界面不支持西門(mén)子S5 TIME時(shí)間格式。怎么辦呢?我們可以通過(guò)西門(mén)子庫(kù)文件系統(tǒng)

2023-03-16 17:18:39 1885

1885

運(yùn)算放大器建立時(shí)間是保證數(shù)據(jù)采集系統(tǒng)性能的關(guān)鍵參數(shù)。為了實(shí)現(xiàn)精確的數(shù)據(jù)采集,運(yùn)算放大器輸出必須在A/D轉(zhuǎn)換器能夠準(zhǔn)確數(shù)字化數(shù)據(jù)之前建立。然而,建立時(shí)間通常不是一個(gè)容易測(cè)量的參數(shù)。

2023-06-17 10:37:54 368

368

??本文主要介紹了建立時(shí)間和保持時(shí)間。

2023-06-21 14:38:26 1081

1081

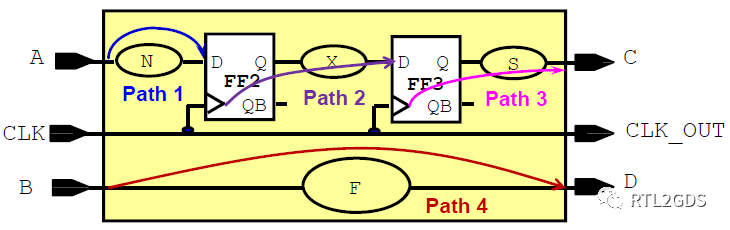

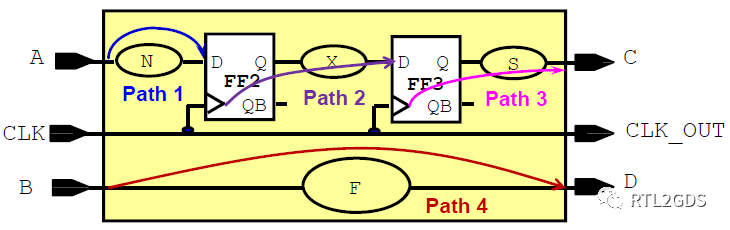

Delay值是多少才算合格呢?這一篇開(kāi)始講解路徑(Path)的概念,以及衡量Path Delay是否合格的標(biāo)準(zhǔn)----建立時(shí)間(setup time)和保持時(shí)間(hold time)。

2023-06-27 14:12:15 492

492

在時(shí)序電路設(shè)計(jì)中,建立時(shí)間/保持時(shí)間可以說(shuō)是出現(xiàn)頻率最高的幾個(gè)詞之一了,人們對(duì)其定義已經(jīng)耳熟能詳,對(duì)涉及其的計(jì)算(比如檢查時(shí)序是否正確,計(jì)算最大頻率等)網(wǎng)上也有很多。

2023-06-27 15:43:55 4597

4597

在后仿真過(guò)程中經(jīng)常會(huì)遇到關(guān)于setup和hold violation的問(wèn)題,但是關(guān)于setup和hold time的產(chǎn)生原因和由來(lái)很多人還比較朦朧,為此本文通過(guò)解剖一個(gè)邊沿觸發(fā)器簡(jiǎn)要說(shuō)明setup和hold產(chǎn)生原因。

2023-07-04 09:32:46 709

709

保持時(shí)間:在時(shí)鐘上升沿之后數(shù)據(jù)保持穩(wěn)定的時(shí)間。

2023-07-04 14:21:24 462

462 建立時(shí)間和保持時(shí)間是SOC設(shè)計(jì)中的兩個(gè)重要概念。它們都與時(shí)序分析有關(guān),是確保芯片正常工作的關(guān)鍵因素。

2023-08-23 09:44:55 390

390 信號(hào)經(jīng)過(guò)傳輸線到達(dá)接收端之后,就牽涉到建立時(shí)間和保持時(shí)間這兩個(gè)時(shí)序參數(shù),它們表征了時(shí)鐘邊沿觸發(fā)前后數(shù)據(jù)需要在鎖存器的輸入持續(xù)時(shí)間,是接收器本身的特性。簡(jiǎn)而言之,時(shí)鐘邊沿觸發(fā)前,要求數(shù)據(jù)必須存在一段時(shí)間,這就是器件需要的建立時(shí)間;

2023-09-04 15:16:19 392

392

亞穩(wěn)態(tài)(Metastability)是由于輸入信號(hào)違反了觸發(fā)器的建立時(shí)間(Setup time)或保持時(shí)間(Hold time)而產(chǎn)生的。建立時(shí)間是指在時(shí)鐘上升沿到來(lái)前的一段時(shí)間,數(shù)據(jù)信號(hào)就要

2023-09-19 09:27:49 360

360

在時(shí)鐘的上升沿之前,輸入信號(hào)需要穩(wěn)定在有效的數(shù)據(jù)值上的最小時(shí)間間隔。Hold時(shí)間指的是在時(shí)鐘的上升沿之后,輸入信號(hào)需要保持在有效的數(shù)據(jù)值上的最小時(shí)間間隔。這兩個(gè)時(shí)間要求是保證數(shù)據(jù)在電路中的正確傳輸和處理的關(guān)鍵。 首先,讓我們更深入地了解一下Setup時(shí)間

2023-11-17 14:11:35 935

935 文件提到兩種setup/hold測(cè)量方式:10% push-up和pass/fail,按照TSMC說(shuō)法,前者會(huì)更樂(lè)觀一些,因此如果是采用前者(10% push-up)的測(cè)量方式得到建立時(shí)間和保持時(shí)間,需要十份小心時(shí)序裕量是否足夠,最好人為添加margin。

2023-12-05 11:19:38 696

696

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論