介紹了基于Zynq平臺(tái)實(shí)現(xiàn)的JPEG圖像壓縮系統(tǒng)。該系統(tǒng)利用Zynq片上AXI總線實(shí)現(xiàn)了ARM與FPGA核間高吞吐率的數(shù)據(jù)交互操作,并結(jié)合了ARM和FPGA在嵌入式系統(tǒng)開發(fā)中各自的優(yōu)勢(shì),對(duì)軟硬件功能的實(shí)現(xiàn)進(jìn)行了明確的劃分。通過具體的實(shí)驗(yàn)測(cè)試,本系統(tǒng)的通用性及高效性得到了驗(yàn)證,并且該系統(tǒng)可方便地移植到不同的實(shí)際應(yīng)用中。

引言

隨著多媒體技術(shù)以及通信技術(shù)的迅猛發(fā)展,高質(zhì)量數(shù)字圖像的應(yīng)用越來越廣泛,然而未經(jīng)壓縮的數(shù)字圖像的數(shù)據(jù)量非常大,勢(shì)必會(huì)給圖像的存儲(chǔ)和傳輸都帶來很大的困難,因此對(duì)數(shù)字圖像的有效壓縮是不可或缺的。在現(xiàn)有圖像壓縮編碼技術(shù)中,靜態(tài)圖像壓縮編碼標(biāo)準(zhǔn)JPEG以其顯著的壓縮效率、較低的圖像質(zhì)量損失以及較低的實(shí)現(xiàn)復(fù)雜度得到了廣泛應(yīng)用,是常用的國(guó)際標(biāo)準(zhǔn)。

JPEG靜態(tài)圖像壓縮標(biāo)準(zhǔn)于1991年由聯(lián)合圖像專家組JPEG(Joint Picture Expert Group)制定[1]。發(fā)展至今,JPEG圖像壓縮系統(tǒng)在各大通用處理器平臺(tái)上的軟件實(shí)現(xiàn)早已成熟,但由于這些算法的實(shí)現(xiàn)需要大量系統(tǒng)資源(內(nèi)存、浮點(diǎn)運(yùn)算)的消耗,很難直接移植到資源有限的嵌入式平臺(tái)中。為了實(shí)現(xiàn)JPEG圖像壓縮在嵌入式平臺(tái)中的應(yīng)用,不少學(xué)者對(duì)JPEG編碼算法進(jìn)行了優(yōu)化,并在ARM微控制器、高性能DSP中進(jìn)行了實(shí)現(xiàn)[24]。由于圖像質(zhì)量及其對(duì)處理實(shí)時(shí)性要求的不斷提高,一些學(xué)者提出了采用FPGA并行硬件來實(shí)現(xiàn)JPEG圖像壓縮算法的解決方案[5],且取得了不錯(cuò)的效果。

若使用ARM微控制器進(jìn)行開發(fā),軟件方法的實(shí)現(xiàn)受限于指令的串行執(zhí)行,處理速度不會(huì)太快,且存在計(jì)算性能不足等問題。而使用高性能DSP進(jìn)行實(shí)現(xiàn)時(shí),雖然DSP內(nèi)部有專門的結(jié)構(gòu)加速實(shí)現(xiàn)數(shù)字信號(hào)處理,但存在開發(fā)復(fù)雜、可移植性不強(qiáng)等問題,而且由于是串行指令執(zhí)行系統(tǒng),仍存在處理速度上的局限。針對(duì)單純使用FPGA進(jìn)行開發(fā)時(shí),雖然硬件并行計(jì)算的優(yōu)勢(shì)能滿足圖像編碼算法處理性能上的需求,但在圖像數(shù)據(jù)的采集(如USB攝像頭)以及數(shù)據(jù)傳輸通信(如網(wǎng)絡(luò)傳輸)方面,相較嵌入式CPU而言,存在開發(fā)難度大、復(fù)雜度高、資源消耗多等問題,不利于系統(tǒng)通用平臺(tái)化實(shí)現(xiàn)。要實(shí)現(xiàn)完整通用的圖像壓縮系統(tǒng),可以采用ARM和FPGA軟硬件協(xié)同設(shè)計(jì)的方式來實(shí)現(xiàn)整個(gè)系統(tǒng)平臺(tái),ARM處理器完成數(shù)字圖像的采集以及壓縮后數(shù)據(jù)的傳輸,F(xiàn)PGA作為協(xié)處理器,通過高速并行計(jì)算完成JPEG編碼算法的硬件實(shí)現(xiàn)。

針對(duì)ARM和FPGA這種異構(gòu)多核的協(xié)同開發(fā),核間通信速率通常是系統(tǒng)設(shè)計(jì)的限制所在,但目前單芯片上集成ARM和FPGA的技術(shù)已經(jīng)很成熟,如Xilinx公司2011年推出的Zynq7000系列芯片[6],片內(nèi)高性能通信總線很好地解決了核間通信速率這一瓶頸。本文采用搭載有XC7Z020CLG484芯片的ZedBoard平臺(tái)完整地實(shí)現(xiàn)了JPEG圖像壓縮系統(tǒng),在利用FPGA并行處理優(yōu)勢(shì)加速實(shí)現(xiàn)JPEG編碼算法的同時(shí),ARM部分便捷地實(shí)現(xiàn)了圖像數(shù)據(jù)的采集、簡(jiǎn)單的預(yù)處理,以及壓縮后數(shù)據(jù)的傳輸?shù)裙δ堋?/p>

1系統(tǒng)整體實(shí)現(xiàn)結(jié)構(gòu)

系統(tǒng)平臺(tái)按照處理流程主要分為3個(gè)部分:圖像數(shù)據(jù)獲取、圖像編碼處理以及壓縮后的數(shù)據(jù)傳輸。本系統(tǒng)的整體實(shí)現(xiàn)結(jié)構(gòu)如圖1所示。

?

圖1 系統(tǒng)實(shí)現(xiàn)結(jié)構(gòu)圖

? ? ? ?

圖像數(shù)據(jù)獲取部分主要目的是采集需要壓縮處理的圖像數(shù)據(jù),包括圖1中的傳輸通信模塊和圖像數(shù)據(jù)采集模塊。本系統(tǒng)平臺(tái)提供兩種實(shí)現(xiàn)方式:一種面向?qū)嶋H圖像傳輸應(yīng)用,通過在嵌入式硬件平臺(tái)中直接連接數(shù)字圖像傳感器來獲取圖像數(shù)據(jù)進(jìn)行處理;另一種則面向圖像處理算法的調(diào)試驗(yàn)證,由PC機(jī)通過以太網(wǎng)或串口發(fā)送特定的圖像數(shù)據(jù)到嵌入式平臺(tái)中進(jìn)行圖像處理算法的驗(yàn)證。這兩種圖像數(shù)據(jù)采集方式均由ARM部分編寫相應(yīng)的驅(qū)動(dòng)程序進(jìn)行實(shí)現(xiàn)。

圖像編碼處理部分是該系統(tǒng)平臺(tái)的核心,包括圖1中的預(yù)處理模塊和圖像JPEG編碼模塊。這部分是基于Baseline JPEG算法實(shí)現(xiàn)的[7],主要包括圖像的色彩空間變換、排序、二維離散余弦變換(2DDCT)、量化、Z字掃描和熵編碼等模塊,圖像經(jīng)該算法處理后即可得到壓縮數(shù)據(jù)。該部分由ARM和FPGA協(xié)同處理實(shí)現(xiàn)。

壓縮后數(shù)據(jù)傳輸部分是指將壓縮后的數(shù)據(jù)由嵌入式硬件平臺(tái)通過圖1中的傳輸通信模塊發(fā)送至PC機(jī)端,完成圖像的解碼顯示。對(duì)于串口發(fā)送這一方案,由于傳輸速度慢,只適用于圖像處理算法的驗(yàn)證,要實(shí)現(xiàn)PC機(jī)端圖像的實(shí)時(shí)顯示則需要通過以太網(wǎng)傳輸。該部分的具體實(shí)現(xiàn)在ARM端進(jìn)行。

其中針對(duì)圖像數(shù)據(jù)獲取和壓縮后數(shù)據(jù)傳輸這兩部分在ARM端的軟件實(shí)現(xiàn),本系統(tǒng)在Zynq7000 SoC的ARM CortexA9雙核中移植了Ubuntu Linux操作系統(tǒng),其具備大量可利用的開源函數(shù)庫(kù)資源,極大地方便了圖像傳感器驅(qū)動(dòng)和以太網(wǎng)通信的實(shí)現(xiàn)。

2 Baseline JPEG編碼單元的設(shè)計(jì)與實(shí)現(xiàn)

本系統(tǒng)是在ZedBoard平臺(tái)上實(shí)現(xiàn)的,圖像數(shù)據(jù)的采集由ARM端完成,要實(shí)現(xiàn)JPEG編碼算法在FPGA中的硬件加速,F(xiàn)PGA需要與ARM進(jìn)行通信從而獲取到需要壓縮處理的圖像數(shù)據(jù)。系統(tǒng)中ARM與FPGA核間通信采用的是Zynq7000片內(nèi)的高性能通信總線AXI_HP,通過DMA的形式進(jìn)行數(shù)據(jù)傳輸,AXI_HP總線最高位寬為64位,理論通信帶寬最高可達(dá)1200 MB/s。

由于Baseline JPEG編碼是使用以DCT為基礎(chǔ)的順序編碼工作方式,在編碼過程中,先將原圖像分割成8×8的數(shù)據(jù)塊(如果是彩色圖像,需先進(jìn)行色彩空間的變換),圖像子塊按照一定的掃描順序依次輸入,對(duì)每一個(gè)8×8尺寸圖像子塊使用二維離散余弦變換去除圖像數(shù)據(jù)在空間上的相關(guān)性,然后根據(jù)指定的量化表進(jìn)行數(shù)據(jù)的量化處理,減少數(shù)據(jù)大小,再對(duì)數(shù)據(jù)進(jìn)行Z字掃描,便于數(shù)據(jù)編碼,接著根據(jù)指定的熵編碼表進(jìn)行編碼,減小數(shù)據(jù)編碼長(zhǎng)度,最終得到壓縮圖像的編碼數(shù)據(jù)。為了充分發(fā)揮AXI_HP總線最高64 位傳輸位寬以及FPGA并行處理等特性,本模塊將簡(jiǎn)單的圖像預(yù)處理部分在ARM部分進(jìn)行實(shí)現(xiàn),而2DDCT、量化、Z字掃描、熵編碼等部分則在FPGA部分進(jìn)行硬件加速實(shí)現(xiàn)。

2.1ARM部分軟件的設(shè)計(jì)

圖像壓縮編碼部分在ARM端的軟件實(shí)現(xiàn)主要是完成圖像預(yù)處理的功能,具體包含色彩空間的變換以及圖像數(shù)據(jù)的排序兩個(gè)部分。

2.1.1色彩空間變換

JPEG是針對(duì)連續(xù)色調(diào)(灰度和彩色)靜止圖像壓縮編碼的標(biāo)準(zhǔn),由彩色圖像傳感器獲取到的圖像通常是由RGB(即紅綠藍(lán))三種顏色分量組成,彩色圖像進(jìn)行JPEG壓縮前需要進(jìn)行色彩空間的轉(zhuǎn)換,通常轉(zhuǎn)換為YCrCb空間,包含一個(gè)亮度分量和兩個(gè)色度分量,由灰度圖像傳感器獲取的灰度圖像只有單一亮度分量,不需要轉(zhuǎn)換。

RGB與YCrCb空間轉(zhuǎn)換關(guān)系如下:

?

在進(jìn)行2DDCT前,需要將圖像像素值轉(zhuǎn)換為有符號(hào)數(shù),即將幅值減去128,所以使用式(1)進(jìn)行色彩空間變換時(shí),得到的每個(gè)分量值還需減去128以轉(zhuǎn)換為有符號(hào)數(shù)。這些轉(zhuǎn)換含有浮點(diǎn)運(yùn)算,為提高處理效率,在ARM端軟件實(shí)現(xiàn)時(shí)可將各浮點(diǎn)運(yùn)算的結(jié)果制成表格,進(jìn)行色彩空間轉(zhuǎn)換時(shí)通過查表的方式實(shí)現(xiàn),節(jié)省了浮點(diǎn)運(yùn)算占用的處理時(shí)間。

彩色圖像的壓縮處理是將色彩空間變換后得到的Y、Cr、Cb三個(gè)分量按照灰度圖像(單一Y分量)的壓縮方法分別進(jìn)行壓縮。本文中主要以Y分量(灰度圖像)的壓縮為例進(jìn)行介紹,其他分量的處理方法類似。

2.1.2圖像數(shù)據(jù)排序

JPEG壓縮編碼是以8×8數(shù)據(jù)塊為基本單元進(jìn)行編碼,一幅圖像中所有圖像子塊是以從左到右、自上往下的順序進(jìn)行處理的。本系統(tǒng)在ARM端完成色彩空間的轉(zhuǎn)換得到亮度值后,先對(duì)圖像數(shù)據(jù)按照處理順序進(jìn)行了重新排列,再通過64 位寬的AXI_HP總線將數(shù)據(jù)傳輸給FPGA端進(jìn)行后續(xù)處理。通過這樣的設(shè)計(jì),F(xiàn)PGA端獲取到重新排列后的數(shù)據(jù)后,便可以直接進(jìn)行以8×8數(shù)據(jù)塊為基本單元的壓縮處理流水實(shí)現(xiàn),無(wú)需涉及到圖像數(shù)據(jù)的存儲(chǔ)等待時(shí)間,可減少總體處理時(shí)間。

2.2FPGA部分軟件的設(shè)計(jì)

本系統(tǒng)中在FPGA部分主要是完成對(duì)預(yù)處理后數(shù)據(jù)的壓縮編碼,具體包含2DDCT、量化、Z字掃描以及熵編碼4個(gè)模塊。

2.2.12DDCT

對(duì)于2DDCT(二維離散余弦變換)的實(shí)現(xiàn),本文采用行列分解快速算法,先對(duì)8×8圖像子塊的所有行完成一維離散余弦變換(1DDCT),再對(duì)變換結(jié)果的每一列進(jìn)行一維離散余弦變換,就可以得到2DDCT的結(jié)果。該部分具體實(shí)現(xiàn)框圖如圖2所示,針對(duì)AXI_HP總線最高64 位傳輸位寬的特性,即可實(shí)現(xiàn)8個(gè)像素的圖像數(shù)據(jù)并行輸入,其中行列處理的轉(zhuǎn)換是通過控制8個(gè)64位輸入、8位輸出FIFO的讀寫進(jìn)行實(shí)現(xiàn)的。1DDCT模塊采用Leoffler DCT算法進(jìn)行優(yōu)化實(shí)現(xiàn)[8],大量減少了乘法器資源的消耗,其中涉及到的浮點(diǎn)小數(shù)乘法運(yùn)算采用定點(diǎn)整數(shù)乘法進(jìn)行替代。

?

圖2 2D_DCT實(shí)現(xiàn)框圖

2.2.2量化

量化過程就是將經(jīng)過二維離散余弦變換后得到的頻域系數(shù),根據(jù)重要性的不同,分別除以不同的量化步長(zhǎng),從而得到量化結(jié)果,具體實(shí)現(xiàn)框圖略——編者注。為了提高處理速度,采用乘法運(yùn)算代替除法運(yùn)算,本文中使用的量化步長(zhǎng)是將JPEG標(biāo)準(zhǔn)推薦量化表的倒數(shù)乘以211后得到的,并存儲(chǔ)在ROM中,經(jīng)過量化后,將計(jì)算結(jié)果右移11位即恢復(fù)為實(shí)際的量化結(jié)果。

2.2.3Z字掃描

經(jīng)過量化處理后,每個(gè)8×8圖像子塊中將出現(xiàn)很多值為0的高頻分量,主要集中在8×8矩陣的右下角,使用Z字形掃描的方式將8×8的二維系數(shù)矩陣變成一維數(shù)據(jù)流(第一個(gè)為DC系數(shù),其余63個(gè)為AC系數(shù)),這樣可以使0值分量集中,以便之后的數(shù)據(jù)編碼,具體實(shí)現(xiàn)框圖略——編者注。

2.2.4熵編碼

為了減少圖像的編碼長(zhǎng)度,要對(duì)Z字掃描后的DC系數(shù)和AC系數(shù)做基于統(tǒng)計(jì)特性的熵編碼,該部分主要是DC系數(shù)根據(jù)直流Huffman編碼表進(jìn)行差分編碼,AC系數(shù)先進(jìn)行行程長(zhǎng)度編碼,再根據(jù)交流Huffman編碼表進(jìn)行編碼,實(shí)現(xiàn)框圖如圖3所示。其中Huffman編碼模塊是將JPEG標(biāo)準(zhǔn)推薦的Huffman編碼表存儲(chǔ)在ROM中,通過查表的方式實(shí)現(xiàn)Huffman編碼。

?

圖3 編碼實(shí)現(xiàn)框圖

3實(shí)驗(yàn)及結(jié)果分析

本系統(tǒng)實(shí)驗(yàn)平臺(tái)略——編者注,該實(shí)驗(yàn)硬件平臺(tái)主要包括以下幾個(gè)部分:①Kinect傳感器,生成分辨率為640×480的數(shù)字圖像數(shù)據(jù);

②搭載有XC7Z020CLG484芯片的ZedBoard開發(fā)板,實(shí)現(xiàn)JPEG圖像壓縮系統(tǒng);

③無(wú)線路由器,連接ZedBoard與PC機(jī),實(shí)現(xiàn)以太網(wǎng)通信。

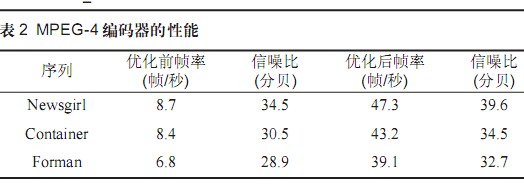

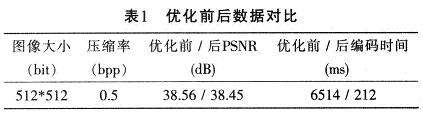

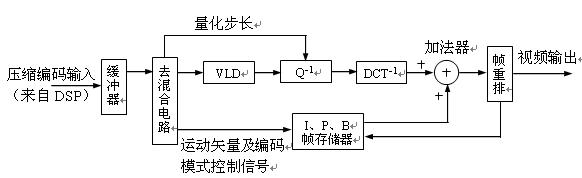

本實(shí)驗(yàn)中,Zynq SoC平臺(tái)ARM部分移植了Ubuntu Linux操作系統(tǒng),由OpenNI驅(qū)動(dòng)程序獲取Kinect傳感器生成的圖像數(shù)據(jù),進(jìn)行色彩空間的變換得到亮度分量Y,重排序后通過AXI_HP總線傳輸給FPGA部分。FPGA部分讀取ARM端預(yù)處理后的圖像數(shù)據(jù),然后進(jìn)行圖像壓縮編碼。實(shí)現(xiàn)640×480像素灰度圖像壓縮編碼算法的FPGA資源占用量如表1所列,算法實(shí)現(xiàn)中涉及640×480尺寸數(shù)據(jù)的存儲(chǔ),因此消耗了較多的BRAM資源。FPGA部分完成圖像壓縮編碼后,便將壓縮后的數(shù)據(jù)通過AXI_HP總線傳輸回ARM部分,最后通過以太網(wǎng)傳輸壓縮后圖像數(shù)據(jù)到PC端,進(jìn)行實(shí)時(shí)解碼顯示。

?

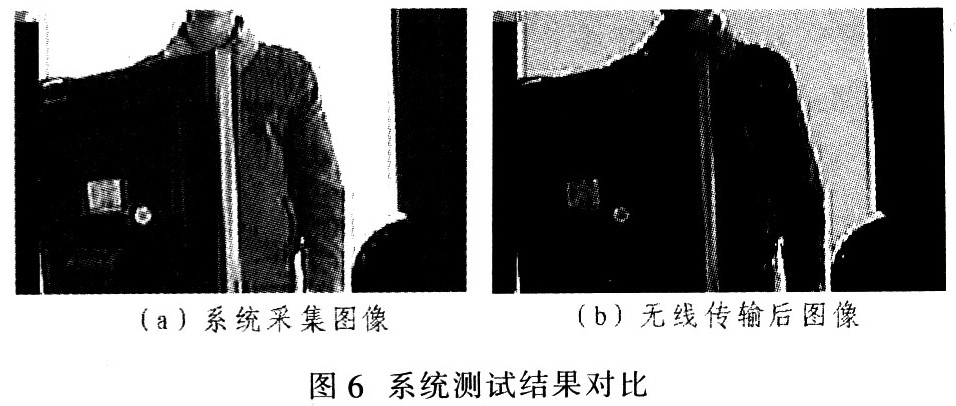

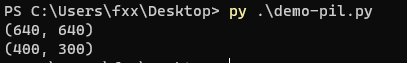

經(jīng)過實(shí)驗(yàn)測(cè)試,ARM端CPU運(yùn)行時(shí)鐘頻率為667 MHz,完成一幅圖像數(shù)據(jù)的采集、預(yù)處理等操作,需要耗時(shí)約14 ms;FPGA端運(yùn)行時(shí)鐘頻率為100 MHz,完成ARM端預(yù)處理后數(shù)據(jù)的讀取、圖像壓縮編碼等操作,需要307 251個(gè)時(shí)鐘周期,耗時(shí)3.07 ms。由于不同復(fù)雜度的圖像壓縮后數(shù)據(jù)量不一樣,所以每幅圖像壓縮后數(shù)據(jù)傳輸回ARM端的時(shí)間也不一樣。如圖4所示的實(shí)驗(yàn)測(cè)試圖樣,在具有大量圖像細(xì)節(jié)的情況下,本系統(tǒng)實(shí)現(xiàn)的壓縮比為13.81,經(jīng)過FPGA算法壓縮完成后的數(shù)據(jù)傳輸回ARM需耗時(shí)0.03 ms,完成圖像壓縮處理的時(shí)間總消耗不超過17.5 ms。針對(duì)Kinect傳感器30 fps的幀率而言,該系統(tǒng)在一個(gè)圖像周期內(nèi)足以完成圖像壓縮處理操作,具備良好的實(shí)時(shí)性。

圖4所示為隨機(jī)獲取兩幅圖像的實(shí)驗(yàn)測(cè)試結(jié)果,測(cè)試結(jié)果表明,該系統(tǒng)在獲得較大壓縮比的同時(shí),保留了原始圖片的關(guān)鍵信息,能滿足實(shí)際應(yīng)用需求。

?

圖4 實(shí)驗(yàn)測(cè)試結(jié)果

結(jié)語(yǔ)

本文主要介紹了一個(gè)基于Zynq SoC的JPEG圖像壓縮系統(tǒng)的實(shí)現(xiàn)過程。該系統(tǒng)按照處理流程劃分為圖像數(shù)據(jù)獲取、圖像編碼處理以及壓縮后數(shù)據(jù)傳輸3個(gè)部分。本文創(chuàng)新性的采用了ARM與FPGA軟硬件協(xié)同設(shè)計(jì)的方式對(duì)JPEG圖像壓縮系統(tǒng)進(jìn)行了高效實(shí)現(xiàn),充分結(jié)合了ARM與FPGA各自在開發(fā)上的特點(diǎn),并采用Zynq片上高性能AXI_HP總線實(shí)現(xiàn)了ARM與FPGA核間高速通信。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論