0 引言

隨著新型傳感技術的發展,衛星遙感圖像的分辨率迅速提升,數據量的爆炸式增長趨勢為傳輸信道和存儲空間帶了極大的壓力,因而,能否對遙感圖像進行在軌實時高效壓縮便成為制約遙感技術發展的一個關鍵問題[1]。目前,相對于基于離散余弦變化廣泛采用的小波變換壓縮算法具有非常好的抗誤碼性能,不過相對于早期的壓縮算法,這類算法的復雜度明顯提高,運算量和內存消耗增大[2],這對圖像壓縮處理系統提出了較高的要求。

FPGA和DSP在數據處理平臺中發揮著日益重要的作用,FPGA擅長執行并行處理,而DSP擅長多算法任務和多條件操作等,因而采用FPGA和多片DSP的并行運算系統受到越來越多的關注。

為了探索遙感圖像的機載實時壓縮技術,本文首先根據遙感圖像處理數據及流程特點,設計了2 FPGA+8 DSP的并行拓撲架構,并構建了機載實時處理硬件平臺,最后基于該平臺介紹了JPEG2000壓縮算法的實現方法,實驗結果表明該平臺具有較強的遙感數據實時處理能力。

1 圖像壓縮系統設計

1.1 芯片選型

在本系統中,FPGA主要實現外部接口、邏輯控制和時序控制等功能,并承擔部分數據處理工作,因此,需要具有較大的存儲空間,支持PCIE接口設計,具備較多的邏輯資源實現圖像預處理功能,并具有足夠的I/O口為FPGA管理多片DSP提供管腳支持。本系統選用Xilinx公司的XC6VLX240T。

為了滿足遙感圖像實時壓縮的要求,系統中選用的DSP要具有很強的定點和浮點運算能力;要具有高性能的互聯接口;支持DSP之間、DSP與FPGA之間建立高速的數據通道;并且具有較大的內部存儲空間,適應圖像壓縮過程中大量中間數據的高速緩存。因此本系統選用ADI公司的TS201。

1.2 并行互聯方式

實現大規模運算的高速執行,需要借助多個處理單元同時運行來減少任務執行時間。并行技術可以體現在處理器內部、處理器級以及系統級等方面,處理器間的拓撲結構可分為兩種[3]:(1)多處理器共享總線和存儲器的緊耦合結構;(2)多處理器通過獨立接口實現互聯的松耦合結構。

緊耦合結構的優點在于提供全局物理地址空間,允許任何處理器對等訪問全部存儲器,便于程序設計。ADSP-TS201的主機接口可以支持最高64 bit位寬的總線共享,全局映射的統一尋址空間可實現多處理器及存儲器間的無縫連接。但是,當處理器數目較多時,頻繁的數據交換會產生嚴重的總線控制權競爭問題,從而導致系統運算效率降低,特別是在進行大數據量運算和大數據量通信時,這個缺點會極大地制約整個系統的運行效率。遙感圖像的實時壓縮是運算密集型、數據吞吐密集型的數據處理過程,緊耦合結構很難實現運算、存儲、傳輸間的平衡,不利于實現復雜壓縮算法的實時處理。

在分布式松耦合結構中,每片DSP通過獨立的接口連接到FPGA,這樣就能避免多個DSP同時訪問FPGA時的數據沖突。FPGA與DSP間常用的接口設計方法主要有3種:(1)采用外部雙口RAM;(2)在FPGA內部構建雙口RAM;(3)通過DSP的高速傳輸接口。前兩種連接方式中數據直接通過總線傳輸,且不涉及復雜的通信協議,接口設計比較簡單[4],但是當芯片數量較多時,硬件設計中的管腳及布線壓力會很大;

另外DSP的數據總線將同時用于與FPGA和與外部存儲器通信,仍然會存在總線競爭風險。TS201可提供4路鏈路口,在采用4位并行方式傳輸時,可支持高達1.2 GB/s的雙向吞吐率;數據通信可由處理器核控制,也可由DMA控制器控制,而不需要占用處理器資源,這能為FPGA與DSP、DSP與外部存儲器以及DSP與DSP之間的高速數據傳輸提供便利,解決在數據密集型處理中這一制約系統整體性能的問題,因此,本系統將采用這種互聯結構。

1.3 系統結構

本系統采用2片FPGA和8片DSP的拓撲結構,其結構框圖如圖1所示。8片DSP分為結構對稱的2簇,構成兩個并行的運算子模塊。每簇內的4片DSP利用鏈路口點對點互聯,并且每片DSP分別通過一個鏈路口與FPGA相連。2片FPGA各負責一個運算子模的任務和數據交互管理工作。這種拓撲結構使得簇內各DSP以及DSP與FPAG間都能實現高速互聯,且增強了數據流的靈活性,可實現按任務劃分的流水并行計算,也可實現按數據劃分的分布式并行計算。

每片DSP都外掛4 M×32 bit的SDRAM作為外部存儲空間,利用TS201內的SDRAM地址映射空間和外部接口,借助SDRAM控制器可輕松實現無縫連接,滿足大量數據實時處理過程中的存儲需求。DSP采用EPROM和鏈路口相結合的程序引導和加載方式[5],每簇外掛1片Flash,簇內其他DSP采用鏈路口形式,這種設計避免了給每片DSP配備Flash,降低了功耗和電路面積。

1.4 FPGA程序設計

在本系統中,FPGA作為邏輯控制中心,主要實現以下幾個功能:

(1)數據解包、切分、串/并轉換、打包、分發等數據管理功能;

(2)數據緩存,利用DDR3 SDRAM乒乓作業的工作方式實現數據無縫緩存;

(3)快速流水協議,實現與TS201鏈路口進行高速通信;

(4)自定義接口協議,參考快速流水協議設計自定義協議,通過LVDS總線實現與另一片FPGA通信;

(5)數據預處理功能,利用內部DSP和邏輯資源實現數據預處理,發揮FPGA并行處理的運算優勢。此外,系統中的FPGA_A還負責與上位機通信,因此,需要利用設計PCIE接口單元。FPGA_A中的邏輯結構如圖2所示,FPGA_B采用相似的邏輯設計。

2 JPEG2000壓縮應用實例

JPEG2000作為新一代靜止圖像壓縮標準,能在甚低比特率壓縮時提供良好的率失真特性和主觀視覺質量,并且具有非常好的抗誤碼性能,在星載遙感圖像壓縮領域受到越來越多的關注。

JPEG2000的基本編碼過程為:源圖像數據經正向預處理后進行離散小波變換(DWT),對變換后的DWT系數進行量化,再進行熵編碼,最后根將熵編碼后的數據組織成壓縮碼流輸出[6]。

為了使程序在TS201上高效運行,從系統層、算法層、代碼層三個不同層面上對JPEG2000壓縮程序進行了優化[7,8],例如:優化DWT中的中間結果存儲方式,在節約內存的同時減少訪問時間;采用建立上下文索引表的方法減小嵌入式最優截斷編碼過程中的掃描運算量;適當修改數據類型,進行數據拼接存儲,提高數據讀寫效率等。

2.1 DSP與FPGA接口設計

此外,系統的高效運行還依賴于高效的數據收發機制。DSP通過Link Port接口與FPGA通信,實現原始圖像數據的接收和壓縮碼流的發送,本系統DSP中的發送和接收單元中分別采用了乒乓緩存+突發式DMA傳輸的設計方法。以數據接收單元為例,DSP中分配了3個緩存空間:input_buffer1、input_buffer2和input,其中,input_buffer1和input_buffer2以乒乓作業的方式緩存接收數據,input用于緩存預處理后的圖像數據,以備后續壓縮處理。

在接收數據時,DSP接收到FPGA的發送指令,便開啟Link Port接口接收數據到Link Port Receive Buffer中,在接收到指定數據量后,Link Port接口自動開啟DMA傳輸,將數據轉移到input_buffer1中,并關閉Link Port口,以防止接收到錯誤數據。此后,DSP對input_buffer1中的數據進行數據類型轉換等預處理,然后轉存到input緩存區中。考慮到Link Port接收、DMA傳輸均需要耗時,而又可以不需要內核參與。

因此,設計了雙通道乒乓作業的接收方式,這樣在數據的突發傳輸任務中,可以配置好參數交給Link Port接口和DMA來獨立完成,從而解放出內核的邏輯計算單元,使之專注于運算和判斷。DSP內核在監測到本次DMA傳輸完成后,首先交換DMA接收端的選擇指針,指向input_buffer2,再開啟Link Port接口,便可以利用內核進行預處理操作了。處理過程中如果有新數據到來,硬件會自動完成接收操作并更改狀態標識,內核只需要在完成當前處理后,查詢其狀態標識便可知道數據是否已經接收完成。如此循環,便可實現圖像數據的快速接收。

2.2 軟件設計流程

從系統層面來看,FPGA與其控制的4片DSP組成兩個運算節點A、B,8個DSP之間執行以數據劃分的分布式并行計算。FPGA_A通過PCIE總線接收源圖像數據,解析包頭獲取任務信息并進行串/并轉換、數據緩存、數據切分、將數據分發給DSP和FPGA_B等。DSP內的壓縮處理以圖像塊為單位,在完成當前圖像塊數據的接收后,開始壓縮處理并將壓縮碼流實時回傳至FPGA,DSP內程序流程如圖3所示。FPGA接收各DSP發送的壓縮數碼流數據包,再以圖像塊為單位進行碼流重組、緩存,最終通過PCIE總線傳輸給上位機。

3 實驗結果

為了驗證壓縮系統的可行性,本文采用12 800×12 800的8 bit圖像數據分別進行了2:1無損壓縮和8:1高倍率壓縮實驗。圖4所示為Lena圖像和一副紋理復雜的城市場景遙感圖像的無損壓縮實驗結果,可見系統具有較高的壓縮質量。表1為應用本平臺的JPEG2000壓縮系統的性能測試結果,無損壓縮時系統最高吞吐速率可達5.9 Mpixels/s,高倍率壓縮時性能略有提升,最高吞吐速率可達6.2 Mpixels/s,可見,本系統具有較強的數據處理能力。

4 結論

本文首先分析了多DSP并行處理拓撲結構及片間互聯方式,為了有效平衡系統運行速度、數據傳輸能力和板上存儲空間三大因素,采用松耦合結構設計了基于2 FPGA+8 DSP的高速大容量實時壓縮處理平臺。最后,基于該平臺實現了JPEG2000壓縮處理。實驗結果表明,該系統具有強大的數據處理和吞吐能力,能夠為遙感圖像實時壓縮應用奠定技術基礎。

參考文獻

[1] 劉榮科,張曉林,廖小濤。星載遙感圖像壓縮編碼技術綜述[J]。遙測遙控,2004,25(2):7-12.

[2] 肖志東,肖明君,劉淼。基于小波變換的遙感圖像壓縮算法綜述[J]。科技創新導報,2008(35):75.

[3] Wu Jie.分布式系統設計[M]。高傳善,譯。北京:機械工業出版社,2001.

[4] 唐垚,曹劍中,李變俠,等。高分辨率圖像采集與壓縮系統的設計實現[J]。科學技術與工程,2007,5(20):1510-1513.

[5] Analog Devices.ADSP-TS20x TigerSHARC processor boot loader kernels operation[Z].2004.

[6] ISO/IEC 15444-13:2008(E).Information technology-JPEG 2000 image coding system:An entry level JPEG 2000 encoder[S].2008.

[7] BISHOP S L,RAI S,GUNTURK B,et al.Reconfigurable implementation of wavelet integer lifting transforms for image compression[C].ReConFig 2006,IEEE International Conference on:1-9.

[8] LIAN C J,CHEN K F.Analysis and architecture design of block-coding engine for EBCOT in JPEG2000[J].IEEE Transactions on Circuits and Systems for Video Teehnology,2003,13(3):219-230.

編輯:jq

-

dsp

+關注

關注

555文章

8120瀏覽量

354023 -

FPGA

+關注

關注

1640文章

21910瀏覽量

611588 -

數據傳輸

+關注

關注

9文章

1987瀏覽量

65371 -

三線耦合結構

+關注

關注

0文章

2瀏覽量

1711

發布評論請先 登錄

相關推薦

基于衛星圖像的智能定位系統軟件

環境遙感行業發展趨勢分析 遙感數據集的獲取與使用

遙感監測的精度與誤差分析 遙感影像分類的方法與技巧

遙感影像分析的方法與步驟

基于 DSP5509 進行數字圖像處理中 Sobel 算子邊緣檢測的硬件連接電路圖

常見的遙感數據源有哪些類型

常見的遙感數據類型有哪些

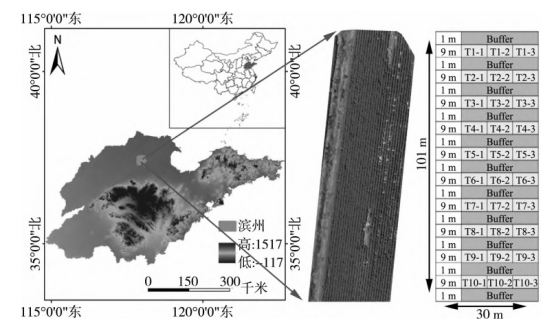

基于無人機多光譜遙感的棉花生長參數和產量估算

圖像邊緣檢測系統的設計流程

高光譜成像系統:高光譜遙感圖像的光譜混合模型

評論