隨著數字信號處理(Digital Signal ProcESSor,DSP)技術的發展,DSP已被廣泛應用于雷達、通信等領域。雖然DSP經歷了幾代的發展,運算速度和能力都有了很大的提高,但在很多情況下,單片DSP已經不能滿足實時處理的要求,必須尋求多片DSP并行處理的方案。

從系統結構出發可以將并行系統分為共享存儲器并行系統和分布存儲器并行系統。AD公司推出的SHARC系列DSP芯片同時支持這二種并行處理器結構。通常,將AD公司的一系列雙位高性能浮點DSP稱為SHARC(Super Harvard Architecture)。對于共享存儲器系統,通過SHARC間的外部共享總線實現。對于分布存儲器系統,通過2個SHARC間的鏈路口直接連接,實現DSP間點對點的通信。

然而,不能認為將多個SHARC互相進行硬件連接就實現了并行處理。真正的并行處理應該是使互連的各個DSP能夠協調工作,縮短系統處理的時間。這需要并行系統中SHARC間能完成數據流的傳遞。并行系統中各個SHARC間數據流的傳遞同數據處理同等重要。本文針對這二種并行方式,分別給出了軟件的設計方法和設計技巧,并且給出了針對ADSP2116X的程序實現。

1 共享存儲器并行系統的設計

SHARC為多處理器系統提供了強大的支持,用戶可以在不附加任何外圍電路的情況下構成共享存儲器并行系統。SHARC具有一套巧妙的分布式總線仲裁機制。使用2~6片SHARC把各SHARC的相應引腳相連就可以共享外部總線。每片SHARC都可以訪問其他SHARC的片內存儲器,還可以通過設置IOP寄存器啟動其他SHARC的DMA操作。

組成共享存儲器并行系統時,每一個SHARC都有一個惟一的標識:ID2~0,取值范圍為000~110。ID=001表示該SHARC為1號DSP,ID=010表示該SHARC為2號DSP,依此類推。ID=000表示是單DSP系統。在多DSP系統中,ID=001號的DSP是必須存在的,這是DSP加載成功以后的主處理器。

在共享存儲器系統中,任何時刻都只有一片SHARC可以驅動外部總線,該SHARC就被稱為主處理器。其余的從SHARC如果需要訪問總線,則必須先申請總線。主處理器如果此時沒有數據傳遞或者總線占用時間到,就會釋放總線控制權,把自己的外部總線驅動為三態,完成總線控制權的轉移。

主處理器對從SHARC的內存訪問和對自己的內存訪問一樣簡單,既可以通過內核直接讀寫完成,也可以通過外部口DMA實現。在共享存儲器并行系統中,每一片SHARC根據自己的ID號都有一個映射的多處理器存儲空間。例如對于ADSP2116X,ID=001的SHARC對應的多處理器存儲空間為0x100000~0x1F FFFF,ID=010的SHARC對應的多處理器存儲器空間為0x20 0000~0x2F FFFF等。共享存儲系統的LDF文件與單DSP系統有些不同。下面給出它的一個示例(以2個SHARC為例)。

例1:共享存儲器系統LDF文件。

ARCHITECTURE(ADSP-21160)

SEARCH_DIR($ADI_DSP211xxlib)

MPMEMORY{

DSP1{START(0X100000)} //第一片DSP在多處理

//器空間的映射地址

DSP2{START(0X200000)} } //第二片DSP在多處理

//器空間的映射地址

MEMORY

{pm_rsTI { TYPE(PM RAM)START(0x00040004)END

(0x0004000f)WIDTH(48) }

pm_code { TYPE(PM RAM)START(0x00040100)END

(0x00049fff)WIDTH(48) }

dm_data { TYPE(DM RAM)START(0x00050000)END

(0x00059fff)WIDTH(32) } }

PROCESSOR DSP1

{LINK_AGAINST(DSP2.DXE) //需要重新連接的

//DSP2的目標文件

OUTPUT(DSP1.DXE) //DSP1輸出的目標文件

…… //和單DSP系統相同,故略去,下同

}

PROCESSOR DSP2

{LINK_AGAINST(DSP1.DXE) //需要重新連接的

//DSP1的目標文件

OUTPUT(DSP2.DXE) //DSP2輸出的目標文件

……

}

這樣,這二片DSP便可以通過外部總線訪問對方的內部資源。當DSP1需要直接訪問DSP2中的某一變量時,只需要DSP2將該變量設置為global類型,DSP1就可以在多處理器空間中通過外部總線直接訪問該變量,當然,也可以根據變量的內存地址直接訪問。

在共享存儲器并行系統中,當二個SHARC之間通過總線進行數據傳遞時,如果此時其他的DSP需要訪問外部總線,則只有掛起等待。這樣,在多個DSP間數據交換比較頻繁時,系統的效率就會大大降低。另外,在共享存儲器并行系統中,最多只能有6個DSP互相連接。如果需要更多的DSP并行工作,共享存儲器并行系統便無能為力。采用以下介紹的分布存儲器并行系統,可以有效地解決這個問題。

2 分布存儲器并行系統的設計

ADSP2116X提供了獨立的6個鏈路口,每個鏈路口可以實現與其他ADSP2116X或者外圍設備點對點的通信。每個鏈路口包括8位雙向數據線(LxDAT7~0),1個雙向時鐘信號(LxCLK),1個雙向確認信號(LxACK)。但是,鏈路口沒有為發送和接收提供2套管腳,所以在任何時刻鏈路口只能工作在單工狀態。依靠鏈路口進行雙DSP間的數據傳遞時,只需要把2個DSP的10個管腳對應連接即可,不需要任何外部附加邏輯。

在ADSP2116X內部有6個鏈路緩沖器。用戶通過定義LAR寄存器,可以為每個鏈路口選擇一個或幾個緩存器。鏈路緩沖器一端與內部總線相連,另一端通過LAR寄存器與不同的鏈路口相連。需要注意的是,鏈路口與鏈路緩存器是完全不同的概念。鏈路緩沖器可以理解為一個雙向的FIFO,而鏈路口僅僅代表其對外的10個管腳。鏈路口的特性很大程度上是由其正在使用的緩沖器的特性決定的。

ADSP2116X的鏈路口發送時鐘頻率可以通過LCTLx寄存器的LxCLKD位設置(1,1/2,1/3,1/4核時鐘頻率),鏈路口數據線根據需要可以選擇為8位或4位。發送方在時鐘LxCLK的上升沿送出8/4位碼,接收方利用時鐘下降沿鎖存8/4位碼,并且接收方使LxACK有效,表示已準備好接收下一個字。在每個字開始發送時,發送方如果看到LxACK無效,則將LxCLK保持為高,并等待LxACK有效后才開始發送新字。當發送緩沖為空時,LxCLK將保持為低電平。

鏈路口數據傳輸可以通過DMA方式和內核直接訪問二種方式。DMA方式傳輸時不需要內核干預,在傳輸數據量比較大時效率很高,但是需要首先進行DMA參數設置。當僅有個別數據需要通過鏈路口傳遞的情況下,往往不使用DMA方式,而是通過ADSP2116X的內核直接訪問。用戶可以通過LCOM寄存器中緩沖器的狀態來控制內核對鏈路口緩沖進行讀寫操作,也可以通過相應的中斷從鏈路口緩沖器中讀寫數據,如“DM(LBUF0)=R0;”或者“R0=DM(LBUF0);”等。值得注意的是,無論是試圖從一個空的鏈路緩沖中讀,還是試圖向滿的緩沖中寫,內核的指令都會掛起,直到操作成功為止。因此,內核指令直接讀寫鏈路緩存時,需要首先判斷鏈路緩沖狀態。

ADSP2116X為每個鏈路口提供了一個專用的DMA通道,它們分別占用DMA中的4~9通道。鏈路口的DMA使用非常方便,只需將對應的DMA參數寄存器(IIx,IMx,Cx)設置完畢,使能LCTLx中對應通道的LxDEN即可。在當前DMA結束(或者鏈式DMA全部結束)后,會觸發一個可屏蔽中斷通知用戶。啟動鏈路口DMA的順序如下:

(1)由LAR寄存器的AxLB為鏈路口分配一個LBUFx;

(2)由LCTL寄存器的LxEN使能這個LBUFx,并設置好LCTL控制寄存器;

(3)設置DMA參數(IIy,IMy,Cy);

(4)置位LCTL寄存器的LxDEN,就啟動了DMA。

其中:x=0~5,y=4~9。

下面給出一個利用鏈路口DMA發送數據的示例。

例2:利用鏈路口0進行數據發送。

.SECTION/dm

dm_data;

.VAR

trans_data[size];

.SECTION/pm

pm_code:

……

r0=0x0002c688;

dm(LAR)=r0;

r9=0x00000229; /*LBUF0使能、發送、8位字寬、核時鐘速率*/

dm(LCTL0)=r9;

r0=trans_data;

dm(II4)=r0; /*需要發送數據的起始地址*/

r0=1;

dm(IM4)=r0;

r0=size;

dm(C4)=r0;

ustat1=dm(LCTL0);

bit set ustat1 L0DEN; /*啟動發送DMA*/

dm(LCTL0)=ustat1;

如果傳輸的數據不在一段連續的內存區,而是在多段數據塊中,可以利用鏈式DMA。鏈式DMA可以在當前DMA操作結束后自動重新配置當前通道并開始新的DMA,所有這些操作都不需要內核的干預。在鏈式DMA過程中,用戶只要對DMA參數配置一次,就可以方便地完成多塊數據的DMA傳輸。

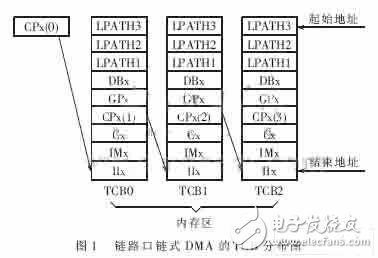

鏈式DMA是通過CPx寄存器實現的。對于ADSP2116X來說,CPx是一個19位的寄存器。寄存器中低18位表示相對于基地址0x40000的偏移量,用戶在這個地址的內部存儲器中存放下一次DMA的參數,這些參數叫做TCB(Transfer Control Blocks)。CPx中的第19位是控制當前鏈式DMA完成后是否產生中斷的PCI位。如果把全局地址賦給CPx,則PCI位一定為1,表明一定會產生中斷。

用戶只需要在內存區填寫多個TCB的表格,用其中的CPx字段將每個表格串起來并將第一個表格的結束地址放入CPx寄存器,就可以啟動鏈式DMA。要終止一個鏈式DMA,只需要把最后一個TCB中的CPx字段填0即可。TCB結構如圖1所示。

下面是建立一個鏈式DMA的順序:

電子發燒友App

電子發燒友App

評論