推挽結(jié)構(gòu)詳解

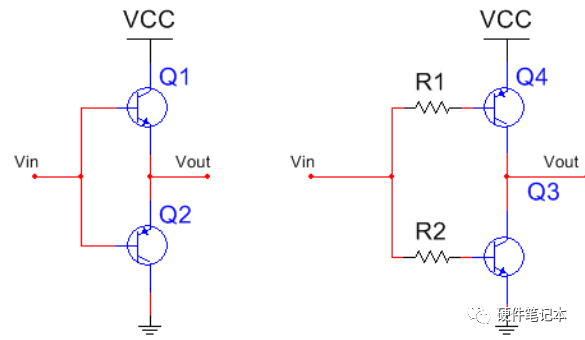

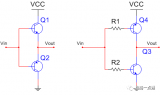

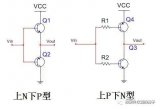

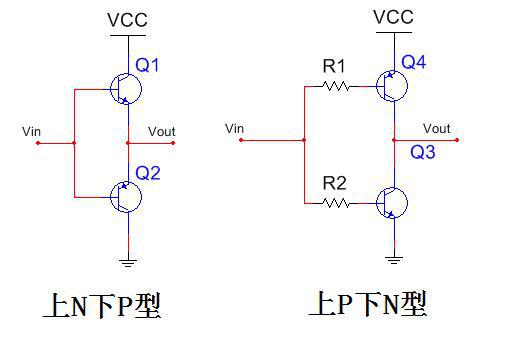

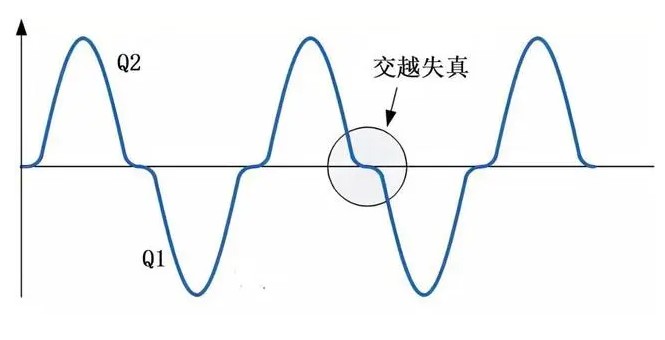

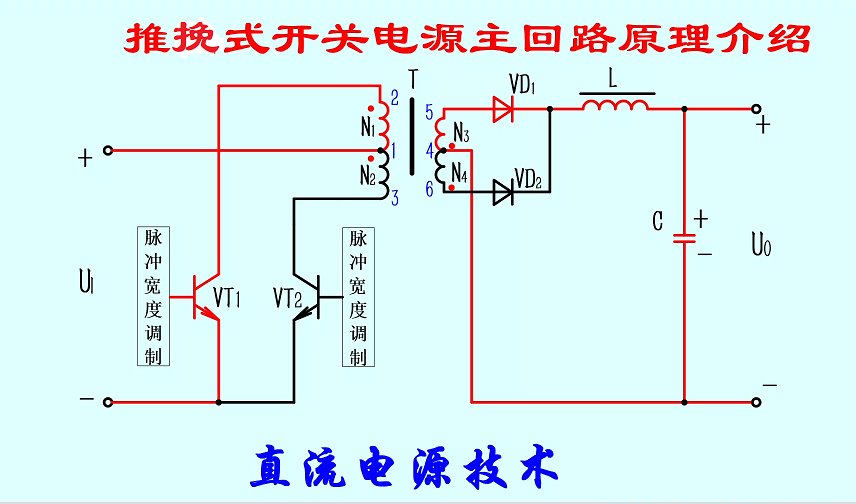

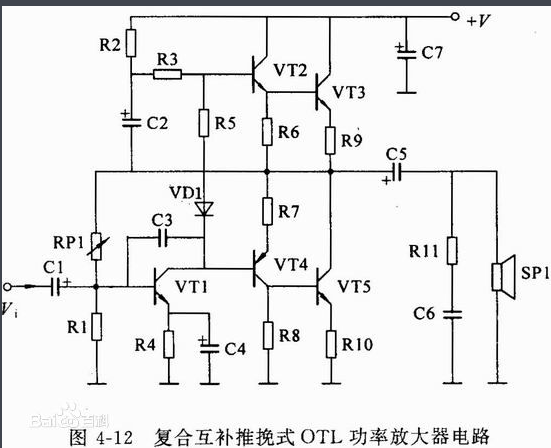

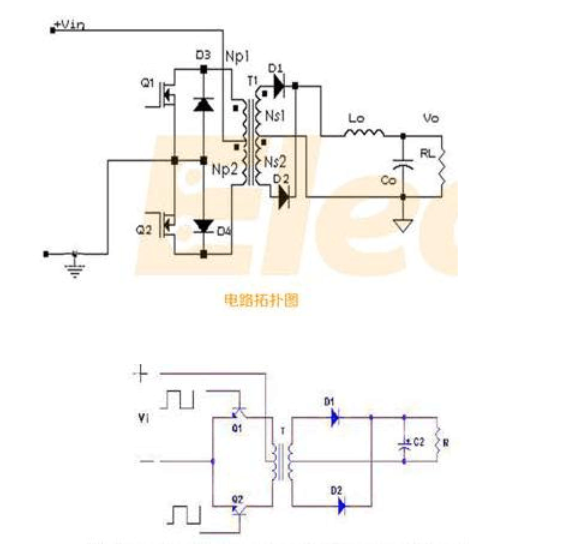

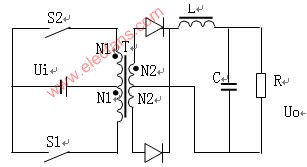

推挽電路是兩個(gè)參數(shù)相同的三極管或MOSFET,以推挽方式存在于電路中,各負(fù)責(zé)正負(fù)半周的波形放大任務(wù),電路工作時(shí),兩只對(duì)稱的功率開關(guān)管每次只有一個(gè)導(dǎo)通,所以導(dǎo)通損耗小效率高。

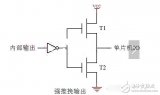

一般是指兩個(gè)三極管分別受兩互補(bǔ)信號(hào)的控制,總是在一個(gè)三極管導(dǎo)通的時(shí)候另一個(gè)截止。要實(shí)現(xiàn)線與需要用OC(open collector)門電路 。如果輸出級(jí)的有兩個(gè)三極管,始終處于一個(gè)導(dǎo)通、一個(gè)截止的狀態(tài),也就是兩個(gè)三級(jí)管推挽相連,這樣的電路結(jié)構(gòu)稱為推拉式電路或圖騰柱(Totem-pole)輸出電路。

推拉式輸出級(jí)既提高電路的負(fù)載能力,又提高開關(guān)速度

開漏輸出:輸出端相當(dāng)于三極管的集電極。 要得到高電平狀態(tài)需要上拉電阻才行。 適合于做電流型的驅(qū)動(dòng),其吸收電流的能力相對(duì)強(qiáng)(一般20ma以內(nèi))。

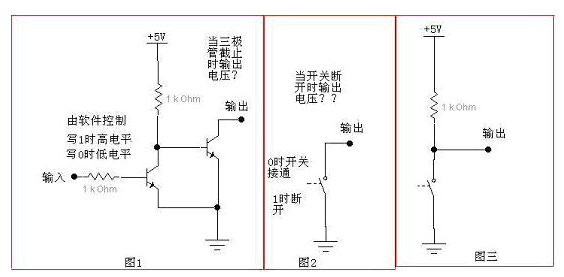

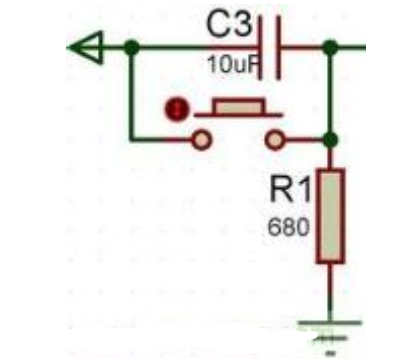

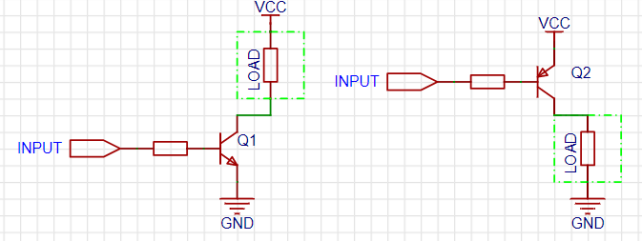

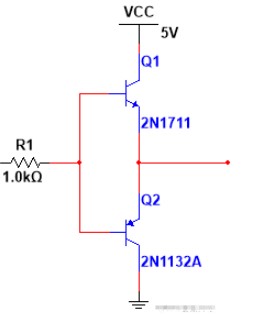

我們先來說說集電極開路輸出的結(jié)構(gòu)。集電極開路輸出的結(jié)構(gòu)如圖1所示,右邊的那個(gè)三極管集電極什么都不接,所以叫做集電極開路(左邊的三極管為反相之用,使輸入為“0”時(shí),輸出也為“0”)。對(duì)于圖1,當(dāng)左端的輸入為“0”時(shí),前面的三極管截止(即集電極C跟發(fā)射極E之間相當(dāng)于斷開),所以5V電源通過1K電阻加到右邊的三極管上,右邊的三極管導(dǎo)通(即相當(dāng)于一個(gè)開關(guān)閉合);當(dāng)左端的輸入為“1”時(shí),前面的三極管導(dǎo)通,而后面的三極管截止(相當(dāng)于開關(guān)斷開)。

我們將圖1簡(jiǎn)化成圖2的樣子。圖2中的開關(guān)受軟件控制,“1”時(shí)斷開,“0”時(shí)閉合。很明顯可以看出,當(dāng)開關(guān)閉合時(shí),輸出直接接地,所以輸出電平為0。而當(dāng)開關(guān)斷開時(shí),則輸出端懸空了,即高阻態(tài)。這時(shí)電平狀態(tài)未知,如果后面一個(gè)電阻負(fù)載(即使很輕的負(fù)載)到地,那么輸出端的電平就被這個(gè)負(fù)載拉到低電平了,所以這個(gè)電路是不能輸出高電平的。

再看圖三。圖三中那個(gè)1K的電阻即是上拉電阻。如果開關(guān)閉合,則有電流從1K電阻及開關(guān)上流過,但由于開關(guān)閉其它三個(gè)口帶內(nèi)部上拉),當(dāng)我們要使用輸入功能時(shí),只要將輸出口設(shè)置為1即可,這樣就相當(dāng)于那個(gè)開關(guān)斷開,而對(duì)于P0口來說,就是高阻態(tài)了。

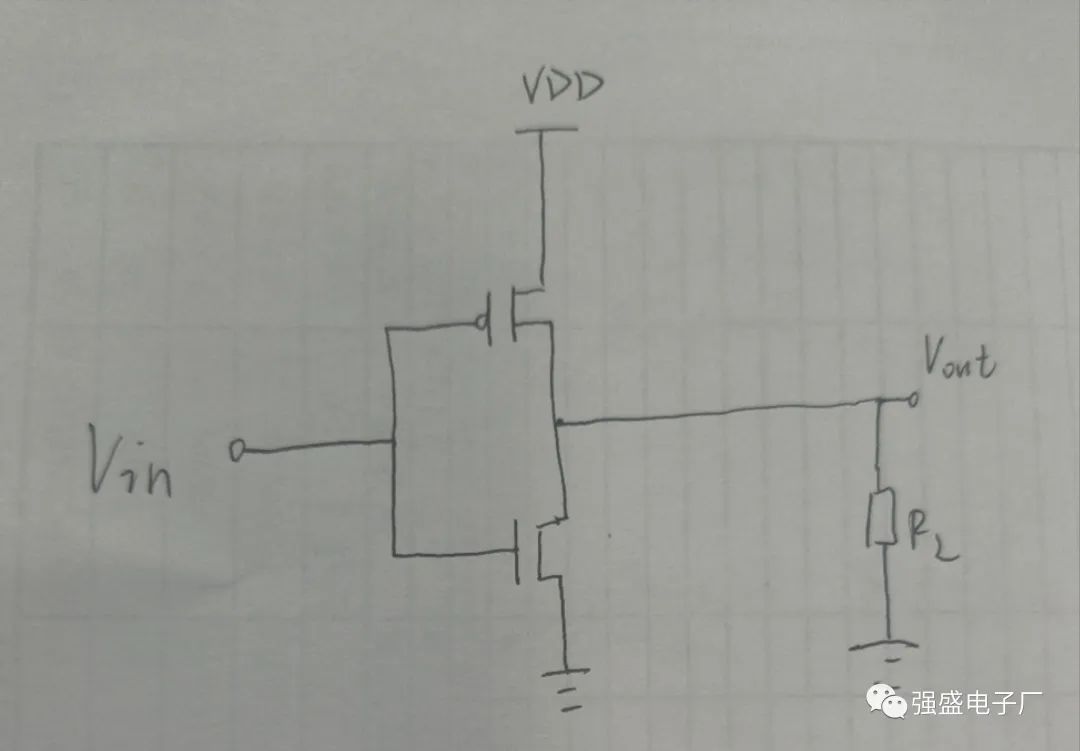

對(duì)于漏極開路(OD)輸出,跟集電極開路輸出是十分類似的。將上面的三極管換成場(chǎng)效應(yīng)管即可。這樣集電極就變成了漏極,OC就變成了OD,原理分析是一樣的。

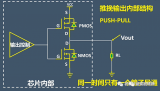

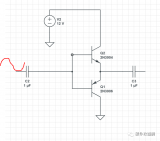

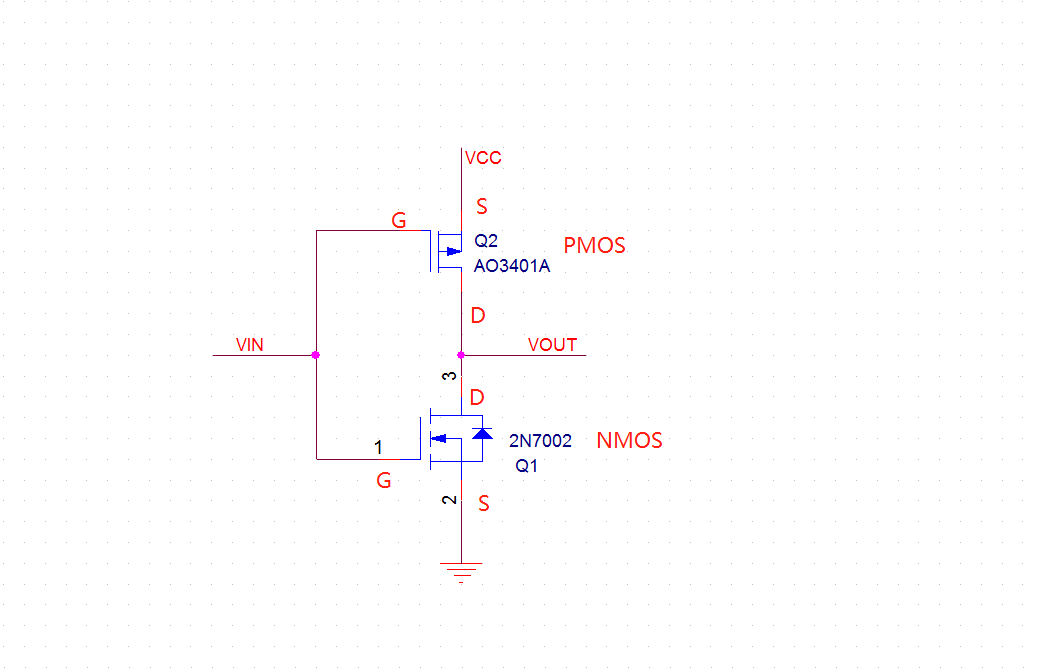

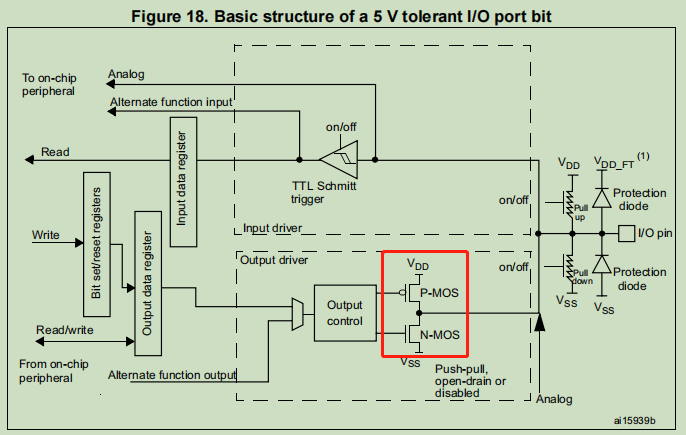

另一種輸出結(jié)構(gòu)是推挽輸出。推挽輸出的結(jié)構(gòu)就是把上面的上拉電阻也換成一個(gè)開關(guān),當(dāng)要輸出高電平時(shí),上面的開關(guān)通,下面的開關(guān)斷;而要輸出低電平時(shí),則剛好相反。比起OC或者OD來說,這樣的推挽結(jié)構(gòu)高、低電平驅(qū)動(dòng)能力都很強(qiáng)。如果兩個(gè)輸出不同電平的輸出口接在一起的話,就會(huì)產(chǎn)生很大的電流,有可能將輸出口燒壞。而上面說的OC或OD輸出則不會(huì)有這樣的情況,因?yàn)樯侠娮杼峁┑碾娏鞅容^小。如果是推挽輸出的要設(shè)置為高阻態(tài)時(shí),則兩個(gè)開關(guān)必須同時(shí)斷開(或者在輸出口上使用一個(gè)傳輸門),這樣可作為輸入狀態(tài),AVR單片機(jī)的一些IO口就是這種結(jié)構(gòu)。

開漏電路特點(diǎn)及應(yīng)用

在電路設(shè)計(jì)時(shí)我們常常遇到開漏(open drain)和開集(open collector)的概念。

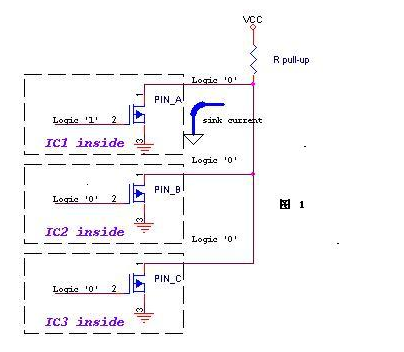

所謂開漏電路概念中提到的“漏”就是指MOSFET的漏極。同理,開集電路中的“集”就是指三極管的集電極。開漏電路就是指以MOSFET的漏極為輸出的電路。一般的用法是會(huì)在漏極外部的電路添加上拉電阻。完整的開漏電路應(yīng)該由開漏器件和開漏上拉電阻組成。如圖1所示:

組成開漏形式的電路有以下幾個(gè)特點(diǎn):

1. 利用外部電路的驅(qū)動(dòng)能力,減少IC內(nèi)部的驅(qū)動(dòng)(或驅(qū)動(dòng)比芯片電源電壓高的負(fù)載)。當(dāng)IC內(nèi)部MOSFET導(dǎo)通時(shí),驅(qū)動(dòng)電流是從外部的VCC流經(jīng)R pull-up ,MOSFET到GND。IC內(nèi)部?jī)H需很下的柵極驅(qū)動(dòng)電流。如圖1。

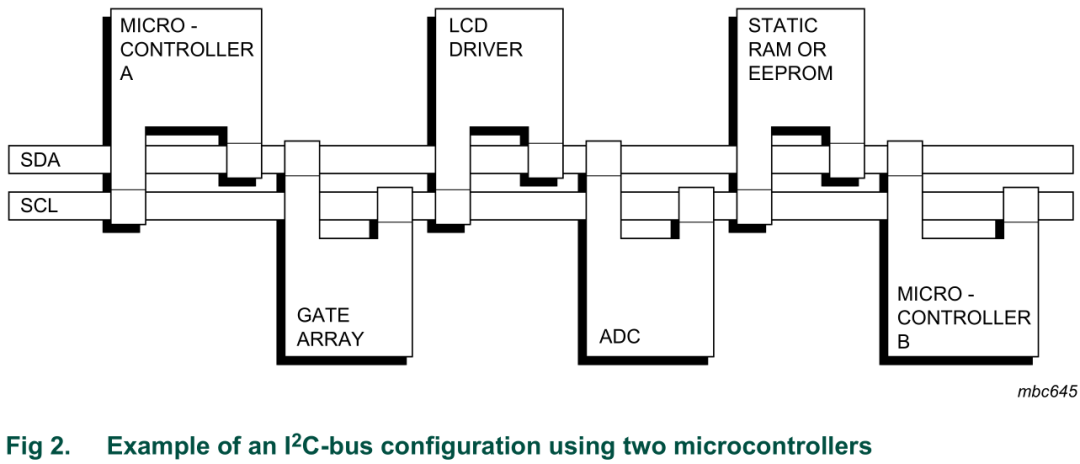

2. 可以將多個(gè)開漏輸出的Pin,連接到一條線上。形成 “與邏輯” 關(guān)系。如圖1,當(dāng)PIN_A、PIN_B、PIN_C任意一個(gè)變低后,開漏線上的邏輯就為0了。這也是I2C,SMBus等總線判斷總線占用狀態(tài)的原理。如果作為輸出必須接上拉電阻。接容性負(fù)載時(shí),下降延是芯片內(nèi)的晶體管,是有源驅(qū)動(dòng),速度較快;上升延是無源的外接電阻,速度慢。如果要求速度高電阻選擇要小,功耗會(huì)大。所以負(fù)載電阻的選擇要兼顧功耗和速度。

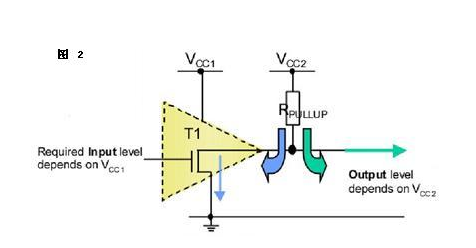

3. 可以利用改變上拉電源的電壓,改變傳輸電平。如圖2, IC的邏輯電平由電源Vcc1決定,而輸出高電平則由Vcc2(上拉電阻的電源電壓)決定。這樣我們就可以用低電平邏輯控制輸出高電平邏輯了(這樣你就可以進(jìn)行任意電平的轉(zhuǎn)換)。(例如加上上拉電阻就可以提供TTL/CMOS電平輸出等。)

4. 開漏Pin不連接外部的上拉電阻,則只能輸出低電平(因此對(duì)于經(jīng)典的51單片機(jī)的P0口而言,要想做輸入輸出功能必須加外部上拉電阻,否則無法輸出高電平邏輯)。一般來說,開漏是用來連接不同電平的器件,匹配電平用的。

5. 標(biāo)準(zhǔn)的開漏腳一般只有輸出的能力。添加其它的判斷電路,才能具備雙向輸入、輸出的能力。

6.正常的CMOS輸出級(jí)是上、下兩個(gè)管子,把上面的管子去掉就是OPEN-DRAIN了。這種輸出的主要目的有兩個(gè):電平轉(zhuǎn)換、線與。

7.線與功能主要用于有多個(gè)電路對(duì)同一信號(hào)進(jìn)行拉低操作的場(chǎng)合,如果本電路不想拉低,就輸出高電平,因?yàn)镺PEN-DRAIN上面的管子被拿掉,高電平是靠外接的上拉電阻實(shí)現(xiàn)的。(而正常的CMOS輸出級(jí),如果出現(xiàn)一個(gè)輸出為高另外一個(gè)為低時(shí),等于電源短路。)

8.OPEN-DRAIN提供了靈活的輸出方式,但是也有其弱點(diǎn),就是帶來上升沿的延時(shí)。因?yàn)樯仙厥峭ㄟ^外接上拉無源電阻對(duì)負(fù)載充電,所以當(dāng)電阻選擇小時(shí)延時(shí)就小,但功耗大;反之延時(shí)大功耗小。所以如果對(duì)延時(shí)有要求,則建議用下降沿輸出。

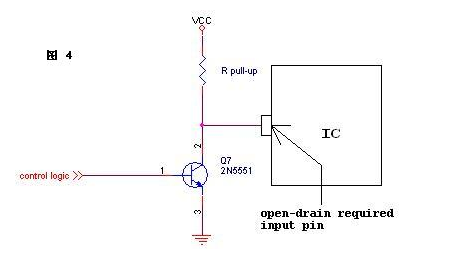

應(yīng)用中需注意: 1. 開漏和開集的原理類似,在許多應(yīng)用中我們利用開集電路代替開漏電路。例如,某輸入Pin要求由開漏電路驅(qū)動(dòng)。則我們常見的驅(qū)動(dòng)方式是利用一個(gè)三極管組成開集電路來驅(qū)動(dòng)它,即方便又節(jié)省成本。如圖4。

2. 上拉電阻R pull-up的阻值決定了邏輯電平轉(zhuǎn)換的沿的速度。阻值越大,速度越低功耗越小。反之亦然。

Push-Pull輸出就是一般所說的推挽輸出,在CMOS電路里面應(yīng)該較CMOS輸出更合適,因?yàn)樵贑MOS里面的push-pull輸出能力不可能做得雙極那么大。輸出能力看IC內(nèi)部輸出極N管P管的面積。和開漏輸出相比,push-pull的高低電平由IC的電源低定,不能簡(jiǎn)單的做邏輯操作等。push-pull是現(xiàn)在CMOS電路里面用得最多的輸出級(jí)設(shè)計(jì)方式。

當(dāng)然open drain也不是沒有代價(jià),這就是輸出的驅(qū)動(dòng)能力很差。輸出的驅(qū)動(dòng)能力很差的說法不準(zhǔn)確,驅(qū)動(dòng)能力取決于IC中的末級(jí)晶體管功率。OD只是帶來上升沿的延時(shí),因?yàn)樯仙厥峭ㄟ^外接上拉無源電阻對(duì)負(fù)載充電的,當(dāng)電阻選擇小時(shí)延時(shí)就小、但功耗大,反之延時(shí)大功耗小。OPEN DRAIN提供了靈活的輸出方式,但也是有代價(jià)的,如果對(duì)延時(shí)有要求,建議用下降沿輸出。

電阻小延時(shí)小的前提條件是電阻選擇的原則應(yīng)在末級(jí)晶體管功耗允許范圍內(nèi),有經(jīng)驗(yàn)的設(shè)計(jì)者在使用邏輯芯片時(shí),不會(huì)選擇1歐姆的電阻作為上拉電阻。在脈沖的上升沿電源通過上拉無源電阻對(duì)負(fù)載充電,顯然電阻越小上升時(shí)間越短,在脈沖的下降沿,除了負(fù)載通過有源晶體管放電外,電源也通過上拉電阻和導(dǎo)通的晶體管對(duì)地 形成通路,帶來的問題是芯片的功耗和耗電問題。電阻影響上升沿,不影響下降沿。如果使用中不關(guān)心上升沿,上拉電阻就可選擇盡可能的大點(diǎn),以減少對(duì)地通路的 電流。如果對(duì)上升沿時(shí)間要求較高,電阻大小的選擇應(yīng)以芯片功耗為參考。

推挽電路組成結(jié)構(gòu)

如果輸出級(jí)的有兩個(gè)三極管,始終處于一個(gè)導(dǎo)通、一個(gè)截止的狀態(tài),也就是兩個(gè)三級(jí)管推挽相連,這樣的電路結(jié)構(gòu)稱為推拉式電路或圖騰柱(Totem-pole)輸出電路。

當(dāng)輸出低電平時(shí),也就是下級(jí)負(fù)載門輸入低電平時(shí),輸出端的電流將是下級(jí)門灌入T4;當(dāng)輸出高電平時(shí),也就是下級(jí)負(fù)載門輸入高電平時(shí),輸出端的電流將是下級(jí)門從本級(jí)電源經(jīng) T3、D1 拉出。這樣一來,輸出高低電平時(shí),T3 一路和 T4 一路將交替工作,從而減低了功耗,提高了每個(gè)管的承受能力。又由于不論走哪一路,管子導(dǎo)通電阻都很小,使 RC 常數(shù)很小,轉(zhuǎn)變速度很快。

因此,推拉式輸出級(jí)既提高電路的負(fù)載能力,又提高開關(guān)速度。 推挽結(jié)構(gòu)一般是指兩個(gè)三極管分別受兩互補(bǔ)信號(hào)的控制,總是在一個(gè)三極管導(dǎo)通的時(shí)候另一個(gè)截止。要實(shí)現(xiàn)線與需要用 OC(open collector)門電路。

電壓和電流

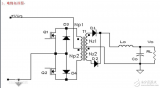

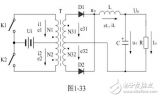

在圖(b)中的(1)所示的是圖(a)中功率變壓器Tr1的中心抽頭的波形,這種波形是因?yàn)殡娏鞣答侂姼蠰cf的存在及一個(gè)經(jīng)過全波整流后的正弦波在過零點(diǎn)時(shí)會(huì)降到零。因?yàn)長(zhǎng)cf的直流電阻可以忽略不計(jì),所以加在上面的直流電壓幾乎為零,在Lcf輸出端的電壓幾乎等于輸人端的電壓,即Udc。同時(shí)因?yàn)橐粋€(gè)全波整流后的正弦波的平均幅值等于Uac=Udc=(2/π)Up,則中心抽頭的電壓峰值為Up=(π/2)Udc。由于中心抽頭的電壓峰值出現(xiàn)于開關(guān)管導(dǎo)通時(shí)間的中點(diǎn),其大小為(π/2)Udc,因此另一個(gè)晶體管處于關(guān)斷狀態(tài)時(shí)承受的電壓為πUdc。

假設(shè)正常的交流輸入電壓有效值為120V,并假設(shè)有±15%的偏差,所以峰值電壓為1.41×1.15×120=195V。考慮到PFC電路能產(chǎn)生很好的可以調(diào)節(jié)的直流電壓,大約比輸入交流電壓高20V左右,就有Udc=195+20=215V。這樣晶體管要保證安全工作就必須能夠承受值為πUd。的關(guān)斷電壓,也就是675V的電壓。當(dāng)前有很多晶體管的額定值都可以滿足電流電壓和頻率ft的要求(如MJE18002和MJE18004,它們的Uce=1000V,ft=12MHz,β值最小為14)。即使晶體管的ft=4MHz也沒有關(guān)系,因?yàn)榫w管在關(guān)斷后反偏電壓的存在大大減小了它的存儲(chǔ)時(shí)間。

從圖中的(2)~(5)可以看出,晶體管電流在電壓的過零點(diǎn)處才會(huì)上升或下降,這樣可以減少開關(guān)管的開關(guān)損耗。因?yàn)橥ㄟ^初級(jí)的兩個(gè)繞組的正弦半波幅值相等,所以其伏秒數(shù)也是相等的,而且由于存儲(chǔ)時(shí)間可以忽略(見圖(b)中的(1)),也就不會(huì)產(chǎn)生磁通不平衡或瞬態(tài)同時(shí)導(dǎo)通的問題了。

每個(gè)半周期內(nèi)的集電極電流如圖中的(4)和(5)所示。在電流方

波脈沖頂部的正弦形狀特點(diǎn)將在下面說明。正弦形狀中點(diǎn)處為電流的平均值(Icav),它可以根據(jù)燈的功率計(jì)算出來。假設(shè)兩盞燈的功率均為P1,轉(zhuǎn)換器的效率為叩,輸人電壓為Udc,則集電極電流為

假設(shè)兩燈管都是40W,轉(zhuǎn)換器效率η為90%,從PFC電路得到的輸人電壓Udc為205V

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論