現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)都屬于大型可編程邏輯器件,十年前它們發(fā)明伊始是為了充當(dāng)膠合邏輯以及ASIC原型器件,但自出現(xiàn)后,它們的功能擴(kuò)展非常迅速。嵌入式加速器和微處理器應(yīng)用曾經(jīng)一度僅使用DSP和ASSP,但FPGA以及CPLD后來(lái)也成為了強(qiáng)有力的候選。一旦設(shè)計(jì)師了解FPGA和CPLD架構(gòu)的基礎(chǔ)知識(shí),就可以提升許多設(shè)計(jì)的性能、效率并縮短設(shè)計(jì)周期。

在演化到目前最新形態(tài)的FPGA和CPLD之前,可編程邏輯已經(jīng)有很長(zhǎng)的發(fā)展歷史。這兩種技術(shù)之間的體系結(jié)構(gòu)差別可由名稱(chēng)識(shí)別出來(lái)。FPGA結(jié)構(gòu)非常像ASIC門(mén)陣列,事實(shí)上,它最初用于ASIC原型。 CPLD則是一堆可編程邏輯元件的網(wǎng)絡(luò),這些元件連接起來(lái)可以創(chuàng)建一個(gè)更大的系統(tǒng)。

可編程邏輯基礎(chǔ)

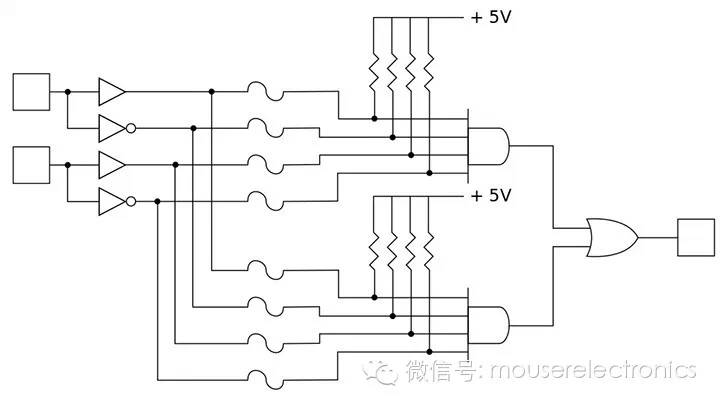

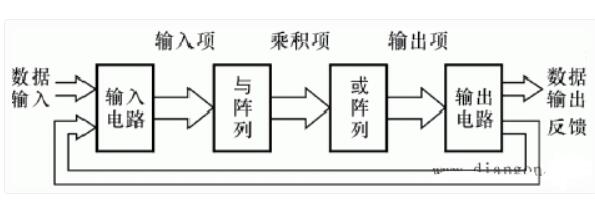

為理解FPGA和CPLD的基礎(chǔ)配置思路,可以重新回顧一下可編程陣列邏輯(PAL)的特性。PAL最初具備一個(gè)寬泛的可編程與(AND)門(mén)平面,可以對(duì)輸入進(jìn)入與操作。或(OR)平面是固定的,限制了可以一起進(jìn)行或操作的項(xiàng)數(shù)。也加入了一些基礎(chǔ)邏輯單元,比如多路復(fù)用器、異或和鎖存器,也包括一些時(shí)序單元,例如觸發(fā)器。

這些電路元件的組合幫助設(shè)計(jì)者實(shí)現(xiàn)大量的邏輯功能,包括狀態(tài)機(jī)需要的時(shí)鐘時(shí)序邏輯。PAL速度非常快,可以取代很多上一代設(shè)計(jì)中的標(biāo)準(zhǔn)邏輯。圖1顯示了一個(gè)基礎(chǔ)的PAL,其中的可編程元件(顯示為熔絲)將輸入信號(hào)的真值和互補(bǔ)值同時(shí)連接到圖中所示的與門(mén)。與門(mén),也被稱(chēng)為乘積項(xiàng),通過(guò)或運(yùn)算,形成乘積項(xiàng)之和的邏輯陣列。

圖1:簡(jiǎn)化的可編程陣列邏輯(PAL)

CPLD和FPGA在PAL和ASIC門(mén)陣列之間創(chuàng)造了一種妥善并且非常具有擴(kuò)展性的媒介。CPLD和PAL速度一樣快,但更為復(fù)雜。FPGA方法復(fù)雜性與門(mén)陣列接近但是可編程。

CPLD架構(gòu)

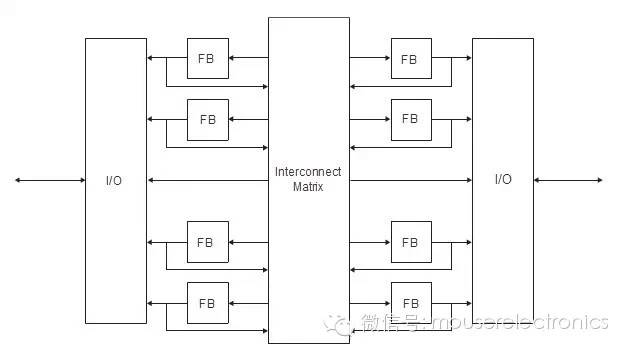

雖然每家CPLD廠商都有其獨(dú)特實(shí)現(xiàn),但所有CPLD具備一些共有特征,比如都擁有功能塊(FB)、輸入/輸出模塊(I / O)以及互連矩陣。 CPLD均通過(guò)使用特定制造商工藝對(duì)應(yīng)的元件編程。存儲(chǔ)器件可以是EPROM單元、EEPROM單元或Flash EPROM單元。圖2顯示了一個(gè)典型的CPLD架構(gòu)。

圖2:簡(jiǎn)化的CPLD架構(gòu)

FPGA架構(gòu)

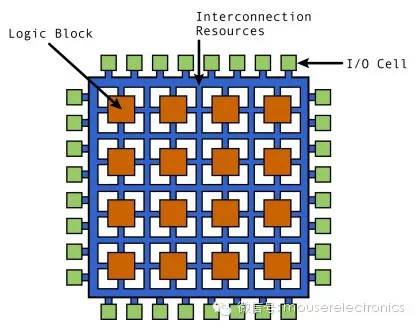

FPGA架構(gòu)與ASIC類(lèi)似,但與CPLD差異巨大。一個(gè)通用的FPGA架構(gòu)包括配置邏輯塊(CLB)陣列、I / O焊盤(pán)和可編程互連,如圖3所示。加入了時(shí)鐘電路以驅(qū)動(dòng)時(shí)鐘信號(hào)到每一個(gè)邏輯塊。算術(shù)邏輯單元、存儲(chǔ)單元和譯碼器也是典型的組件。

圖3:基礎(chǔ)FPGA架構(gòu)

FPGA邏輯蘊(yùn)藏在CLB中,CLB包含了RAM資源,可用于創(chuàng)建組合邏輯功能,這些功能也常稱(chēng)為查找表(LUT)。它還包含了觸發(fā)器,可用于時(shí)序存儲(chǔ)元件,還包含了多路復(fù)用器,以用于邏輯塊內(nèi)和外部資源之間的邏輯的布線。多路復(fù)用器還可用于極性選擇以及復(fù)位和清零輸入選擇。

可配置I / O塊包含帶有三態(tài)以及開(kāi)路輸出控制集合功能的一對(duì)輸入和輸出緩沖對(duì)。輸出的極性通常可編程為高有效或低有效輸出,并且輸出的壓擺率經(jīng)常也可以被編程為快或慢的上升和下降時(shí)間。輸入端和輸出端通常包含觸發(fā)器。在輸入端使用觸發(fā)器,這樣在到達(dá)觸發(fā)器之前就不會(huì)有太多時(shí)延,但將增加器件保持時(shí)間的要求。在輸出端,觸發(fā)器允許時(shí)序信號(hào)直接輸出到管腳,不會(huì)遇受顯著延遲問(wèn)題。

為避免信號(hào)延遲帶來(lái)的不利后果,互聯(lián)結(jié)構(gòu)最終呈現(xiàn)出層次化結(jié)構(gòu),在這種結(jié)構(gòu)中長(zhǎng)連線(它們也可以被用作總線)連接芯片中物理上遠(yuǎn)離的多個(gè)關(guān)鍵CLB。短連線連接彼此接近的多個(gè)獨(dú)立CLB。類(lèi)似于CPLD中的開(kāi)關(guān)矩陣,以特殊方式連接多條長(zhǎng)連線和短連線。芯片內(nèi)的可編程開(kāi)關(guān)使能CLB與互連線的連接,以及互連線彼此間的連接,還有互連線與開(kāi)關(guān)矩陣的連接。

利用三態(tài)緩沖器將多個(gè)CLB連接形成一個(gè)長(zhǎng)連線,多條長(zhǎng)連線就組成了總線。時(shí)鐘通過(guò)長(zhǎng)連線分布在整個(gè)FPGA中,這樣的長(zhǎng)連線稱(chēng)為全局時(shí)鐘線,專(zhuān)門(mén)面向低阻抗和快速傳播進(jìn)行了優(yōu)化。他們連接到時(shí)鐘緩沖器,以及連接到每個(gè)CLB中的時(shí)序元件。

-

復(fù)用器

+關(guān)注

關(guān)注

1文章

709瀏覽量

28361 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2002瀏覽量

61284 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

517瀏覽量

44139

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

可編程邏輯(PLD)的市場(chǎng)及優(yōu)點(diǎn)分析

什么是可編程邏輯

什么是可編程邏輯控制器?可編程邏輯控制器有哪些特點(diǎn)?

可編程邏輯器件基礎(chǔ)及應(yīng)用實(shí)驗(yàn)指導(dǎo)書(shū)

什么是PLD(可編程邏輯器件)

EDA技術(shù)與應(yīng)用(可編程邏輯器件)

關(guān)于可編程邏輯器件的分析和應(yīng)用

可編程陣列邏輯構(gòu)造_可編程邏輯器材的運(yùn)用

可編程邏輯控制繼電器

可編程邏輯器件測(cè)試

關(guān)于可編程邏輯推動(dòng)基于MCU的設(shè)計(jì)的分析和應(yīng)用

關(guān)于可編程邏輯推動(dòng)基于MCU的設(shè)計(jì)的分析和應(yīng)用

評(píng)論