采用CPLD市場領先供應商提供的MAX?II 開發套件,您可以評估MAX II CPLD的系列特性,或者開始對自己的設計進行原型開發。它包括參考設計(LCD控制器、PCI、USB和插槽)、演示設計、軟件、電纜以及確保快速方便的使用MAX II CPLD的所有附件。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

cpld

+關注

關注

32文章

1248瀏覽量

169518 -

控制器

+關注

關注

112文章

16434瀏覽量

178979 -

lcd

+關注

關注

34文章

4437瀏覽量

168073

發布評論請先 登錄

相關推薦

#硬聲創作季 #FPGA 玩轉FPGA-18 BJ-EPM240實驗11-MAX II內部震蕩時鐘使用實例-1

fpga時鐘發生器EPM實例epM240

水管工

發布于 :2022年10月29日 12:32:53

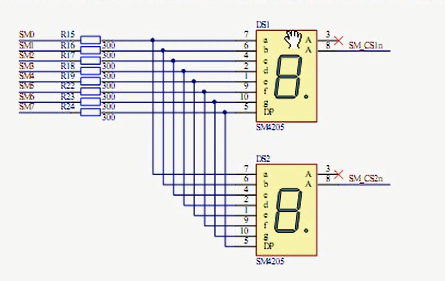

FPGA視頻教程之使用BJ-EPM240學習板進行數碼管顯示實驗的資料說明

本文檔的主要內容詳細介紹的是FPGA視頻教程之使用BJ-EPM240學習板進行數碼管顯示實驗的資料說明

發表于 02-28 10:35

?5次下載

FPGA視頻教程之BJ-EPM240學習板的詳細資料介紹

本文檔的主要內容詳細介紹的是FPGA視頻教程之BJ-EPM240學習板的詳細資料說明免費下載,BJ-EPM240學習

發表于 03-01 11:35

?21次下載

BJ-EPM240學習板介紹

主芯片使用的是Altera公司的MAXII系列EPM240T100C5,該芯片有240個邏輯單元,等效宏單元192個,資源比較豐富,內有8KbitFlash的存儲空間。

BJ-EPM240學習板之分頻計數實驗

這個實驗可以說是verilog入門最基礎的實驗了,我們不做太多的理論分析,實踐是硬道理。蜂鳴器與CPLD的接口如圖所示,當CPLD的1/0口(FM) 為低電平時,三極管截至,蜂鳴器不發聲;當CPLD的I/0 (FM)為高電平時,三極管導通,蜂鳴器發聲。

FPGA視頻教程:BJ-EPM240學習板-MAX II內部震動時鐘使用實驗

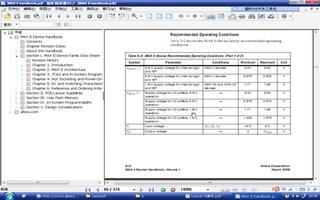

Altera的MAX? II 系列在所有CPLD系列中,其單位I/O引腳的功耗和成本都是最低的。MAX II CPLD支持高級功能集成,以降低系統設計成本。

FPGA視頻教程:BJ-EPM240學習板-MAX II的UFM模塊使用實驗

MAX II 器件屬于非易失、瞬時接通可編程邏輯系列,采用了業界突破性的 CPLD 體系結構。這種體系結構幫助您大大降低了系統功耗、體積和成本。

BJ-EPM240學習板:MAX II內部震動時鐘使用實驗

BJ-EPM240學習板:MAX II內部震動時鐘使用實驗

評論