了解如何輕松快捷地在設計周期中隨時完成一次性設計約束的導入,并且有信心自己的產品設計全程完全遵守這些約束。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

pcb

+關注

關注

4324文章

23158瀏覽量

399257 -

設計

+關注

關注

4文章

818瀏覽量

69926

發布評論請先 登錄

相關推薦

SOLIDWORKS高級BOM及屬性批量導入工具

SOLIDWORKS BOM插件-SolidKits.BOMs工具可以準確、規范、便捷的一鍵完成各種結構BOM導出,匯總BOM生成,批量導入屬性,自動建立結構,實現規范化管理,并自定義打包操作,還可根據企業需求定制模板.BOM工具試用/報價/購買,歡迎點擊咨詢Solidk

時序約束一主時鐘與生成時鐘

的輸出,對于Ultrascale和Ultrascale+系列的器件,定時器會自動地接入到GT的輸出。 1.2 約束設置格式 主時鐘約束使用命令create_clock進行創建,進入Timing

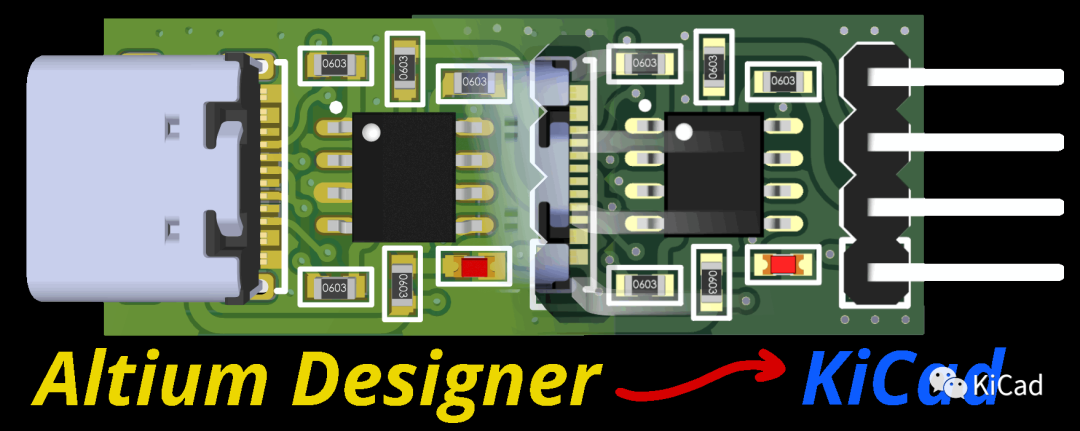

如何導入Altium Designer的原理圖和PCB?

“ ?KiCad可以支持直接導入Altium Designer的原理圖及PCB文件。與其它導入器不同,KiCad導入器可以直接導入源生的二進制文件(*.schdoc及*.pcbdoc)

常用時序約束使用說明-v1

為了節省每層導入網表的時間,在設置中我們通常不會勾選Aoto Load place and route Data 前面的勾選框。這樣每次編譯完成之后Show/Hide Tcl Command

AD畫完原理圖后如何導入PCB

完整無誤 : 在進行導入之前,請確保原理圖已經繪制完成,并且所有元件都已正確放置和連接。 檢查元件的封裝是否已分配,因為封裝是元件在PCB上的物理表示。 創建或打開PCB文件 : 如果尚未創建PCB文件,請在項目中新建一個PCB文件,并為其命名。 如果已經存在PCB文件,

Xilinx FPGA編程技巧之常用時序約束詳解

今天給大俠帶來Xilinx FPGA編程技巧之常用時序約束詳解,話不多說,上貨。

基本的約束方法

為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑以及異常路徑為

發表于 05-06 15:51

時序約束實操

添加約束的目的是為了告訴FPGA你的設計指標及運行情況。在上面的生成約束之后,在Result àxx.sdc中提供約束參考(請注意該文件不能直接添加到工程中,需要熱復制到別的指定目錄或者新建自己的SDC文件添加到工程)。

Xilinx FPGA的約束設置基礎

LOC約束是FPGA設計中最基本的布局約束和綜合約束,能夠定義基本設計單元在FPGA芯片中的位置,可實現絕對定位、范圍定位以及區域定位。

發表于 04-26 17:05

?1305次閱讀

Xilinx FPGA編程技巧之常用時序約束詳解

今天給大俠帶來Xilinx FPGA編程技巧之常用時序約束詳解,話不多說,上貨。

基本的約束方法為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑以及異常路徑為

發表于 04-12 17:39

如何快捷地完成設計約束的導入

如何快捷地完成設計約束的導入

評論