時序分析基礎(chǔ)

1. 時鐘相關(guān)

時鐘的時序特性主要分為抖動(Jitter)、偏移(Skew)、占空比失真(Duty Cycle DistorTIon)3點。對于低速設(shè)計,基本不用考慮這些特征;對于高速設(shè)計,由于時鐘本身的原因造成的時序問題很普遍,因此必須關(guān)注。

1. 時鐘抖動 (clock jitter)

理想的時鐘信號應(yīng)該是理想的方波,但是現(xiàn)實中的時鐘的邊沿變化不可能是瞬變的,它有個 從低到高 / 從高到低 的變化過程,如圖1所示。

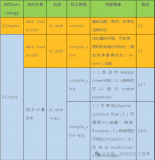

常見的抖動參數(shù)有3種:

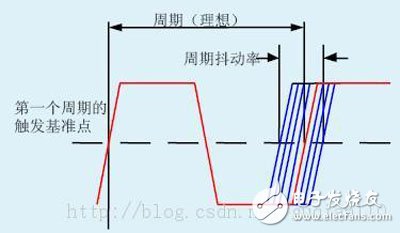

周期抖動(Period Jitter):

周期抖動率(Period Jitter)測量時鐘輸出傳輸偏離其理想位置的最大偏離。Period Jitter代表周期差抖動的上下邊界。

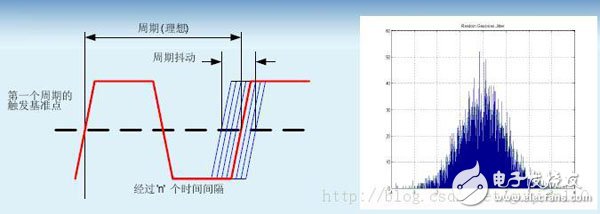

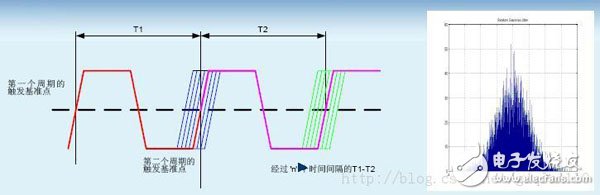

周期差抖動(cycle-to-cycle Jitter):

周期差抖動率(cycle-to-cycle jitter)是兩個相鄰周期的時間偏差。它總是小于周期抖動(period jitter)

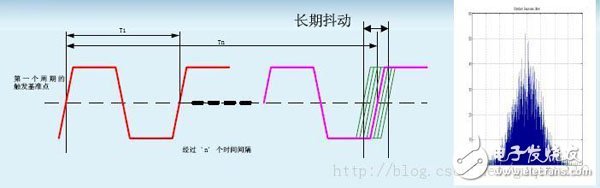

長期抖動(Long-term Jitter):

長期抖動率如下圖(Long-Term Jitter)定義為一個時鐘沿相對于基準周期時鐘沿經(jīng)過一段時間的延時之后,與其理想位置的偏離。此測量可以捕獲鎖相環(huán)低頻周期變化(緩慢的,頻率很低的)。長期抖動對圖形、串行連接通訊系統(tǒng)、打印機和任何光柵掃描操作非常重要。

時鐘抖動的原因就是噪聲。時鐘抖動是永遠存在的,當其大到可以和時鐘周期相比擬的時候,會影響到設(shè)計,這樣的抖動是不可接受的。

2. 時鐘偏斜 (clock skew)

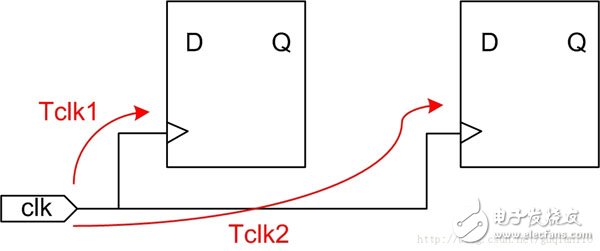

時鐘信號要提供給整個電路的時序單元,所以時鐘信號線非常長,并構(gòu)成分布式的RC網(wǎng)路。它的延時與時鐘線的長度、時序單元的負載電容、個數(shù)有關(guān),所以產(chǎn)生所謂的時鐘偏移。時鐘偏移是指同一個時鐘信號到達兩個不同的寄存器之間的時間差值,根據(jù)差值可以分為正偏移和負偏移。

時鐘偏移的計算公式: Tskew = Tclk2 - Tclk1

時鐘偏移是永遠存在的,當其大到一定程度會影響電路的時序。解決方法就是在FPGA的設(shè)計中讓主要的時鐘信號走全局時鐘網(wǎng)絡(luò)。該網(wǎng)絡(luò)采用全銅工藝和樹狀結(jié)構(gòu),并設(shè)計了專用時鐘緩沖和驅(qū)動網(wǎng)絡(luò),到所有的IO單元、CLB和塊RAM的偏移非常小,可以忽略不計。

3. 占空比失真DCD (Duty Cycle DistorTIon)

即時鐘不對稱,時鐘的脈沖寬度發(fā)生了變化。DCD會吞噬大量的時序裕量,造成數(shù)字信號的失真,使過零區(qū)間偏離理想的位置。DCD通常是由信號的上升沿和下降沿之間時序不同而造成的。

2. 信號扇入/扇出 (fan-in/fan-out)

The number of circuits that can be fed input signals from an output device. 扇出,輸出可從輸出設(shè)備輸入信號的電路的數(shù)量。

扇出(fan-out)是定義單個邏輯門能夠驅(qū)動的數(shù)字信號輸入最大量的術(shù)語。大多數(shù)TTL邏輯門能夠為10個其他數(shù)字門或驅(qū)動器提供信號。因而,一個典型的TTL邏輯門有10個扇出信號。

在一些數(shù)字系統(tǒng)中,必須有一個單一的TTL邏輯門來驅(qū)動10個以上的其他門或驅(qū)動器。這種情況下,被稱為緩沖器(buf)的驅(qū)動器可以用在TTL邏輯門與它必須驅(qū)動的多重驅(qū)動器之間。這種類型的緩沖器有25至30個扇出信號。邏輯反向器(也被稱為非門)在大多數(shù)數(shù)字電路中能夠輔助這一功能。

模塊的扇出是指模塊的直屬下層模塊的個數(shù)。一般認為,設(shè)計得好的系統(tǒng)平均扇出是3或4。一個模塊的扇出數(shù)過大或過小都不理想,過大比過小更嚴重。一般認為扇出的上限不超過7。扇出過大意味著管理模塊過于復雜,需要控制和協(xié)調(diào)過多的下級。解決的辦法是適當增加中間層次。一個模塊的扇入是指有多少個上級模塊調(diào)用它。扇人越大,表示該模塊被更多的上級模塊共享。這當然是我們所希望的。但是不能為了獲得高扇人而不惜代價,例如把彼此無關(guān)的功能湊在一起構(gòu)成一個模塊,雖然扇人數(shù)高了,但這樣的模塊內(nèi)聚程度必然低。這是我們應(yīng)避免的。

設(shè)計得好的系統(tǒng),上層模塊有較高的扇出,下層模塊有較高的扇人。其結(jié)構(gòu)圖像清真寺的塔,上面尖,中間寬,下面小。

3. launch edge

時序分析起點(launch edge):第一級寄存器數(shù)據(jù)變化的時鐘邊沿,也是靜態(tài)時序分析的起點。

4. latch edge

時序分析終點(latch edge):數(shù)據(jù)鎖存的時鐘邊沿,也是靜態(tài)時序分析的終點。

-

時序

+關(guān)注

關(guān)注

5文章

392瀏覽量

37390 -

時序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

22597

發(fā)布評論請先 登錄

相關(guān)推薦

使用機器學習改善庫特征提取的質(zhì)量和運行時間

ADS8412手冊第一頁寫到“0 to 1-MHz Sample Rate”,說明此芯片采樣率可調(diào),對嗎?

高密度Interposer封裝設(shè)計的SI分析

Verilog vhdl fpga

LM4811在啟動時或者shutdown開啟關(guān)閉過程中,增益控制跟預(yù)想的有偏差是為什么?

使用MXO58示波器輕松進行電源時序分析

時序分析基礎(chǔ)

時序分析基礎(chǔ)

評論