今天再啰嗦點玄學 - fpga的設(shè)計流程,因為“流程”我們學習任何一門技術(shù)都必須事先清楚的重要信息。

還是先劃一下重點 - 我們應(yīng)該學什么?想一下如果你要去駕校學開車,什么是你的重點?開車的一系列要領(lǐng)和技術(shù)還是你用來學習駕駛的車的按鈕的操作?顯然是前者,雖然市場上的車有幾十上百個不同的型號,多數(shù)的駕校都用桑塔納來當教練車,基于的前提就是所有的車支持你在路上行駛的功能(換擋、加速、剎車、后視鏡、方向盤)都是齊備的,主要的不同點在于這些功能按鈕擺放的位置不同。

因此當你要駕駛一輛從未摸過的車,你心里并不緊張,因為你已經(jīng)學會了駕駛,而且知道所有的車操作起來都大同小異,只要花5分鐘看一下說明書,熟悉一下各個功能的按鈕在哪里就可以上路了。

設(shè)計FPGA和畫PCB道理也是如此 - 我們要清楚地知道你需要掌握的技術(shù)是什么?運用這些技術(shù)需要的步驟、流程是什么?包括哪些環(huán)節(jié)?把這些搞清楚了,無論你用哪家的平臺、哪家的工具,就像換一輛不同品牌的車一樣都可以在簡單地對應(yīng)之后從容操作。

因此,要學習設(shè)計FPGA,第一件要做的事情就是FPGA設(shè)計和使用要經(jīng)歷哪些環(huán)節(jié)、流程?每個環(huán)節(jié)的注意事項是什么?

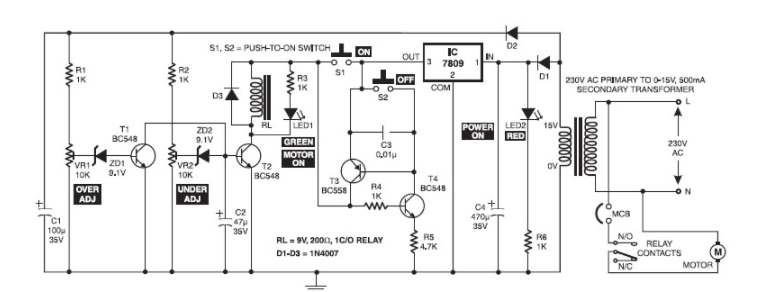

下面是一個簡單的FPGA設(shè)計Flow(流程)示意圖。

我們來看看每一步都要做什么事情:

設(shè)計定義:雖然貌似跟器件還沒打交道,這一步卻是整個過程中最重要的,它是將你的需求轉(zhuǎn)化為具體的邏輯功能實現(xiàn)的過程。比如你要設(shè)計一個交通燈的控制邏輯,我建議你去馬路邊蹲十分鐘,仔細觀察十字路口的交通燈的變化方式,用你自己的語言把每個狀態(tài)以及各個狀態(tài)之間的轉(zhuǎn)換方式、導致這些轉(zhuǎn)換的條件等描述清楚,將這些用筆在紙上畫出來,不漏掉任何一個細節(jié),做到這點,你的邏輯其實已經(jīng)出來了。后面的步驟都是工具要做的事情 - 將你腦子里的邏輯轉(zhuǎn)變成用FPGA芯片執(zhí)行的邏輯,并通過板子上的按鍵、LED指示燈等表現(xiàn)出來而已。復雜的任務(wù)就需要進行分解,就像你有一個團隊,團隊中的每一個角色承擔不同的職能,既要定義好每個角色的功能,又要定義好他們之間的關(guān)聯(lián)方式,也就是你需要將要實現(xiàn)的邏輯功能自上而下(Top Down)地分解為多個功能模塊(module),把每個模塊之間的接口信號及相應(yīng)的時序關(guān)系定義清楚;

告訴機器該怎么做:將你紙上畫好的邏輯關(guān)系用計算機工具軟件能夠理解的語言方式撰寫清楚,這個過程叫邏輯輸入,使用的方式可以是原理圖(最古老、直觀的方式)或者一些硬件描述語言 - Verilog、System Verilog、VHDL、System C等。在我們的教程中用的是Verilog這種硬件描述語言(HDL),做過PCB設(shè)計的同學肯定會覺得這個過程很類似繪制原理圖;

通過驗證確保機器的理解跟你想的一致:在用這些機器語言表述你的邏輯的時候你要確保機器理解的跟你自己理解的是一致的,如何才能做到這一點?我們聰明的工程師發(fā)明了“Simulation(仿真)”這么個過程,給出一些輸入條件,看機器理解的結(jié)果是不是如你預期的一樣,如果有出入,那就是你們之間的溝通有問題,也就是你用它的語言表述的不夠清晰、準確,你需要進行調(diào)整;類比PCB設(shè)計,這個過程類似你設(shè)計了一個模擬電路之后需要運行Spice工具對你設(shè)計的電路以及相應(yīng)的參數(shù)進行驗證一樣。很多人省去了這個過程,把風險留給了后面;

讓機器生成一個“它”理解的邏輯,這一步叫邏輯綜合,當然得到的結(jié)果是機器能夠理解的抽象的關(guān)系圖,基于這個關(guān)系圖機器就可以在下一步自動根據(jù)FPGA的內(nèi)部資源進行具體的功能分配了。到現(xiàn)在為止還沒有跟具體的FPGA器件發(fā)生任何關(guān)系,這就類似PCB設(shè)計中基于繪制的原理圖生成了Netlist一樣。

針對具體的FPGA器件進行資源分配 - 我們叫Implementation,也可以叫Place & Route(中文意思是布局布線,跟PCB中的過程類似)。這個過程就與你選用的哪家的器件、哪個類別的器件、哪個型號的器件,乃至哪個速度等級的器件都有關(guān)系了,在資源分配的過程中你一定要給出讓計算機分配資源的約束條件,除了你選用的具體的器件本身的資源限制以外,你要指定在邏輯中的哪個信號對應(yīng)在哪個管腳上,從一個管腳到另一個管腳之間的最大延時是多少等等,這就類似PCB布局布線的時候你一定要根據(jù)加工廠提供的需求設(shè)定每根走線的寬度、線間距、過孔的大小等design rule一樣。道理都是一致的,面對具體的器件,你不能隨心所欲。

每次完成布局布線,因為不同廠商的不同型號的器件其內(nèi)部的構(gòu)成架構(gòu)是不同的,因此需要再次驗證將你的邏輯映射到具體的器件的具體資源里面以后,它干的活是不是滿足你的要求,不僅要求其實現(xiàn)你需要的功能,更要要求其滿足你要求的性能,也就是說內(nèi)部的這些功能塊乃至每個門之間的時序配合要滿足你的要求,否則在實際的系統(tǒng)中就會出亂子的。這就像國慶閱兵,每個部隊在拉到長安街之前要經(jīng)過嚴格的演練,要做各種演習,驗證你的每一個環(huán)節(jié)都配合得天衣無縫。

一切都完美 - perfect,生成一個最高指示 - bit stream,發(fā)送到你選中的fpga芯片配置的PROM中,每次FPGA加上電以后就調(diào)用這些PROM中的最高指示,將其內(nèi)部的資源配置成最高指示想要的模樣,任勞任怨地干活唄。

這個流程清楚了吧?每家的FPGA都得遵循這個過程,無論是其中的貴族還是貧民,因為設(shè)計的規(guī)則都是一樣的。

還是那話,無論是Lattice的Diamond,Intel的Quartus,亦或是Xilinx的Vivado,都是“大同”的 - 都要具備這些功能,都要遵循這些流程,不同的就是有的搞得簡約一些,有得搞得華麗一些,每個按鈕點一點,每個輸出的結(jié)果看一看,就清楚他們之間的“小異”了。

不要再宣稱我只會用Xilinx的Vivado、我只會用Altium的AD,這只能說明你沒有真正掌握設(shè)計的核心。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21786瀏覽量

605061 -

機器

+關(guān)注

關(guān)注

0文章

784瀏覽量

40772 -

機器語言

+關(guān)注

關(guān)注

0文章

35瀏覽量

10769

原文標題:從概念到FPGA邏輯實現(xiàn)的設(shè)計流程

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

氯離子結(jié)構(gòu)示意圖和鈉離子結(jié)構(gòu)示意圖

一個簡單的FPGA設(shè)計Flow流程示意圖

一個簡單的FPGA設(shè)計Flow流程示意圖

評論