1 引言

高速數據采集系統(tǒng)目前已在雷達、聲納、圖像處理、語音識別、通信、瞬態(tài)信號測試等領域得到廣泛應用。它的關鍵技術是高速ADC技術、數據存儲與傳輸技術和抗干擾技術。當大量的高速實時數據經過模數轉換后,必須高速存儲,多通道高采樣率的數據采集系統(tǒng)會產生巨大的數據流。這樣就需要高速大容量的存儲板將數據存儲起來,然后再讀回計算機進行處理。基于以上原因,本文設計了可以同時存儲兩通道采樣數據的大容量存儲板,板中采用了64片Samsung公司的高速大容量存儲器K9F2G08UOM,使整塊板卡的存儲容量達到128Gbit。采用FPGA作為控制器,通過標準的CPCI工控機箱操作存儲板,并通過CPCI總線將存儲板上的數據高速讀回計算機,提高了讀取數據的速度。

2 K9F2G08UOM簡介

NOR Flash和NAND Flash是目前市場上的兩種主要的非易失性閃存技術,本設計的目的是為了高速存儲大容量的數據,因此,選擇NAND型K9F2G08U0M存儲器。它的存儲容量是2 Gbit,8位位寬,頁大小為2 048×8 bit,每塊由64頁組成,共有2 048塊。每頁帶有64×8 bit的空閑存儲區(qū),共有8 192 K×8 bit的空閑存儲區(qū)。頁編程的典型時間為300μs,最大頁編程時間為700μ8。頁內連續(xù)最小訪問時間為30 ns/Byte,即數據寫入Flash數據寄存器的速度可達33 MB/s。但是單頁數據的典型編程速度為2 048/300μs=6.8 MB/s,最慢的編程速度為2 048/700μs=2.9 MB/s。塊擦除的典型時間為2 ms。K9F2G08U0M具有硬件數據保護功能,即在電源上電、掉電期間關閉編程/擦除操作。K9F2G08U0M內部寫控制器使得所有的編程和擦除操作自動進行,片內包含一個頁(2 048+64字節(jié))的數據寄存器,讀寫過程中始終是將存儲單元數據或外部數據先緩存到數據寄存器,然后再讀出數據或寫入存儲單元。因此,它是基于頁讀寫,基于塊擦除的。當然,它也支持隨機讀寫。但本設計目的是高速存儲數據,因此對它的讀寫操作完全是基于頁的。K9F2G08U0M的主要引腳有CLE(命令鎖存允許)、ALE(地址鎖存允許)、CE(片選)、WE(寫允許)、RE(讀允許)、WP(寫保護)、R/B(準備好/忙)、PRE(上電讀使能)、I/O0~I/O7(輸入,輸出)。其中I/O0~I/O7既可作為數據輸入輸出引腳,又可作為命令地址的輸入引腳,命令、地址、數據分時復用,根據不同的命令區(qū)分地址和數據。一般的操作流程為:

1) 寫入命令,通知器件所要完成的操作(讀、寫、擦除等);

2) 寫入地址,即寫入要讀寫數據的起始地址,包括列地址和頁地址;

3) 如果是讀或者擦除,寫入一個確認命令。如果是寫操作,輸人待編程的數據,完成后輸入編程確認命令。

因為K9F2G08U0M共有128 K頁,每頁的大小為(2 048+64)×8 bit,所以在寫入地址時列地址需要12根地址線,頁地址需要17根地址線。這樣就需要5個時鐘周期來寫入地址。前兩個時鐘寫入列地址,后三個時鐘寫人頁地址。

3 系統(tǒng)設計

3.1 總體硬件設計

外部數據采集系統(tǒng)是2個40 MHz采樣的16位A/D通道,所以設計時分成兩個通道獨立設計。雖然K9F2G08U0M的數據寄存器寫入速度可達33MB/s,但在FPGA設計時,為了在時序上更加可靠,選擇使用25 MHz的時鐘設計,則K9F2G08U0M的寫入速度為50 MB/s(把兩個K9F2G08U0M并成16bit,寫入速度即為25 M×l6 b/s)。這樣,在FPGA內部開辟3個頁大小的雙口RAM作為緩存區(qū)就能滿足40 M×16 b/s的寫入速度,即在寫第2、3個RAM的時間(25 ns×2 048×2=102.4μs)內,啟動第1個RAM把數據寫入Flash的數據寄存器,所需時間為40 ns×2 048=81.92μs,小于102.4μs。

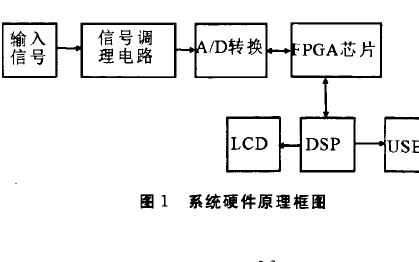

在讀回數據時,如以20 MHz讀取Flash,以40MHz讀出緩沖區(qū)中的數據,3個雙口RAM就能剛好滿足要求,如圖1。讀取K9F2G08U0M一頁數據能達到33 MHz的速度,為了讓讀寫Flash使用同一時鐘,讀Flash也采用25 MHz的速度。同時為了增加系統(tǒng)設計的冗余,采用4頁的雙口RAM作為緩沖區(qū)。所以每片F(xiàn)PGA內部至少需要4×2 048×16 bit=131 072 bit的存儲空間。

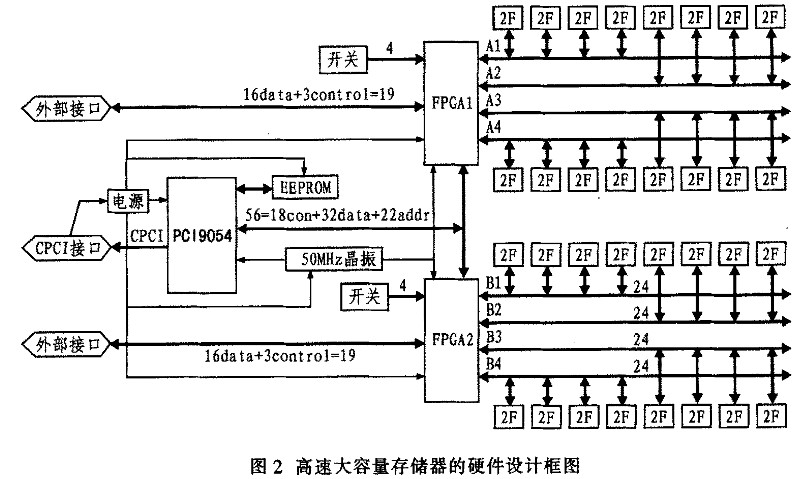

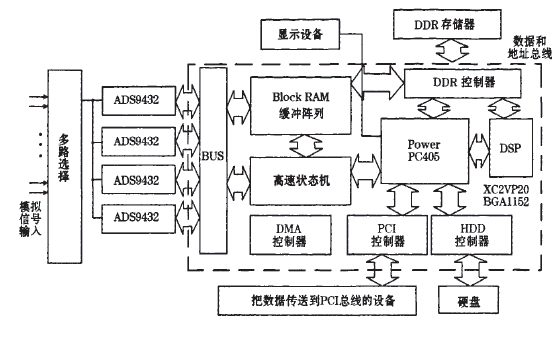

由于數據在寫入Flash后還有較長的編程時間,一頁的編程時間典型值為300μs,最大值為700μs。數據在存儲上不能有任何的停頓,否則就會丟失數據,所以不能使用R/B信號進行設計。為了系統(tǒng)更加可靠,選擇最大編程時間700μs。兩次對同一組Flash進行寫操作的時間間隔為700μs+81.92μs=781.92μs,一頁的數據寫到雙口RAM要用25ns×2 048=51.2μs。總時間除以寫一頁數據的時間:781.92/51.2=15.3μs,說明一個循環(huán)內至少需要16組Flash才能滿足要求。所以在設計中,對于每路A/D采樣通道都用一片F(xiàn)PGA作為緩沖和控制系統(tǒng),在每片F(xiàn)PGA內部都采用4個緩沖區(qū),每個緩沖區(qū)對應一條外部總線,每條總線上掛有4組K9F2G08U0M×2(將兩片F(xiàn)lash并成16位操作,即把I/O并成16位,共用控制信號線)。系統(tǒng)整體框圖如圖2所示。

圖2中2個外部接口連接2個A/D通道,采用兩片F(xiàn)PGA作為控制和緩沖區(qū),每片控制16組Flash。存儲板通過PCI9054與CPCI總線相連,通過CPCI總線可以將存儲板數據高速讀回計算機。

3.2 系統(tǒng)設計思想

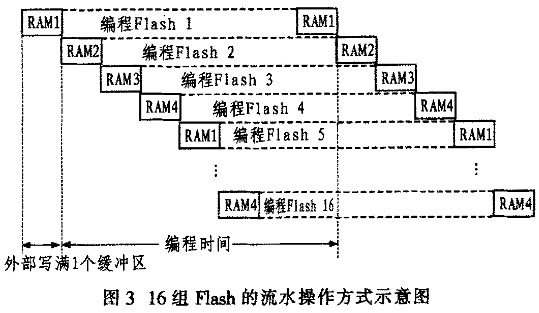

為了解決高速的數據采集和低速的Flash訪問速度之間的矛盾,采取將數據流串并轉換,復制多個操作模塊并行處理的設計方法。通過利用FPGA內部的存儲區(qū)實現(xiàn)4個雙口RAM作為緩沖區(qū)。每條外部Flash總線用一個雙口RAM,采集到的數據分時加載到4個RAM中,然后再寫入Flash。寫入Flash的操作以流水方式進行,具體方式如圖3所示。首先,外部A/D采樣通道寫數據到RAM1。當RAM1寫滿時,加載數據到第一組Flash數據寄存器,加載完成后第一組Flash進入自動編程階段;當RAM2寫滿時,第2組Flash加載開始,數據加載完成后,進入自動編程階段。依次加載RAM3,當RAM4寫滿,第4組Flash開始加載后,F(xiàn)PGA內部控制重新寫RAM1,開始對第5組Flash操作,然后依此循環(huán)方式對第6~16組Flash進行操作;當第16組數據加載完成后,第1組Flash已經編程結束,接著從第1組Flash開始加載和編程。可看出向16組Flash寫入數據是并行的,通過并行寫操作,可存儲高速采集的數據。

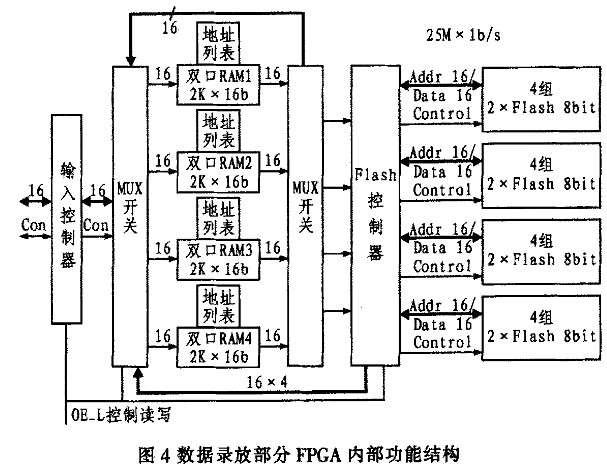

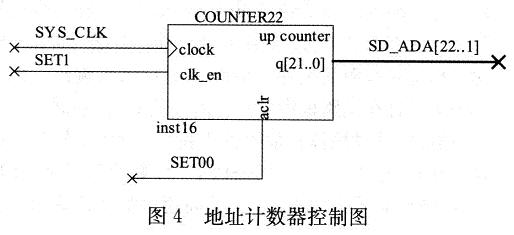

FPGA內部設計大體可劃分為PCI9054操控部分和數據錄放部分。PCI9054操控部分一方面跟PCI9054接口,一方面要完成對Flash的操作。數據錄放部分主要完成外部數據寫入、讀出以及擦除、建立無產塊信息列表等功能。由于對4組Flash的操作都是一樣的,所以數據錄放部分可以分為數據流控制部分和Flash操控部分。數據流控制部分控制數據寫入或讀取哪組Flash;Flash操控部分用于對Flash的具體操作。圖4為數據錄放部分FPGA功能結構。為了節(jié)省內部存儲單元的數量,寫入和讀取數據要使用同樣的緩存區(qū)。

3.3 無效塊的建立和操作

當一個塊中有一位或更多位不能正確操作時,就定義此塊為無效塊。無效塊并不影響其他塊的正常工作,各個塊之間是相互獨立的。所選的K9F2G08U0M在出廠時可能存在無效塊,在使用中也可能產生新的無效塊,但是器件的第一個塊一定不是無效塊。NAND Flash在出廠時就標記本身的無效塊,每個塊的第一頁或第二頁的空閑區(qū)的第一個數據不是FFh,則表示此塊為無效塊。為了保證Flash的正確操作,必須在操作之前建立無效塊信息表。在每片F(xiàn)PGA中設計了4個2 048×1 bit的RAM用于存儲無效塊的信息。RAM的每一個存儲單元存儲相應總線上的4組Flash的無效塊信息。其中某一塊的無效塊信息是4組Flash的無效塊信息相“與”后的結果(1表示正常,0表示無效塊)。在對Flash進行讀、寫或擦除操作之前,應先從RAM中讀取無效塊信息,然后根據無效塊信息決定是否對當前塊操作。

3.4 讀寫Flash操作

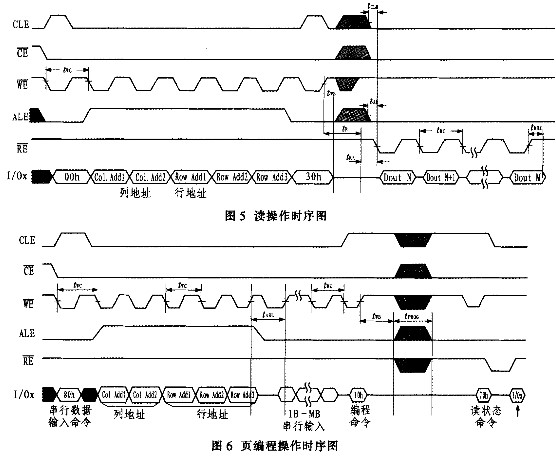

對Flash的讀寫操作都是基于頁的,讀寫操作的時序分別如圖5和圖6所示。計算機通過CPCI總線發(fā)送出讀或寫命令后,F(xiàn)PGA內部根據接收到的命令執(zhí)行相應操作。寫Flash時,外部采集的數據輸入RAM1,RAM1滿后,開始向RAM2寫入數據,同時選通第一條總線上第一組Flash的寫模塊,在寫模塊中通過計數器產生ALE、CLE、WE、RE等控制寫Flash的相應時序,將數據從RAM中編程到Flash內存,并令頁地址加1,依次循環(huán)(循環(huán)流程見圖3)。當總線上的第4組Flash的頁地址為64時,塊地址加1,并讀取無效塊信息,如果為無效塊,則屏蔽此塊,重新讀取下一塊信息,直至讀取到正常塊為止。如果是正常塊,則向此塊中寫入數據,同時將頁地址清零。讀操作與寫操作類似,只不過是將Flash中的數據讀出先送到RAM,然后依循環(huán)次序讀取RAM即可。

3.5 PCI9054操控部分的設計

通過編寫PCI9054專用的驅動和應用軟件,實現(xiàn)由計算機通過CPCI總線操控存儲板卡。在應用軟件中,對Flash讀寫或者擦除等命令自定義為對CPCI總線發(fā)送特定的數據。而在FPGA內部根據PCI9054發(fā)送的局部端數據線上的特定數據判斷是何種操作,并執(zhí)行相應操作。FPGA和PCI9054通信的主要信號線有LHOLD、LHOLDA、READY、ADS、ADDR、DATA,利用這些信號線可以實現(xiàn)PCI9054局部端和FPGA握手。將數據寫到計算機中。在PCI9054專用的驅動和應用軟件中,利用DMA方式讀取Flash,讀取速度可提高至1.3 MHz×16 bit。

4 結束語

本設計采用流水、并行處理技術,利用FPGA內部嵌入的存儲塊設計一組高速數據緩沖區(qū),使得多個慢速的存儲器件并行工作,令系統(tǒng)內外部數據的速率匹配,避免了外置高速緩存,簡化了硬件電路,且極大地提高了存儲數據的速率。大容量高密度閃存器件可使單片存儲板容量高達128 Gbit。在FP-GA內部設計中,建立Flash無效塊信息列表,并在此基礎上對Flash進行讀、寫、擦除及重建無效塊信息等操作。使系統(tǒng)具有集成度高、靈活性好、可移植性強、速度快等特點。通過CPCI總線采取DMA方式讀取,極大地提高了讀取速度。當接收到的數據帶寬很大,速度很高時,可將存儲板并聯(lián)起來,多個存儲板級聯(lián)可滿足更大的存儲容量需求,也可將級聯(lián)并聯(lián)二者結合起來以滿足不同系統(tǒng)的要求。整個系統(tǒng)基于CPCI工控機箱,更適合于野外的工作環(huán)境,并能及時保存、分析數據。

-

FPGA

+關注

關注

1630文章

21794瀏覽量

605146 -

控制器

+關注

關注

112文章

16442瀏覽量

179019 -

數據采集

+關注

關注

39文章

6243瀏覽量

113912

發(fā)布評論請先 登錄

相關推薦

基于ARM+FPGA的高速同步數據采集

高速大容量數據存儲技術

常見的幾種不同的高速數據采集存儲系統(tǒng)介紹

基于FPGA的高速數據采集系統(tǒng)該怎么設計?

如何利用FPGA實現(xiàn)高速連續(xù)數據采集系統(tǒng)設計?

高速數據采集系統(tǒng)中高速緩存與海量緩存的實現(xiàn)

大容量固態(tài)存儲設備的FPGA實現(xiàn)

采用FPGA的高速數據采集系統(tǒng)

單片機系統(tǒng)中高速數據采集的實現(xiàn)

基于SATA硬盤和FPGA的高速數據采集存儲系統(tǒng)

如何使用FPGA和DSP進行高速數據采集系統(tǒng)設計

如何使用FPGA設計高速實時數據采集存儲系統(tǒng)的資料概述

采用FPGA器件實現(xiàn)數據采集系統(tǒng)中高速大容量存儲板的設計

采用FPGA器件實現(xiàn)數據采集系統(tǒng)中高速大容量存儲板的設計

評論