1 引言

在現代航空通訊過程中,通訊信息量比較大,傳輸過程中容易出現諸多問題。在現有的磁帶記錄儀、數字處理專用機,動態參數記錄儀等設備,因技術、存儲容量、記錄速度、記錄的準確性等方面都有很大的缺陷和不足。為對存在于航空通訊的諸多問題,諸如通訊誤碼、中斷故障等做到及時掌握,查找原因,改進通訊質量,利用成熟的數字處理技術(DSP),基于TI 公司的TMS320F2812,設計了本通訊信息記錄系統。此通訊信息記錄系統主要包括信息管理、信息存儲、信息下載(后續開發)等部分組成。在設計過程中,主要使用到了CCS2000 開發工具和一些輔助試驗設備。DSP 是基于可編程超大規模集成電路和計算機技術發展起來的一門重要技術,可廣泛應用于通信控制、信號處理、儀器儀表、醫療、家電、軍事、工業檢測、控制及消費類產品。DSP 芯片的快速數據采集與處理功能以及片上集成的各種功能模塊為DSP 應用于各種場合提供了可能。在設計過程中,考慮到航空通訊的特殊要求,例如飛行時間,特殊的使用環境,及記錄設備與外界的鏈接,對存儲芯片都是一種特殊的要求,在以往的磁帶記錄儀、數字處理專用機等設備和器材中,一些體積大,存儲容量受限等因素利用DSP 可以得到很好的解決。

2 C2000 系列DSP 平臺及TMS320F2812 簡介

在系統開發過程中,需要一整套完整的軟硬件開發工具。利用TI公司推出的用于TM320系列DSP的軟件集成環境(IDE)。CCS工作在Windows操作系統下,類似于VC++的集成開發環境,采用圖形接口界面,提供編輯工具和管理工具。他將多種代碼產生工具匯編器,鏈接器,C/C++編譯器,建庫工具等集成在一個統一的開發平臺中,并且CCS具有開放式的架構,使TI和第三方能通過無縫插入附加專用工具來擴張IDE功能。CCS所集成的代碼調試工具具有各種調試功能,包括原TI公司提供的C/C++源代碼調試器和模擬器所具有的所有功能,他能對TMS320系列DSP進行指令級的仿真和可視化的實時數據分析。此外還提供了豐富的輸入、輸出庫函數,從而極大的方便了TMS320系列DSP的軟件開發過程。

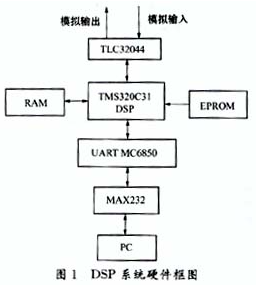

本文是基于DSP和FPGA為核心的,結合數模轉換電路、緩存器、FLASH存儲器等元器件,設計的通訊信息存儲記錄系統。TMS320F2812 是TI公司主推的一款高性能32位定點DSP 控制器。采用先進的體系結構,具有低功耗、運行速度快和片內資源豐富的特點,在數字控制領域有著廣泛的應用。它的主要特點有:

(1) 工作頻率高達150MHz(時鐘周期6.67ns),實時處理能力強,能應用于很多復雜的控制算法。

(2) 內含高性能32 位CPU,同時包含2個16 ×16位乘累加器,可以方便地運行16×16位和32×32的乘法累加操作,可滿足高精度與快速計算的要求。

(3)具有16 通道高性能12 位的帶流水線的模數轉換器(ADC),提供了兩個采樣保持電路,可以實現雙通道信號的同步采樣。

(4 )片上含兩個事件管理器(EVA 和EVB)可設計用于自身和FPGA的對通訊信息的管理控制等。

(5) 完善的外圍接口,包括1 個串行外圍接口(SPI)、2個串行通信接口(SCIs)、1個標準的UART 接口、1 個eCAN 接口和多通道緩沖串行接口(McBSP)等。

3 記錄系統硬件電路原理設計

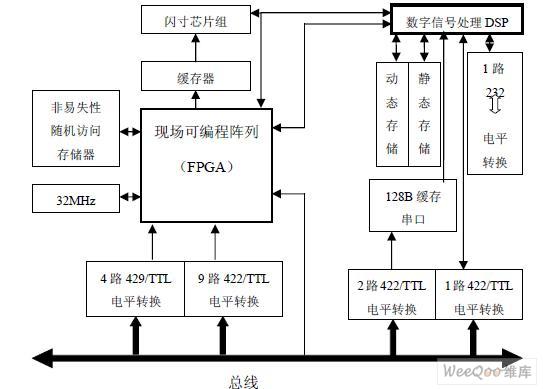

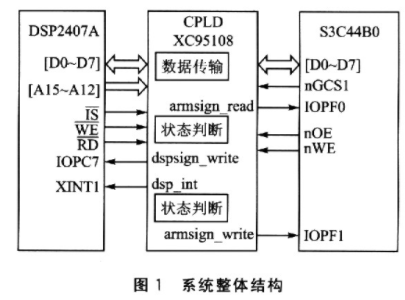

記錄系統中通信管理設備與顯示設備的2 路422 數據由DSP 負責接收、分析、組織并轉存至FLASH 芯片(使用3 片)中,其余9 路422 數據和4 路429 數據由FPGA 負責接收、組織并轉存。FPGA 共有4 個FLASH 接口,除了接口4 控制4 片FLASH 之外,每個接口控制3片FLASH。圖 1 是 系統的原理框圖。

圖 1 系統的原理框圖

當記錄系統處于工作狀態(GSE# = 0)時,FPGA 和DSP 接收各個通道的數據,進行緩存、組織和寫入(DSP 還要對接收到的數據進行分析,僅記錄控制字,如果是數據就直接丟棄)。為了能夠實現循環存儲并且在擦除舊數據時不丟失新的數據,每個通道的數據都組織為定長為64 字節的數據塊,其中第1 個字節為通道標識(因傳感器的通道比較多,設備繁雜在相應的通道加上通道標識),余下的63 字節為真實的數據和時標信息,這個定長數據塊是不可分割的,所有通道的數據按順序存儲到自身所在的FLASH 接口所控制的FLASH 芯片中,假定該接口有3 片FLASH 存儲器,使用第1 片存儲器時檢查第2 片存儲器是否可用,如果不可用,則向第2 片存儲器發送擦除命令;同理,使用第2 片存儲器時檢查第3 片存儲器是否可用,如果不可用,則向第3 片存儲器發送擦除命令;使用第3 片存儲器時檢查第1片存儲器是否可用,如果不可用,則向第1 片存儲器發送擦除命令;這樣就實現了循環存儲且保證丟掉的數據是最舊的數據。這樣的存儲方式要求有較大容量的緩存,在FPGA 內實現較為困難,因此使用外掛FIFO。

當記錄系統處于非空中工作狀態(GSE# = 1)時,DSP 通過422 接口與外圍主處理系統進行通信,如果需要獲取數據,DSP 首先獲得各接口當前存儲數據的具體空間,然后讀出數據進行解析。如果需要對數據進行擦除,對于自己管理的3 片FLASH,DSP 直接執行擦除命令,對于FPGA 管理的13 片FLASH,DSP 通過與FPGA 之間的命令接口執行擦除命令。共使用了16 片FIFO,1GB 容量均分到每個芯片,單芯片的容量需達到64M(512Mbit),這樣大容量的NOR 型FLASH 目前有AMD 公司的S29GL-P 系列和S70GL-N 系列,典型的寫數據速率為32B*106/(240+21)s ≈ 122.6KB/s,但目前考慮到貨源問題,無法做到系統設備的大批量生產,因此采用管腳兼容的AM29LV256M,總容量為512MB。

1 時鐘:記錄模塊使用了三種時鐘,其頻率分別是33MHz、7.3728MHz 和30MHz,33MHz時鐘提供給FPGA 內部邏輯使用,可分頻產生毫秒計數時鐘和429 總線用時鐘。

2 復位電路:記錄模塊復位包括上電復位、外部復位及DSP 復位。任意復位信號有效時均能復位整個模塊,除了FLASH 芯片,FIFO 芯片和DSP 之外,無其它資源需要在復位時處于特定狀態,因此只需考慮對FPGA 內部邏輯和DSP、FLASH 芯片的復位。如圖2 復位電路示意圖。

圖 2 復位電路示意圖

3 模塊電壓:記錄模塊使用7 種電壓,+/-12V、5V、 3.3V、1.8V、1.9V 和2.5V。

4 看門狗電路:DSP內部包含看門狗定時器,可通過軟件設置超時周期,并提供了使能/禁止看門狗的功能。

5 電平轉換:429電平轉換芯片使用2片HOLT公司的HI-8482雙通道接收器,422電平轉換芯片使用3片MAXIM公司的MAX309*通道接收器和1片MAXIM公司的MAX3491四通道發送器。

其中429電平轉換后的5V信號不能直接接入FPGA,需要用兼容3.3V/5V工作電壓的驅動器進行隔離。

6 FIFO:用于緩存接收到的數據,選用IDT 公司的IDT72V05,單片容量為8K*8。每個FLASH 接口需要2 片,共需8 片。

7 NVSRAM:NVSRAM 用于保存FLASH 存儲空間的起始地址和結束地址,保證在下電后該信息不丟失,選用SIMTEK 公司的STK14C88-3。容量為32K*8bit。

8 FPGA:FPGA 的功能是將接收到的4 路429 和9 路422 數據分別緩存,分別寫入。每隔10ms 時標生成插入單元會給緩存隊列插入相對時標,在軟件解析時,結合GPS 通道傳送的日歷時間可還原出各通道各數據包的絕對時間(精度為10ms)。

9 地址空間分配:TMS320F2812 通過其外部擴展接口訪問外擴RAM 和FPGA 內部寄存器及FLASH 空間,該外部接口映射到5 個獨立的存儲空間,當訪問相應的存儲空間時,會產生一個片選信號;每個空間都可以獨立地設置訪問建立、激活及跟蹤時間。還可以使用XREADY信號來控制外設的訪問。記錄模塊各單元所在存儲空間分配依據要求進行分配。

4 記錄系統軟件設計

根據通訊協議、全雙工通信方式、通信速率(115.2 Kbps)、傳輸數據格式以及數據包結構。數據包結構如下表:

其中,數據類型用以標識信令的種類;數據長度為轉義前消息數據與校驗和字節的總數;校驗和為消息中不含開始與結束標志的其余字節的CRC 校驗,占2 個字節,CRC 算法按定義;數據流向從左至右發送數據包的每個字節,每一個字節從低位至高位發送。如:C0 的發送順序為:0,0,0,0,0,0,1,1。

通信協議:SLIP 是一個簡單的面向字符的協議。在每個用戶信息幀的首尾各加-個特殊的標志字節 END ,封裝成為 SLIP 幀。標識字節 END 的編碼為(C0H)。若用戶信息幀中的某一個字節與(C0H)一樣,那么將這一個字節更換成(DBH, DCH)。這里的特殊字符(DBH)稱為SLIP 轉義字符。若用戶信息幀中的某個字節與(DBH)一樣,那么將這一個字節再更換成(DBH, DDH)。嚴格按照應用軟件的開發流程,結合信息在記錄設備中的傳輸,開發軟件,并對各種需求功能就行開發.開發的部分源程序:

5 創新點

首次采用TMS320F2812 結合AM29LV256M,采用的是現今國內最大的記錄芯片,設計航空通信信息記錄系統,實現了對通訊數據的實時記錄,設計出的記錄系統性能穩定,可靠性高,存儲量更大,記錄時間更長,經第三方驗證,通過對容錯能力的實驗,錯誤率低于標準要求。首次完成了在航空通訊領域原始數據問題紀錄的空白。在存儲芯片的選擇上,隨著技術的發展和改善,這一系統將得到完善和發展。設計基本達到了預期要求,滿足了需求,并在航空通訊裝備建設中得到了批量運用,產生的經濟效益巨大。

-

dsp

+關注

關注

554文章

8059瀏覽量

349774 -

FPGA

+關注

關注

1630文章

21785瀏覽量

605051 -

芯片

+關注

關注

456文章

51119瀏覽量

426007 -

編譯器

+關注

關注

1文章

1642瀏覽量

49224

發布評論請先 登錄

相關推薦

FPGA與DSP的高速通信接口設計與實現

采用CAN總線與RS-485實現DSP通信接口

FPGA與DSP的高速通信接口設計與實現

采用DSP實現網絡通信接口設計

采用DSP實現網絡通信接口設計

通過FPGA實現溫控電路接口及其與DSP通信接口的設計

航空總線接口通信系統的設計與實現

航空圖像壓縮系統的DSP設計方案解析

DSP系統程序遠程更新的研究與實現

基于TMS320F2812 DSP芯片的航空電源穩定性自我測試診斷方案

采用DSP芯片實現航空通信記錄系統的設計

采用DSP芯片實現航空通信記錄系統的設計

評論