1、 引言

4X2.5G線路接口卡是T比特路由器的一種重要接口,屬于高密度線路接口,這種接口是當前路由器設計中的一個重點和難點。所謂高密度,指的是在一塊繞路接口卡上提供多個接口。之所以出現高密度線路接口的需求,是因為互聯網的規模不斷的擴大,對路由器的接入能力提出了日益增大的需求,如果還沿用單板單接口的設計方法將導致路由器的物理規模不斷的擴大,不符合現代設備發展的趨勢。在4X2.5G線路接口卡的設計中,采用單片多路的SDH處理芯片S19202集中完成物理層的處理,然后根據整體設計方案在其后端進行數據的技術處理。

針對多路報文在送往轉發單元時的公平性和穩定性需求,以及SDH芯片S19202的特點,提出了輸入報文合路采用分片輪詢(Cell Round Robin Scheduling;CRR)和改進的欠賬式輪詢調度(Defect Round Robin Scheduling;DRR)相結合的調度策略。這種調度策略保證了4路POS接口之間的公平性和整包處理的穩定性,并且在工程上易于實現。本文第2節詳細闡述了該調度策略的設計與實現過程,第3節對全文進行了總結。

2、 輪詢調度的設計與實現

在4X2.5G線路接口卡的設計中,采用了AMCC公司的SDH處理芯片S19202進行鏈路層數據處理,該芯片的特點是4個接口共享同一組接收總線和同一組發送總線,另外提供通道選擇信號來指示當前工作的線路接口號,其輸入端每個接口的緩存大小最大只有1k字節,根本不足以緩存一個長的整包(最長包可達到1500字節)。

針對這個特點,設計中使用了在S19202后端的FPGA進行分片輪詢和整包接收的處理,保證了4個接口的公平性和穩定性;針對4個接口的報文共享一條到轉發的通路時,由于各接口的報文長度差異,可能造成的不公平和不穩定,提出了一種改進式欠賬輪詢的調度策略。通過分片輪詢和改進式欠賬輪詢的結合使用,保證了4個接口合路的公平性和穩定性。

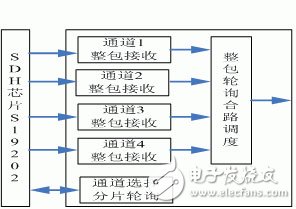

圖1 輸入合路模塊中的輪詢調度策略

輸入合路模塊中聯合調度策略的原理如圖1所示,對SDH芯片S19202送出的4路數據進行分片逐個輪詢,并緩存進相應通道的整包接收FIFO,相應通道若沒有數據則輪空,轉入下一通道;整包輪詢合路調度則逐個輪詢4個整包FIFO,若該FIFO有整包,則在每一輪詢周期發送一個整包,否則輪空。

在該聯合調度策略中,分片輪詢調度比較容易實現,僅需在FPGA實現的最前端設計一個輪詢機,利用SDH芯片S19202提供的通道指示信號(在FPGA設計用SRX_CHANNEL表示)對每個通道進行固定的輪詢訪問,有數據則存入相應的通道整包接收FIFO即可。而整包調度是使每個通道得到服務的公平性和穩定性的關鍵,它直接決定著接收服務的通道所得到的服務帶寬、時延以及時延抖動等性能指標,因此本文把研究重點放在了整包調度的設計與實現上。

目前,在整包調度上,主要的調度算法有先到先服務(FCFS)、逐包調度(PRR)、公平排隊、虛時鐘、加權循環服務(WRR)等多種策略。由于多數調度方式在包長不定的IP網絡中實現時遇到了困難,為此,M.Sheedhar等提出了適用于IP網絡的欠帳式循環調度(DRR),該算法由于其較低的實現復雜度、良好的公平性及穩定性而被經常采用。

但是,DDR算法直接用于高密度線卡設計中會有一定的問題。首先,DRR算法是針對集成服務網絡中不同業務需求而提出的,在一般應用中由于隊列數較多,所以需要減小隊列數,而在我們的設計中只有4個隊列,所以不需要減小隊列數;其次,在線卡設計中合路報文的包長無法直接給出,如果一定要加上包長則需用多加一級緩存,這就增大了設計復雜度也提高了成本;同樣由于經典DDR算法嚴格要求儲蓄計數器值大于隊頭包長才輸出,這種不允許帶寬透支只允許盈余的要求會導致出現有包但是無法輸出的現象。

根據4X2.5G線路接口的實際情況和DDR算法的思想,我們可以給出如下適合高密度POS接口使用的改進式欠賬式循環調度策略:

1) 逐包輪詢;

采用這種改進的DRR算法下,可以保證在變長包的情況下,各個接口的整包緩存隊列在報文合路時公平的帶寬,確保合路調度的穩定運行。

DRR整包輪詢合路的基本工作過程為:輪詢4個整包緩存隊列,每讀取一個整包都判斷該包是否是協議包,如果是協議包,則按照上交CPU報文格式送協議FIFO,如果是需要轉發的報文,則按照轉發報文格式送數據報文FIFO。

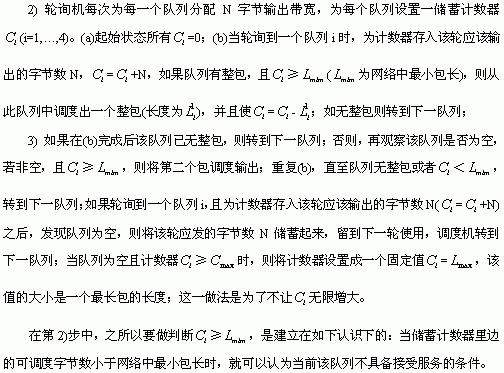

調度機輪詢到某個隊列時,為該隊列的儲蓄計數器加上40;然后判斷該隊列是否為空,如果為空,則馬上轉向下一個隊列;如果非空,則判斷當前該隊列是否有整包,如果當前該隊列無整包,則轉到下一個隊列;否則,如果該隊列目前有整包則輸出該隊列的隊頭包到合路隊列,同時該路的儲蓄計數器的值要減去輸出報文的長度;然后重復上述過程,直到該隊列無整包或者隊列的儲蓄計數器的值小于40時跳轉到下一隊列服務,其詳細工作流程如圖2 所示:

圖2 改進的DRR合路調度流程圖

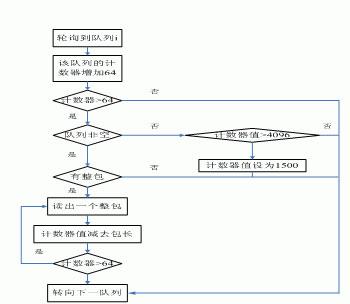

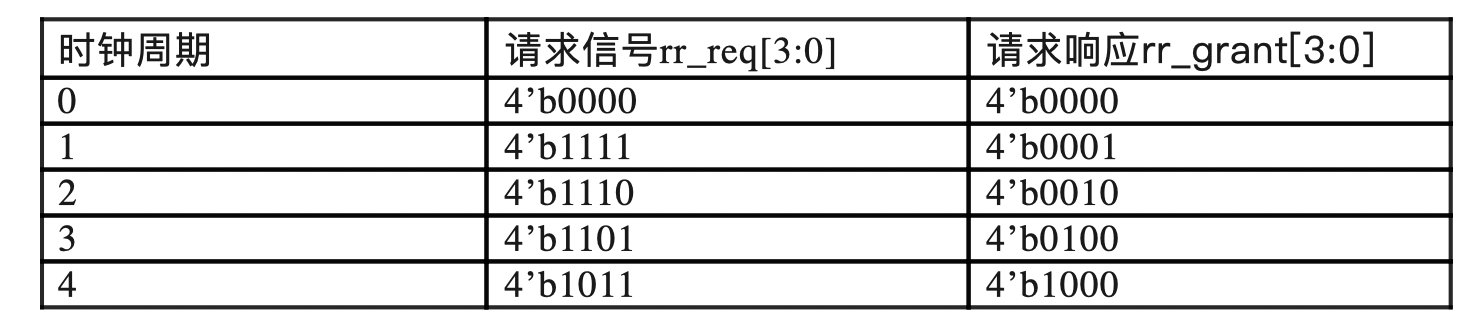

DRR合路調度單元已在ALTERA公司的quartusII4.1環境下用VHDL編程實現,其仿真波形如圖3所示:

圖3 DRR合路調度單元仿真波形圖

仿真結果顯示這種采用分片輪詢和欠賬輪詢的結合的合路調度策略設計可以達到性能需求,確保變長分組合路調度的公平性和穩定性。

3、 結束語

根據SDH芯片的S19202的特點和性能要求,通過在FPGA內部編程實現分片輪詢和改進式欠賬輪詢結合的調度策略,保證了4X2.5G線路接口卡輸入端各個接口合路的公平性和穩定性。經測試該設計性能穩定,整個工作流程簡單實用,符合設計要求。

-

FPGA

+關注

關注

1630文章

21786瀏覽量

605071 -

芯片

+關注

關注

456文章

51121瀏覽量

426083 -

計數器

+關注

關注

32文章

2259瀏覽量

94868

發布評論請先 登錄

相關推薦

IC設計:Verilog是如何實現RR輪詢調度的?

FPGA實現原理

請問FreeRTOS是如何實現調度的?

Microchip單片機固定時間片輪詢調度匯編代碼 精選資料分享

Microchip單片機固定時間片輪詢調度匯編代碼 精選資料推薦

通過對stm32內部的flash的讀寫可以實現對stm32的編程操作

調度器的原理及其任務調度代碼實現

基于FPGA的輪詢合路的設計和實現

PYNQ就是通過Python語言直接對FPGA進行編程嗎

基于完全服務輪詢機制MAC協議的FPGA設計

通過FPGA內部編程實現輪詢調度的設計

通過FPGA內部編程實現輪詢調度的設計

評論