片上系統(tǒng)(SoC)需要在單個硅片上實現(xiàn)模/數(shù)混合集成。與數(shù)字系統(tǒng)工藝兼容、功耗、面積等指標優(yōu)化的高性能模/數(shù)轉(zhuǎn)換器(Analog to Digital Converters,ADC)是片上系統(tǒng)中非常重要的單元,它實現(xiàn)了模擬電路與數(shù)字電路之間的聯(lián)系。流水線結(jié)構(gòu)模/數(shù)轉(zhuǎn)換器(Pipelined ADC)是一種研究和應用非常廣泛的模/數(shù)轉(zhuǎn)換器,其結(jié)構(gòu)本身并非屬于基本模/數(shù)轉(zhuǎn)換器結(jié)構(gòu),但在精度、速度及功耗方面相對于其他類型都有很大的改進,是高速高精度領域的主要應用類型之一。本文介紹了流水線A/D轉(zhuǎn)換器的基本原理,并構(gòu)造了一個三級流水線結(jié)構(gòu)的9位100 MSPS A/D轉(zhuǎn)換器(ADC),采用Zarlink 0.6μm互補雙極工藝模型對電路進行了模擬驗證。

1 三級流水線A/D轉(zhuǎn)換器電路設計

使用分級技術是解決高速高分辨率的一種方法。可以使用兩級或多級高速、低分辨率子ADC組合起來,形成一個高速高分辨率的流水線ADC。

1.1 三級流水線A/D轉(zhuǎn)換器工作原理

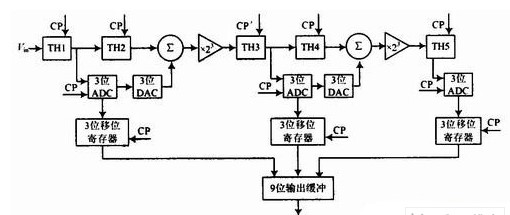

在基本A/D轉(zhuǎn)換結(jié)構(gòu)中,有些具備高速性能,有些具備高精度性能,沒有能夠同時達到高速高精度的要求。流水線ADC的出現(xiàn)在一定程度上解決了這個難題。流水線結(jié)構(gòu)可以在采樣速度和轉(zhuǎn)換精度之間取得較好的平衡。圖1是三級流水線ADC的結(jié)構(gòu)。

圖1 三級流水線ADC的結(jié)構(gòu)

由圖1可知,流水線結(jié)構(gòu)模/數(shù)轉(zhuǎn)換器主要是由采樣保持器、子ADC、子DAC及減法電路組成。輸入模擬信號首先送入第一個采保電路(TH 1),TH1的輸出信號輸出給第一個的子ADC(ADC1)和第二個采保電路(TH2),ADC1將輸入信號轉(zhuǎn)換得到高3位數(shù)字信號,該高3位數(shù)據(jù)通過DAC(DA C1)還原成模擬量,再將該模擬量和TH2的輸出一同輸入到減法電路,并將差值由放大器放大一定倍數(shù),便得到第一級模擬余量信號。此模擬余量將作為第二級轉(zhuǎn)換電路的輸入信號。重復上述步驟,得到次3位轉(zhuǎn)換數(shù)據(jù),依此類推。

設輸入信號為Vin,Vin通過3位ADC產(chǎn)生的數(shù)字量為Dm,3位DAC輸一模擬量為Vout,則Vin,Dm和Vout的關系由式(1)、(2)決定。

由式(2)可知,3位DAC還原得到的Vout小于等于輸入信號Vin,其差值就是包含低位數(shù)據(jù)位信息的模擬余量。為了使下一單元的ADC得到滿幅輸入,以降低對子ADC性能的要求,還需將此模擬余量乘以ADC量化單位的倒數(shù),即將此模擬余量放大23倍后再送給下一級子轉(zhuǎn)換器。

1.2 采樣保持電路的設計與分析

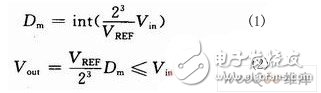

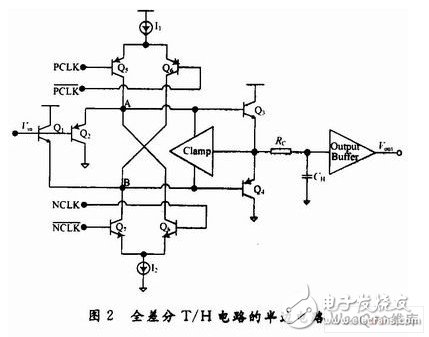

圖2為全差分采樣保持電路(T/H電路)的半邊電路;圖3為該T/H電路控制時鐘信號。

圖3 T/H電路控制時鐘信號

當PCLK和NCLK信號為低電平時,T/H電路工作在采樣模式,Q5,Q7導通,Q6,Q8截止,A節(jié)點電壓升高,B節(jié)點電壓降低,這時Q1~Q4均導通且工作在正向放大區(qū),它們形成一個AB類緩沖器驅(qū)動保持電容CH。該輸入電路結(jié)構(gòu)具有輸入偏置電流小、輸入阻抗高、交調(diào)失真小的特點。當PCLK和NCLK信號為高電平時,T/H電路工作在保持模式,Q5,Q7截止,Q6,Q8導通,鉗位電路(CLAMP)開始作用,使A節(jié)點電壓鉗位在VCH-VthN,使B結(jié)點的電壓鉗位在VCH+VthP(VthN和Vthp分別表示NPN管和PNP管的BE結(jié)導通屯壓),也使A,B兩節(jié)點呈現(xiàn)為低阻抗節(jié)點。此時Q1~Q4均截止,故而形成輸入信號與保持電容之間的二重隔離,消除保持模式的信號饋通。

RC和CH構(gòu)成一個低通濾波器,其截止頻率會隨負載而變化。為克服這一缺點,在輸出端設計一個輸出緩沖器。采樣/保持電路的噪聲特性主要來自于Q1~Q4的基極寄生電阻熱噪聲以及它們的散粒噪聲和帶寬限制電阻RC熱噪聲。電路設計時,選用大尺寸的器件來減小基極電阻Rb,使得基極寄生電阻熱噪聲最小化。將Q3,Q4偏置在較大的靜態(tài)電流來最小化它們的散粒噪聲,同時采樣模式動態(tài)特性也要求Q3,Q4有大的靜態(tài)電流,以減小VBE調(diào)制的影響。當該T/H電路被偏置在大電流時,它將有大的帶寬,因此必須串聯(lián)電阻RC來限制帶寬以濾除高頻噪聲。大的偏置電流也要在功耗和性能之間進行折衷考慮。

1.3 子ADC的設計與分析

折疊型結(jié)構(gòu)有比較器數(shù)量少、芯片復雜程度低、功耗較小的特點,具有較好的發(fā)展前景。將折疊結(jié)構(gòu)ADC應用于流水線(Pipeline)技術中,構(gòu)成流水線折疊式ADC,則可以提高其工作速度。折疊結(jié)構(gòu)ADC的比較器個數(shù)與其分辨率成線性比例關系。1個n位分辨率的折疊結(jié)構(gòu)ADC僅僅需要n個比較器。這不僅減小了芯片面積,而且降低了功耗。折疊單元電路是折疊式ADC的核心模塊,其數(shù)學模型及波形模型如圖4所示。

圖4 折疊電路數(shù)學模型及波形模型

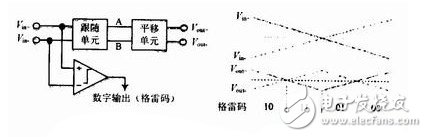

折疊單元電路工作原理如下;設折疊單元輸入電壓范圍為-VR~+VR,如圖4所示,輸入信號同時送給跟隨單元和比較器,跟隨單元實現(xiàn)的功能是使得其輸出端A,B分別跟隨Vin+,Vin-中較高者和較低者;平移單元將跟隨單元的輸出電壓進行平移,使其達到信號折疊的目的,如圖4所示。其輸出的電壓信號Vout+,Vout-作為下一級折疊單元的輸入信號。比較器輸出的是格雷碼數(shù)字輸出,由于ADC最終要實現(xiàn)二進制碼輸出,所以還需要在后續(xù)電路中實現(xiàn)格雷碼向二進制碼的轉(zhuǎn)換。

本文設計的A/D轉(zhuǎn)換器電路采用2級折疊結(jié)構(gòu)的子ADC,產(chǎn)生3位數(shù)字信號輸出。2組折疊單元具有相同的結(jié)構(gòu),折疊單元接收差分模擬輸入信號,產(chǎn)生1位輸出數(shù)字信號,同時產(chǎn)生1對差分折疊模擬輸出信號輸出給下一級折疊單元。圖5給出了折疊單元的結(jié)構(gòu)原理,以及它的輸入/輸出波形。

圖5 折疊單元的結(jié)構(gòu)原理以及它的輸入/輸出波形

模擬輸入電壓VINH,VINL驅(qū)動一對互補的射極跟隨器(折疊單元),輸出一對折疊信號VXH,VXL。VXH,VXL分別跟隨VINH,VINL中電壓較高的一個和較低的一個,這樣就完成了輸入信號的折疊。信號的共模電平由平移單元調(diào)整,平移單元由平移電阻R1(R2)及跟隨器Q1。(Q2)組成,最終得到輸出信號VOH,VOL。VINH,VINL還通過折疊單元放大后輸入預放大比較器產(chǎn)生格雷碼數(shù)字信號,并完成格雷碼二進制碼轉(zhuǎn)換。 A/D轉(zhuǎn)換器的子ADC實現(xiàn)模擬信號量化為格雷碼的同時,實現(xiàn)格雷碼向二進制碼的轉(zhuǎn)換,所以在轉(zhuǎn)換過程中模擬信號必須在格雷碼被鎖存之前全部被折疊單元處理完畢。這里的折疊單元都是以射極跟隨器為基礎構(gòu)成的,所以整個折疊轉(zhuǎn)化過程很快。由于折疊單元的增益為一,模擬信號通過跟隨器完成折疊之后振幅減半。

2 三級流水線A/D轉(zhuǎn)換器電路仿真與分析

該轉(zhuǎn)換器采用Zarlink 0.6 μm雙多晶互補雙極工藝實現(xiàn)。NPN管,PNP管特性頻率分別可以達到25 GHz和19 GHz,完全滿足電路性能要求。并使用Cadence Spectre電路仿真軟件對電路進行仿真驗證。

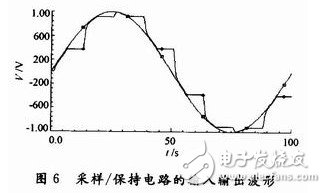

經(jīng)Spectre仿真驗證,T/H電路在-40~+100℃內(nèi)均能正常工作。圖6是典型工藝條件下,輸入信號頻率為10 MHz、幅度為2 V時,采樣/保持電路的輸出波形。圖6中,在保持階段保持電壓的變化很小,其變化量不大于70μV,故該電路完全滿足9位的精度要求。

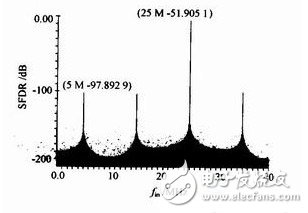

圖7是采樣頻率為100 MHz,輸入信號在幅度為2.2 V、頻率為25 MHz情況下,對輸出信號做離散傅里葉變換(DFT)得到的頻譜圖。由圖可知,輸入信號頻率為25 MHz時無雜散動態(tài)范圍(SFDR)為97.84 dB,完全滿足設計要求。

圖7 采樣/保持電路的SFDR

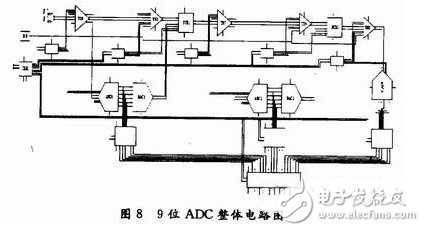

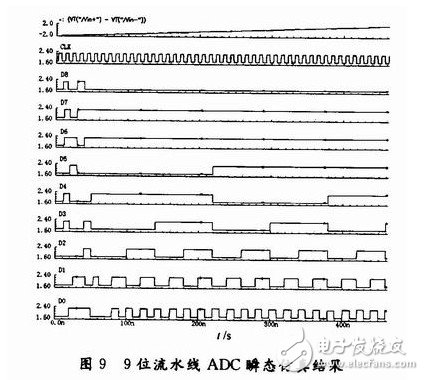

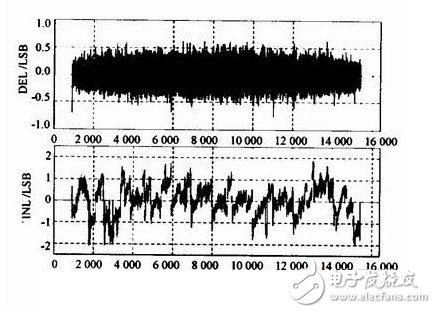

圖8是9位100 MSPS三級流水線A/D轉(zhuǎn)換器整體電路圖,采樣時鐘CP頻率為100 MHz,輸入信號為一個上升的斜波的正弦波,峰峰值為2.2 V。圖9和圖10分別為A/D轉(zhuǎn)換器的瞬態(tài)仿真結(jié)果和動態(tài)仿真結(jié)果。

由仿真結(jié)果可以看出,電路具有良好的線性度,在整個輸入范圍內(nèi)鮮見誤碼。典型的DNL為0.7LSB,INL為2.0LSB,滿足電路設計要求。

圖10動態(tài)仿真結(jié)果

3 結(jié)語

本文設計了一個9位100 MHz低功耗流水線A/D轉(zhuǎn)換器電路。該A/D轉(zhuǎn)換器采用開環(huán)結(jié)構(gòu)的采樣保持電路提高了輸入帶寬,使用折疊結(jié)構(gòu)子ADC,簡化了電路結(jié)構(gòu),減小了芯片面積和功耗。該ADC有效輸入帶寬達到100 MHz。在奈奎斯特頻率范圍內(nèi),整個ADC的有效位數(shù)始終高于10位。在100 MHz采樣頻率下,電路的功耗僅為650 mW。

-

放大器

+關注

關注

145文章

14024瀏覽量

215586 -

轉(zhuǎn)換器

+關注

關注

27文章

8879瀏覽量

149970 -

adc

+關注

關注

99文章

6606瀏覽量

547616

發(fā)布評論請先 登錄

相關推薦

流水線ADC結(jié)構(gòu)解析 流水線ADC和其它ADC的比較

流水線型模數(shù)轉(zhuǎn)換器MAX1200及其與DSP的接口

如何利用SIMULINK建立1.5位/級10位流水線模數(shù)轉(zhuǎn)換器?

一種流水線結(jié)構(gòu)AD轉(zhuǎn)換器的速度分析方法

MAX1200中文資料,pdf (流水線結(jié)構(gòu)的模數(shù)轉(zhuǎn)換器)

一種基于40nmCMOS工藝12位60MHz流水線模數(shù)轉(zhuǎn)換器

ADC12281 12位20MSPS單端輸入流水線AD轉(zhuǎn)換器的詳細資料概述

12bit200MSPS時間交織流水線ADC研究與設計

了解流水線型ADC

流水線ADC的內(nèi)部結(jié)構(gòu)和工作原理是什么

ADS804流水線式模數(shù)(A/D)轉(zhuǎn)換器數(shù)據(jù)表

ADS830流水線式CMOS模數(shù)(A/D)轉(zhuǎn)換器數(shù)據(jù)表

ADS807高動態(tài)范圍、12位流水線式模數(shù)(A/D)轉(zhuǎn)換器數(shù)據(jù)表

評論