隨著超大規模集成電路的迅速發展,半導體工業進入深亞微米時代,器件特征尺寸越來越小,芯片規模越來越大,可以在單芯片上集成上百萬到數億只晶體管。如此密集的集成度使我們現在能夠在一小塊芯片上把以前由CPU和外設等數塊芯片實現的功能集成起來,由單片集成電路構成功能強大的、完整的系統,這就是我們通常所說的片上系統。

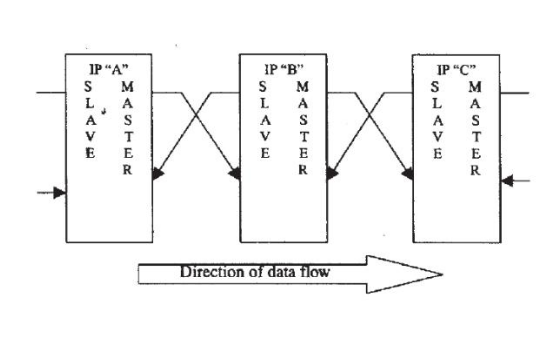

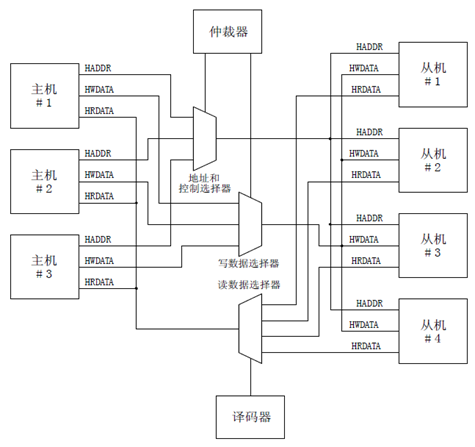

IP復用是片上系統時代的核心技術之一。由于IP核的設計千差萬別,它們要能夠直接連接,就要遵守相同的接口標準。在片上系統中,處理器核和所有外設通過共享總線互通互聯,因此這些IP核必須遵守相同的總線規范。總線規范定義的是IP核之間的通用接口,因此它定義了一套標準的信號和總線周期,以連接不同的模塊,而不是試圖去規范IP核的功能和接口如何實現。一個片上總線(On-Chip Bus,OCB)規范一般需要定義各個模塊之間初始化、仲裁、請求傳輸、響應、發送接收等過程中驅動、時序、策略等關系。

芯片與電路板的資源和環境的不同,導致片上總線與板上總線存在若干明顯差異,包括:

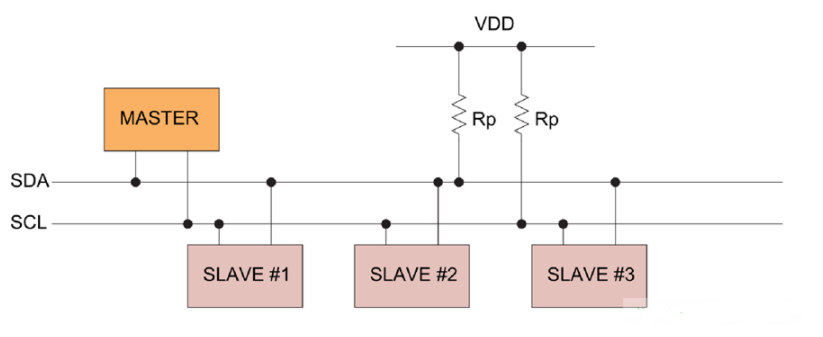

①片上總線多采用單向信號線,而板上總線多采用三態信號。片上三態總線無論在功耗、速度、可測性上都存在很大缺陷,而且一旦出現多驅動情況便會損毀芯片(比如若應該輸出"Z"的信號實際輸出為"1",而另有一個信號輸出為"0",就形成一個低電阻通路,導致局部電流過大,熱量難以及時釋放,從而增加芯片功耗和大大降低芯片壽命)。由于片上布線資源較為豐富,因此片上總線多采用單向信號線。由于電路板上布線資源較為昂貴,因此板上總線多采用三態總線,但是由于三態總線的功耗問題和速度限制,目前板上總線也在向串行和非三態方向發展,如USB和PCI Express。

②片上總線比板上總線更加簡單靈活。首先片上總線結構要簡單,這樣可以占用較少的邏輯單元;其次時序要簡單,以利于提高總線的速度;第三接口要簡單,如此可減少與IP核連接的復雜度。片上系統應用廣泛,不同的應用對總線的要求各異,因此片上總線具有較大的靈活性。其一,多數片上總線的數據和地址寬度都可變,其二,部分片上總線的互連結構可變,如Wishbone總線支持點到點、數據流、共享總線和交叉開關四種互連方式;其三,部分片上總線的仲裁機制靈活可變,如Wishbone總線的仲裁機制可以完全由用戶定制。而板上總線則較為死板,時序也更加苛刻。

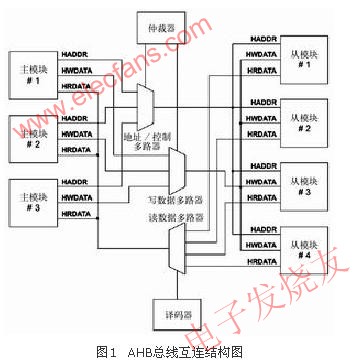

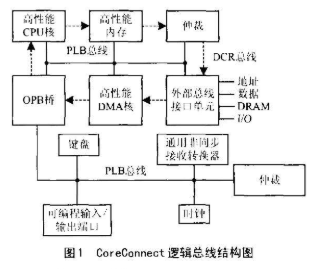

目前比較常見的片上總線規范有ARM公司的AMBA、Silicore的Wishbone、IBM公司的CoreConnect和Altera公司的Avalon。其他三種總線各有特點,其適用范圍也不同。AMBA 總線規范因ARM處理器的廣泛使用而擁有眾多第三方支持,被ARM公司90%以上的合作伙伴采用,已成為廣泛支持的現有互連標準之一。IBM公司的CoreConnect因為IBM的業界地位也有廣泛的應用。Avalon主要用于Altera公司系列FPGA中,最大的優點在于其配置的簡單性,可由EDA工具快速生成。這三種片上總線雖然都是公開標準,但都不是免費的。而Wishbone則是一個真正開放和免費的規范。它最先是由Silicore公司提出的,目前由OpenCores組織維護。由于其開放性,因此OpenCores上的免費的IP核,大多數都采用Wishbone標準。Wishbone的優勢除開放、免費、擁有眾多免費IP核外,還有簡單、靈活、輕量的特點,特別適合大型IP內部的小型IP之間的互聯。在很多OpenRISC處理器設計中,各個模塊間的互聯接口中大量的采用了Wishbone總線規范。

Wishbone已被OPENCORE 聯盟采用,并且有可能成為IEEE標準。因此,Wishbone 總線從技術上講簡單、靈活、功能強大及易于移植,從經濟角度考慮又全部免費,易于全面推廣。我們認為它極有可能成為未來SoC片上總線的通用標準,其前景看好。

Lattice在MachXO3等系列的產品中采用基于Wishbone總線的IP核設計,包括軟核和一些硬核(Harden I2C、SPI、Timer/Counter)。學習Wishbone的基本原理,對我們在使用和設計IP時都是很有幫助的。Wishbone作為一個輕量級片上總線,比AMBA等總線簡單的多,很適合片上總線的入門者學習。

-

芯片

+關注

關注

456文章

51127瀏覽量

426097 -

集成電路

+關注

關注

5391文章

11606瀏覽量

362753 -

總線

+關注

關注

10文章

2899瀏覽量

88277

原文標題:【博文連載】片上總線概述

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

求解ARM的On-Chip Bus片上總線規范是什么

主從式片上總線系統交易級的實現

一種面向應用優化的片上總線調度策略

AHB片上系統總線的建模與驗證

基于Wishbone片上總線的IP核的互聯

基于AMBA片上總線的片上系統

AMBA片上總線在基于IP復用的SoC設計中的應用

三種總線的邏輯結構描述及在片上系統中的應用

片上總線與板上總線存在若干明顯差異

片上總線與板上總線存在若干明顯差異

評論