現(xiàn)代密碼協(xié)議規(guī)定只有授權(quán)參與者才可以獲得密鑰和訪問信息的權(quán)限。然而,通過侵入系統(tǒng)泄露密碼的方法層出不窮,給現(xiàn)代信息安全造成嚴(yán)重的威脅。對此問題,PUF不可克隆的優(yōu)點(diǎn),為信息安全提供了進(jìn)一步的保障。例如:RO PUF、Arbiter PUF、SRAM PUF。通過把物理信息集成到電路設(shè)計從而實(shí)現(xiàn)PUF的設(shè)計,與現(xiàn)有RO PUF相比,PISO移位寄存器的運(yùn)用減少了更多的硬件資源。由4位激勵能夠產(chǎn)生16位隨機(jī)響應(yīng),大大增加了激勵響應(yīng)對的數(shù)目,而且通過FPGA測得內(nèi)部漢明距離是符合要求的。

引言

加密是信息安全的一個分支,其中包括數(shù)據(jù)安全性、數(shù)據(jù)完整性和安全認(rèn)證機(jī)制。加密技術(shù)的使用使得通信安全有了保障。發(fā)送方終端通過密鑰對數(shù)據(jù)進(jìn)行加密,在接收終端以相同的密鑰或派生密鑰解密信息。加密體制依據(jù)解密與加密所用秘鑰是否相同,將其劃分為對稱和非對稱密碼兩種體制。在對稱密碼體制中,加密密鑰和解密密鑰是一樣的。而非對稱密碼體制中,加密密鑰和解密密鑰是分開的,不相同。加密的密鑰不應(yīng)該受到環(huán)境的影響,應(yīng)該是隨機(jī)的、可靠的以及抗側(cè)信道攻擊的。 一種基于PUF的密鑰產(chǎn)生機(jī)制如圖1所示。

經(jīng)典線性反饋移位寄存器用于隨機(jī)數(shù)生成。偽噪聲隨機(jī)數(shù)字發(fā)生器(PN-RNG)是利用初始種子產(chǎn)生隨機(jī)數(shù)序列的。由于有一組共同的初始種子,偽噪聲隨機(jī)數(shù)發(fā)生器(PN-RNG)產(chǎn)生的隨機(jī)序列并不隨機(jī),如果有人存儲這些序列,根據(jù)序列之間的相關(guān)性,即PN-RNG在產(chǎn)生最大值之后開始產(chǎn)生相同的序列,對手可以預(yù)測到下一個序列[1]。加密密鑰是數(shù)據(jù)安全的關(guān)鍵,秘鑰一定是可信可靠的隨機(jī)數(shù)。真正可靠的密碼體系應(yīng)該是:即便破譯者可以加密任何的明文,也沒法破譯密文。一般地,如果僅根據(jù)密文就可以推算出明文或密鑰,則稱這個密碼體制是可破譯的。基爾霍夫原則指出“一個密碼體制是安全的,其總的前提就是假設(shè)密碼分析者已經(jīng)知道了密碼體制的算法,體制的安全性僅依賴于密鑰的保密”。現(xiàn)在的人喜歡依賴手機(jī)進(jìn)行電子交易,所以信息安全得到了更多的關(guān)注。硅密鑰因為具有不可克隆的特點(diǎn)而被優(yōu)選,不可克隆是指:即使用相同的材料也不能制造出2個性能相同的設(shè)備。2001年Srini Devadas(麻省理工學(xué)院CSAIL)提出了用物理不可克隆函數(shù)(PUF)來生成密鑰的IC。PUF是一種基于器件和工藝偏差的體系。從PUF系統(tǒng)可以產(chǎn)生不可預(yù)測的隨機(jī)數(shù),不過PUF產(chǎn)生的隨機(jī)數(shù)必須經(jīng)過編碼才能獲取想要的密鑰。PUF電路利用器件的特定屬性生成隨機(jī)數(shù),這些屬性是無法克隆的,并且很難預(yù)測。根據(jù)半導(dǎo)體的任何可變屬性都可以用來構(gòu)建PUF。延遲、頻率和SRAM上電初值的PUF,已在早期研究工作中有所研究,這些PUF[3]都反應(yīng)了制造設(shè)備的隨機(jī)性變化。PUF電路必須能夠產(chǎn)生大量的激勵響應(yīng)對。對于每個激勵響應(yīng)都應(yīng)該獨(dú)特而不可預(yù)測。對于不同的PUF,同樣的激勵生成的PUF響應(yīng)應(yīng)該都是不同的。PUF的性能可以用唯一性、可靠性和穩(wěn)定性衡量。唯一性一般用內(nèi)部漢明距離表示,理想值μ=0%。它代表了對于不同的PUF給予相同的激勵條件,得到響應(yīng)之間的差異性。文獻(xiàn)[3]中展示了唯一性,用這種特性來識別電路。可靠性一般用片間漢明距離表示,理想情況下μ=0%。它代表對于同一個PUF,給予兩個相同的激勵,得到響應(yīng)之間的差異性。穩(wěn)定性表示響應(yīng)受溫度、老化效應(yīng)、電源電壓、噪聲等環(huán)境的影響。理想的響應(yīng)應(yīng)該是獨(dú)立于這些因素的[4]。

1典型RO-PUF

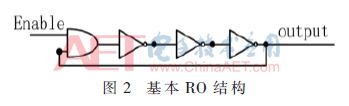

RO PUF是PUF中常見的應(yīng)用之一,其基本結(jié)構(gòu)單元是環(huán)形振蕩器(Ring-Oscillator,RO)。RO的構(gòu)成如圖2所示。

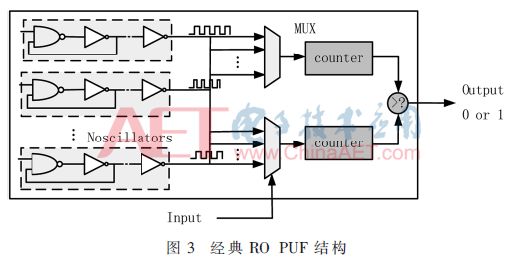

環(huán)形震蕩PUF是一個將激勵映射到響應(yīng)的頻率變化函數(shù)。RO PUF是由于工藝偏差而產(chǎn)生的變化頻率來生成隨機(jī)數(shù)的。圖3給出了N個環(huán)振蕩器產(chǎn)生的不同頻率f1,f2,…fn,這里2個并行的多路復(fù)用器的選擇取決于輸入激勵。兩個多路復(fù)用器選定兩個不同的頻率 ,它們分別作為n位計數(shù)器的時鐘輸入。然后,兩個計數(shù)器對選定的兩個頻率開始計數(shù)。如果Q1>Q2響應(yīng)為1,否則輸出響應(yīng)為0。

2本文提出的方案

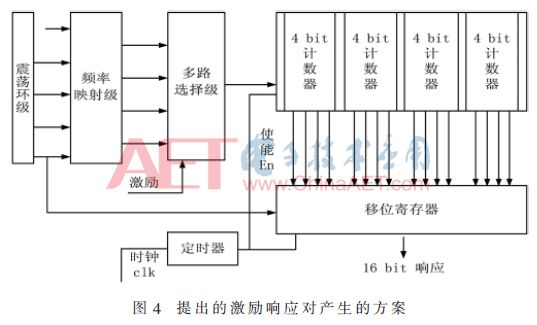

本設(shè)計是利用不同數(shù)量的環(huán)形振蕩器而不是基于工藝偏差用相同數(shù)量的環(huán)形振蕩器來獲得變化的頻率。圖4所示的電路圖有3個工作模塊:(1)產(chǎn)生不同頻率的環(huán)形振蕩器,分別用不同階數(shù)的RO震蕩環(huán)產(chǎn)生5個不同的震蕩頻率;(2)映射階段,它是一個D觸發(fā)器的級聯(lián),將環(huán)形振蕩器產(chǎn)生的任意兩個頻率作為D觸發(fā)器的數(shù)據(jù)輸入和時鐘輸入,輸出是一個采樣頻率。本設(shè)計中將F1、F2、F3、F4作為D觸發(fā)器的數(shù)據(jù)輸入,其對應(yīng)的時鐘輸入分別為F2、F3、F4、F5;(3)選擇電路,基于多路復(fù)用器的選擇電路,根據(jù)激勵輸入選擇4個時鐘脈沖,并作為計數(shù)器的時鐘脈沖。在計數(shù)某個確定時間后,計數(shù)器值鎖存到PISO移位寄存器,在移位寄存器的每個時鐘有效邊沿產(chǎn)生1位響應(yīng),重復(fù)16次,獲得16位響應(yīng)。圖4電路代表激勵響應(yīng)對產(chǎn)生的方案,4位激勵被映射到16位響應(yīng),這個PUF是變化頻率和頻率映射階段的隨機(jī)函數(shù)。提出的電路結(jié)構(gòu)在Virtex5上得到驗證。

2.1環(huán)形振蕩器

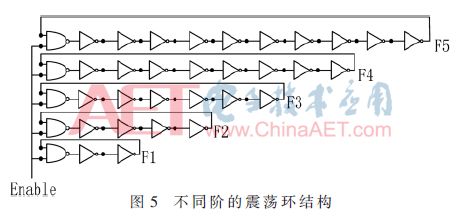

電路由5個具有奇數(shù)個反相器的環(huán)形振蕩器組成,目的是獲得不同的變化頻率。每個RO由圖5所示的nand門的輸入Enable控制,使能Enable信號為高開始振蕩。環(huán)形振蕩器由奇數(shù)個反相器構(gòu)成,其頻率取決于反相器的階數(shù),對于N階環(huán)形振蕩器,振蕩頻率為:Fosc=1/τpd=1/(2Nτp),其中τpd=τphl+τplh,N為反向器的階數(shù)[5]。從表達(dá)式發(fā)現(xiàn),隨著反相器階數(shù)的增加,頻率下降,頻率也彼此接近。表1顯示震蕩頻率隨著反相器數(shù)量的增加而發(fā)生變化。

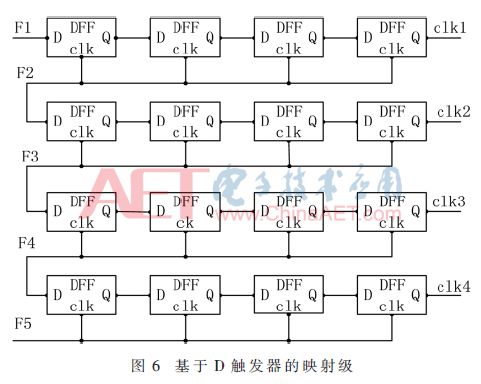

2.2映射階段

它是由4級D觸發(fā)器級聯(lián),D觸發(fā)器將兩個頻率中一個作為數(shù)據(jù)輸入,另一個作為時鐘輸入,獲得一個采樣輸出,圖6所示的第一行4級D觸發(fā)器數(shù)據(jù)輸入端接F1,時鐘輸入接F2,采樣輸出記為CLK1。在本設(shè)計中使用時鐘上升沿觸發(fā)有效; 如果D觸發(fā)器時鐘上升沿比數(shù)據(jù)上升沿提前,輸出保持上次結(jié)果不變,如果時鐘上升沿比數(shù)據(jù)上升沿落后,則輸出與觸發(fā)器數(shù)據(jù)端輸入端一樣。同理,第二行、第三行、第四行4級級聯(lián)的D觸發(fā)器產(chǎn)生CLK2、CLK3、CLK4,產(chǎn)生的4個時鐘脈沖信號將用于下一級的頻率比較階段。由于振蕩器頻率不同,它們的邊緣到達(dá)時間是不可預(yù)測的,這就增加了更多的隨機(jī)性到PUF電路。在數(shù)據(jù)和時鐘邊緣同時到達(dá)的情況下將導(dǎo)致亞穩(wěn)態(tài),在下一個邊沿時鐘脈沖產(chǎn)生完全不可預(yù)測的電路輸出(高或低)。并且本文采用的是慢時鐘采快時鐘,根據(jù)麥奎斯特采樣定理,肯定會有信號遺漏,但是我們并不是想要最后得到完整的數(shù)據(jù)信號,僅僅是利用丟失信號的不確定性來增加PUF電路的隨機(jī)性。

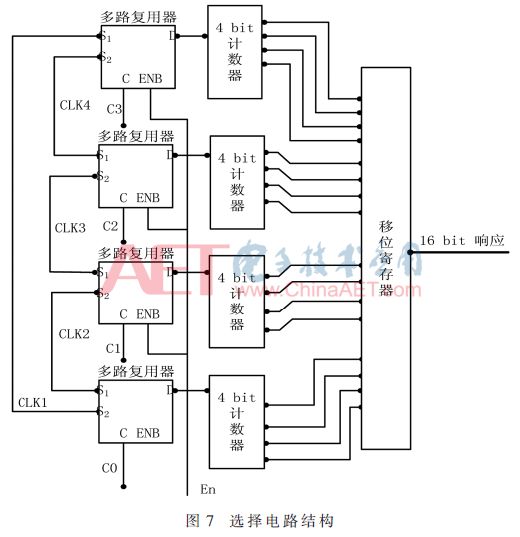

2.3選擇電路

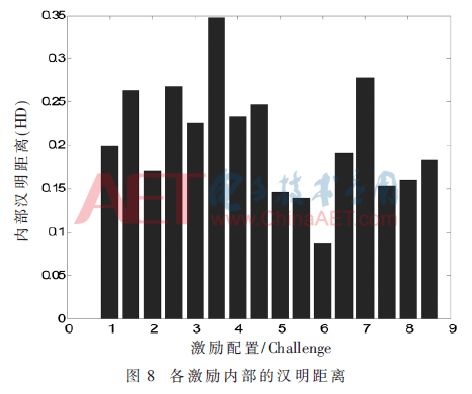

圖7所示電路是多路復(fù)用器構(gòu)成的選擇電路。時鐘上升沿到來計數(shù)器向上計數(shù)。在計數(shù)某個確定時間后,計數(shù)器值鎖存到PISO移位寄存器,在移位寄存器的每個時鐘有效邊沿產(chǎn)生1位響應(yīng),重復(fù)16次,獲得16位響應(yīng)。圖8給出了16個激勵的內(nèi)部漢明距離,這幾乎是理想的值。本文提出的PUF結(jié)構(gòu)與現(xiàn)有的RO PUF相比,需要更少的硬件資源。圖3顯示了2個計數(shù)器產(chǎn)生1位響應(yīng)的RO結(jié)構(gòu)。要有16位響應(yīng),它需要32個計數(shù)器和16個比較器并行工作。并且提出的PUF結(jié)構(gòu)相對于RO PUF在計數(shù)階段消除了硬件復(fù)雜性,并從單個計數(shù)器和PISO移位寄存器直接產(chǎn)生16位響應(yīng)。

本文提出了一種新穎的基于硬件的產(chǎn)生激勵響應(yīng)對的RO PUF結(jié)構(gòu),其結(jié)合電路變化而不是工藝偏差。運(yùn)用頻率映射與PUF結(jié)合的策略產(chǎn)生隨機(jī)性響應(yīng),響應(yīng)的內(nèi)部漢明距離幾乎達(dá)到理想值。PUF的早期設(shè)計中2個計數(shù)器產(chǎn)生1位響應(yīng),當(dāng)前設(shè)計中用相同位數(shù)的計數(shù)器產(chǎn)生16位響應(yīng)。在接下來的研究中計數(shù)器和PISO移位寄存器的大小可以增強(qiáng)到255位,為AES加密算法生成128位密鑰。

3實(shí)驗與分析

本文將上述方案在FPGA平臺上進(jìn)行實(shí)驗測試,實(shí)驗開發(fā)板:Xilinx Virtex5,開發(fā)軟件:集成開發(fā)環(huán)境ISE,仿真工具M(jìn)odelsim,測試和分析工具ChipScope;開發(fā)語言:Verilog HDL。經(jīng)過XST綜合后的FPGA配置文件下載到開發(fā)板上,時鐘周期是50 ns,定時器定時時間為0.512 μs。用ChipScope 軟件抓取輸入激勵與其對應(yīng)輸出響應(yīng)的波形圖。通過ChipScope 導(dǎo)出的波形圖,解析出激勵-響應(yīng)對。在測試過程中,對電路進(jìn)行了50 次測試,每次測試能夠得到16個激勵-響應(yīng)對,對同一個激勵產(chǎn)生的50個響應(yīng)計算內(nèi)部漢明距離,結(jié)果表明,該電路對于同一激勵的響應(yīng)內(nèi)部漢明距離最大為0.277 8,最小可以達(dá)到0.080 0,大部分分布在0.200 0左右,文獻(xiàn)[14]中測得的內(nèi)部漢明距離9次達(dá)到0.310 0,6次達(dá)到0.190 0,1次達(dá)到0.250 0,所以比較文獻(xiàn)[14],本文設(shè)計的PUF較優(yōu),該設(shè)計滿足PUF函數(shù)的相關(guān)要求。

4結(jié)論

本文的設(shè)計是通過把物理信息集成到電路設(shè)計從而實(shí)現(xiàn)PUF的設(shè)計,與現(xiàn)有RO PUF相比,PISO位寄存器的運(yùn)用減少了更多的硬件資源。由4位激勵能夠產(chǎn)生16位隨機(jī)響應(yīng),大大增加了激勵響應(yīng)對的數(shù)目,也即增加了ID的數(shù)量,安全性得到提高。并且經(jīng)由FPGA驗證本文改良后的RO PUF具有更高的“片內(nèi)穩(wěn)定性”。環(huán)境溫度、供電電壓是影響片內(nèi)穩(wěn)定性的重要因素,確保ID不隨溫度、電壓發(fā)生變化,并且精確可重復(fù)生成是未來研究的方向。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21789瀏覽量

605088 -

PUF

+關(guān)注

關(guān)注

2文章

24瀏覽量

8607

原文標(biāo)題:【學(xué)術(shù)論文】基于RO電路變化PUF的FPGA實(shí)現(xiàn)

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

淺談PUF技術(shù)如何保護(hù)知識產(chǎn)權(quán)

基于憶阻器的PUF芯片設(shè)計

LPC55S69的PUF數(shù)字指紋能否用于生成公私鑰對?

國內(nèi)首創(chuàng)!通過SDK集成PUF,“芯片指紋”打造MCU高安全芯片

基于FPGA的光電系統(tǒng)同步自適應(yīng)電路設(shè)計與實(shí)現(xiàn)

動態(tài)可配置多輸出RO PUF設(shè)計研究

Rogers Ro4350高頻PCB材料

RO3000系列高頻電路材料Rogers

RO3010?層壓板Rogers

使用PUF的外部安全存儲應(yīng)用說明

基于RO電路變化PUF的FPGA實(shí)現(xiàn)

基于RO電路變化PUF的FPGA實(shí)現(xiàn)

評論