FPGA相比于CPU,最大的優(yōu)點(diǎn)在于速度,簡單來講,F(xiàn)PGA是靠控制每個(gè)時(shí)鐘(Cycle)來驅(qū)動信號與寄存器傳輸?shù)模簿褪钦f可以通過時(shí)鐘來精確控制任務(wù)。而且,F(xiàn)PGA是并行執(zhí)行的,每個(gè)Cycle可以同時(shí)執(zhí)行上百萬個(gè)數(shù)據(jù)流任務(wù),所以,和CPU相比,F(xiàn)PGA是通過較慢的時(shí)鐘頻率,同時(shí)并行執(zhí)行數(shù)據(jù)流,而CPU雖然主頻高,但是并行執(zhí)行能力差,綜合起來對于同樣的代碼,應(yīng)用程序在FPGA上的運(yùn)行速度可能比在傳統(tǒng)CPU上運(yùn)行要快100倍。

FPGA中包含上千萬的可編程邏輯資源,具有并行性和并發(fā)性的優(yōu)點(diǎn)。在設(shè)計(jì)時(shí),工程師可以利用這種并行體系結(jié)構(gòu),將設(shè)計(jì)分解為結(jié)構(gòu)良好的數(shù)據(jù)執(zhí)行流。

例如,一幀圖像,如果按照傳統(tǒng)處理方式,可以按像素來處理整個(gè)圖像。但是當(dāng)并行處理時(shí),它被分解成不同的碎片,由不同的進(jìn)程同時(shí)進(jìn)行處理,然后再拼湊回一起。過程雖然變復(fù)雜了,但是速度快了許多,要求輸入數(shù)據(jù)必須以最優(yōu)的方式分解,并有效地分配給每個(gè)進(jìn)程,然后將處理后的數(shù)據(jù)收集并重新組裝,從而大大提高了效率。

在一個(gè)普通的CPU中,這一過程涉及到數(shù)據(jù)從內(nèi)存中存入和取出,以及使進(jìn)程對當(dāng)前內(nèi)存狀態(tài)保持一致的復(fù)雜協(xié)議。即使是最大的英特爾CPU也只有18個(gè)內(nèi)核。相比之下,在FPGA中,數(shù)據(jù)流可以被設(shè)計(jì),因此它永遠(yuǎn)不會離開芯片。數(shù)以萬計(jì)的并發(fā)進(jìn)程可以同時(shí)存在,并且處理的時(shí)間得到了優(yōu)化,因此吞吐量始終是最大的。

通過FPGA實(shí)現(xiàn)還有給優(yōu)勢就是成本。使用FPGA可以節(jié)省大量成本,因?yàn)樘岣咚俣鹊耐瑫r(shí)減少了硬件需求,一個(gè)FPGA可以執(zhí)行許多服務(wù)器的任務(wù)。

最后,F(xiàn)PGA具有強(qiáng)大的新一代互聯(lián)互通和增強(qiáng)的靈活性,可以利用最新的技術(shù)發(fā)展在器件上重新編程。一旦啟動并運(yùn)行,F(xiàn)PGA就可以隨時(shí)改變以滿足不斷變化的業(yè)務(wù)需求。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605177 -

cpu

+關(guān)注

關(guān)注

68文章

10901瀏覽量

212667

原文標(biāo)題:FPGA在運(yùn)算中的優(yōu)勢

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

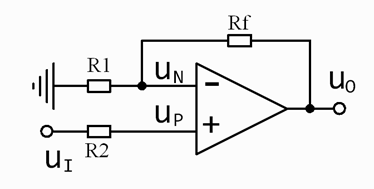

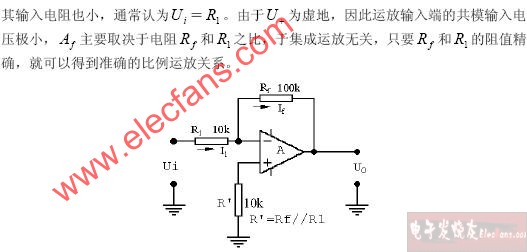

同相比例運(yùn)算電路設(shè)計(jì)

相比CPU、GPU、ASIC,FPGA有什么優(yōu)勢

FPGA在圖像處理領(lǐng)域的優(yōu)勢有哪些?

集成運(yùn)放在運(yùn)算電路中的應(yīng)用

FPGA/CPLD與單片機(jī)相比有哪些優(yōu)勢?

在芯片設(shè)計(jì)中FPGA的優(yōu)勢是什么?

模擬乘法器及其在運(yùn)算電路中的應(yīng)用

什么是ASIC芯片?與CPU、GPU、FPGA相比如何?

FPGA+CPU的單片集成相較于傳統(tǒng)應(yīng)用的優(yōu)勢明顯

FPGA相比CPU在運(yùn)算中的優(yōu)勢

FPGA相比CPU在運(yùn)算中的優(yōu)勢

評論