LU是 Latch Up的簡寫,即閂鎖效應,也叫可控硅效應,表征芯片被觸發低阻抗通路后、電源VDD到GND之間能承受的最大電流。非車規芯片的規格書中通常都不會提供這個參數,而車規芯片的規格書中通常都會明確標注出來這個參數。這也是一個極為重要卻極容易被電子工程師忽略的參數。

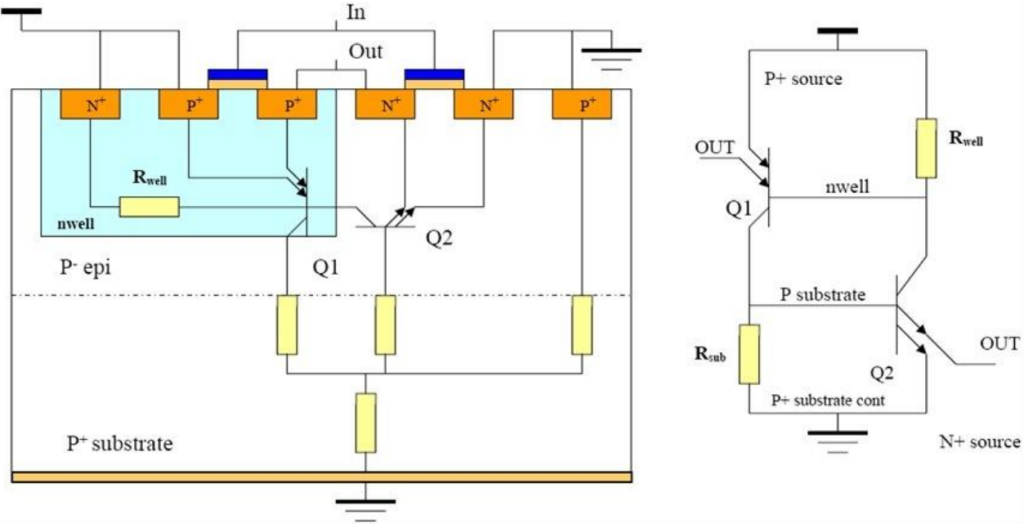

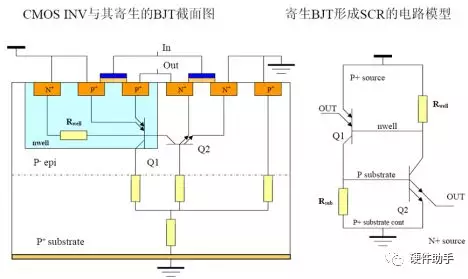

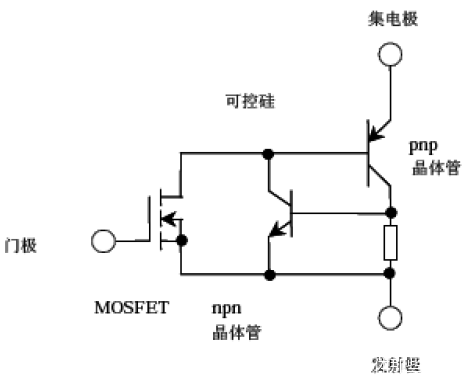

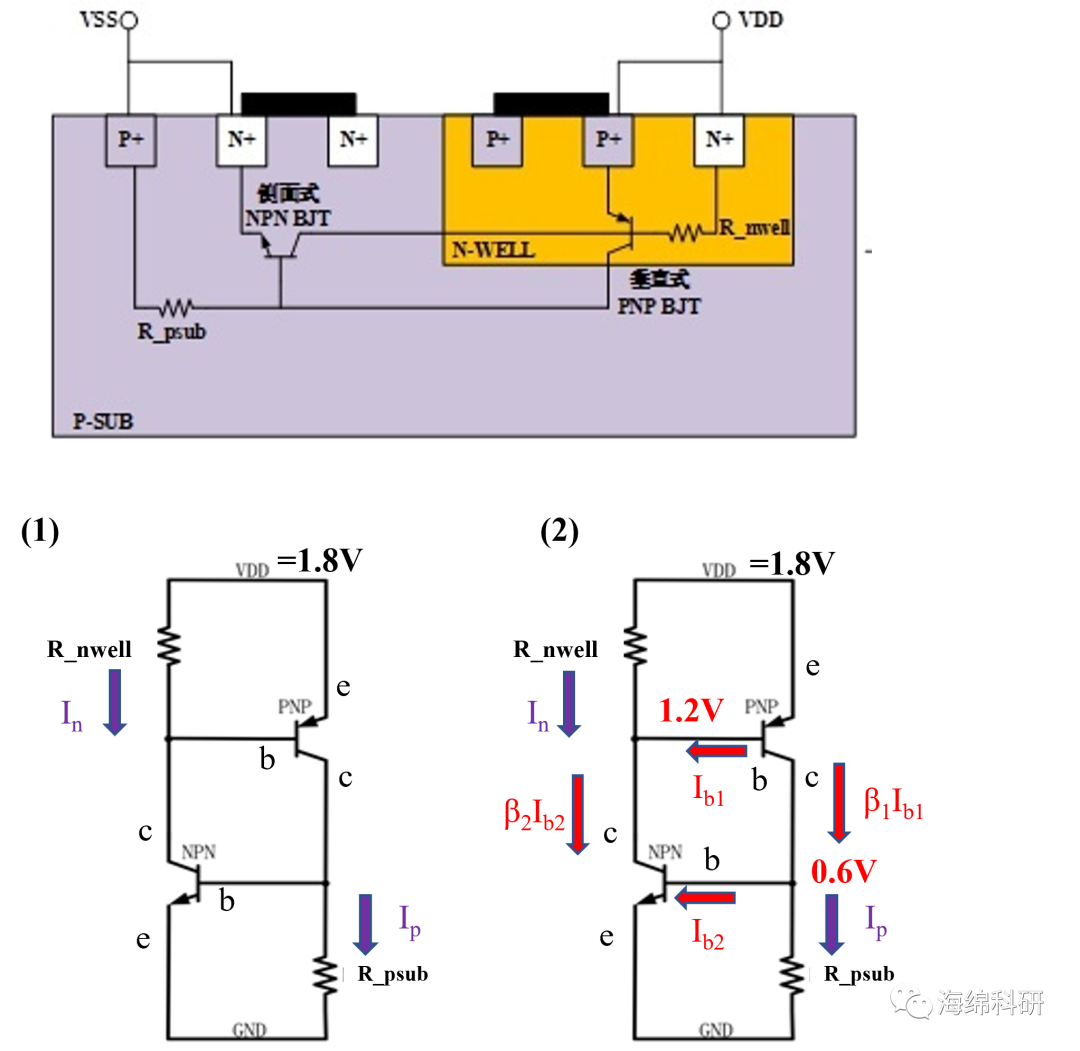

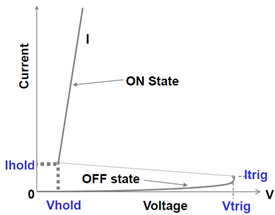

閂鎖效應是CMOS工藝所特有的寄生效應,是由NMOS的有源區、P襯底、N阱、PMOS的有源區構成的N-P-N-P結構而產生的,當其中一個三極管正偏時,就會構成正反饋形成閂鎖。ESD 和相關的電壓瞬變都可能會引起閂鎖效應,是半導體器件失效的主要原因之一。一旦觸發閂鎖效應,即會產生一個低阻抗通路,如圖1,當Q1或者Q2被異常觸發導通后,會使芯片的VDD和GND之間產生大電流,如果芯片的VDD端流入的電流超過芯片Latch up能承受的電流極限,就可能會燒毀芯片。

圖1 CMOS寄生BJT示意圖及等效電路(圖片來源于網絡)

芯片被觸發進入Latch up狀態后,只有重新上電才能脫離這個鎖定狀態。

芯片研發工程師在設計層面會采用多種手段來防御閂鎖的產生,但是難以根除。在應用層面,電子工程師就需要在應用電路層面做適當的防御措施:

1)在輸入端和輸出端加鉗位電路,使輸入和輸出不超過規定電壓。

2)芯片的電源輸入端加去耦電路,防止VDD端出現瞬間的高壓。

3)在VDD供電腳加限流電阻,保證觸發Latch up后的通路極限電流小于芯片承受的能力,保護芯片不被損壞。

4)當系統由幾個電源分別供電時,開關要按下列順序:開啟時,先開啟CMOS芯片的電源,再開啟輸入信號和負載的電源;關閉時,先關閉輸入信號和負載的電源,再關閉CMOS芯片的電源。

-

CMOS

+關注

關注

58文章

5841瀏覽量

236955 -

半導體

+關注

關注

335文章

28111瀏覽量

226628 -

PMOS

+關注

關注

4文章

261瀏覽量

29981 -

閂鎖效應

+關注

關注

1文章

33瀏覽量

9456

原文標題:【芯知識】LU-- 閂鎖效應

文章出處:【微信號:run-ic,微信公眾號:江蘇潤石】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CMOS的閂鎖效應:Latch up的原理分析

淺談IGBT的閂鎖效應

什么是閂鎖效應?

對 閂鎖效應 的一些理解

CMOS電平的介紹和CMOS的閂鎖效應詳細概述

IGBT中的閂鎖效應到底是什么

單片機發生閂鎖效應的因素,如何防止發生單片機閂鎖效應?

芯片失效機理之閂鎖效應

評論