本篇主要針對(duì)CMOS電平,詳細(xì)介紹一下CMOS的閂鎖效應(yīng)。

1、Latch up

閂鎖效應(yīng)是指CMOS電路中固有的寄生可控硅結(jié)構(gòu)(雙極晶體管)被觸發(fā)導(dǎo)通,在電源和地之間存在一個(gè)低阻抗大電流通路,導(dǎo)致電路無法正常工作,甚至燒毀電路。

Latch up是指CMOS晶片中,在電源VDD和地線GND(VSS)之間由于寄生的PNP和NPN雙極性BJT相互影響而產(chǎn)生的一低阻抗通路,它的存在會(huì)使VDD和GND之間產(chǎn)生大電流;

隨著IC制造工藝的發(fā)展,封裝密度和集成度越來越高,產(chǎn)生Latch up的可能性會(huì)越來越大;

Latch up產(chǎn)生的過度電流量可能會(huì)使芯片產(chǎn)生永久性的破壞,Latch up的防范是IC Layout的最重要措施之一;

Latch up最易產(chǎn)生在易受外部干擾的I/O電路處,也偶爾發(fā)生在內(nèi)部電路。

2、Latch up的原理分析

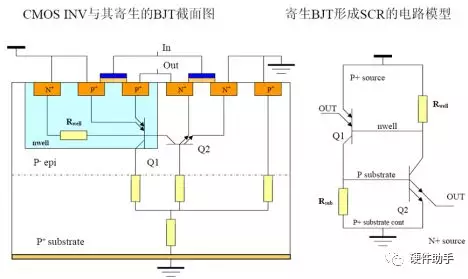

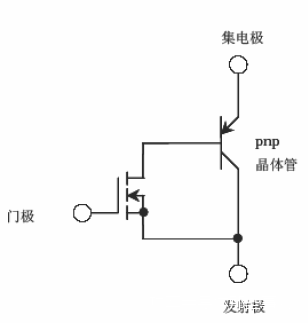

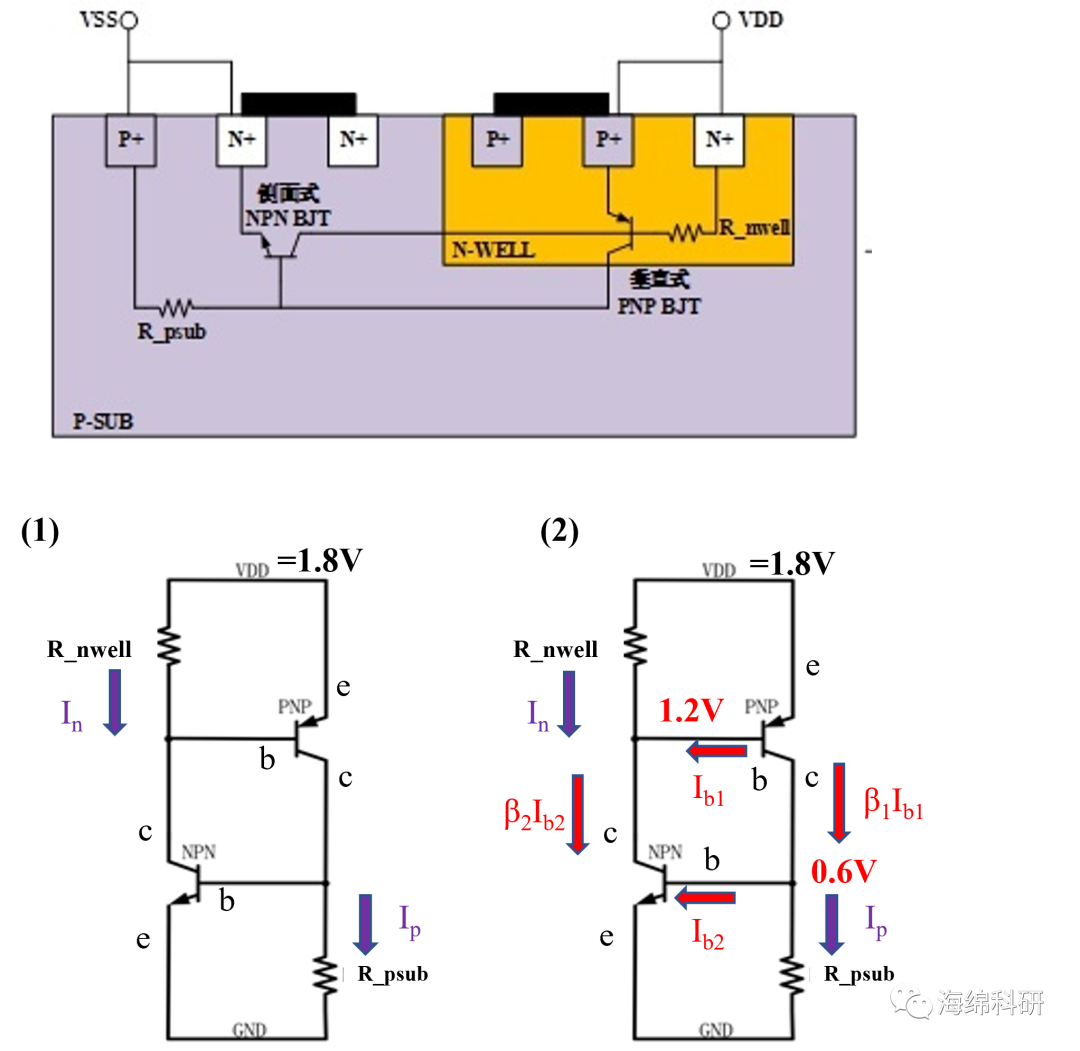

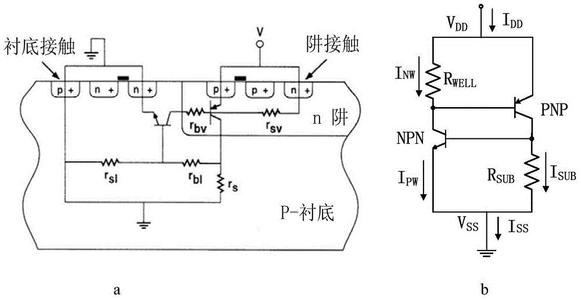

Q1為垂直式PNP BJT,基極(base)是nwell,基極到集電極的增益可達(dá)數(shù)百倍;Q2是側(cè)面式的NPN BJT,基極為P substrate,到集電極的增益可達(dá)數(shù)十倍;Rwell是nwell的寄生電阻;Rsub是substrate電阻。

以上四元件構(gòu)成可控硅(SCR)電路,當(dāng)無外界干擾引起觸發(fā)時(shí),兩個(gè)BJT(可控硅結(jié)構(gòu))處于截止?fàn)顟B(tài),集電極電流由C-B的反向漏電流構(gòu)成,電流增益非常小,此時(shí)Latch up不會(huì)產(chǎn)生。當(dāng)其中一個(gè)BJT的集電極電流受外部干擾突然增加到一定值時(shí),會(huì)反饋至另一個(gè)BJT,從而使兩個(gè)BJT因觸發(fā)而同時(shí)導(dǎo)通,VDD至GND間形成低阻抗通路,Latch up由此而產(chǎn)生。

3、Latch up的產(chǎn)生原因

實(shí)際電路中Latch up產(chǎn)生的原因主要有一下幾種:

芯片一開始工作時(shí)VDD變化導(dǎo)致nwell和P substrate間寄生電容中產(chǎn)生足夠的電流,當(dāng)VDD變化率大到一定程度,將會(huì)引起Latch up(VDD上電太快導(dǎo)致閂鎖);

當(dāng)I/O的信號(hào)變化超出VDD-GND(VSS)的范圍時(shí),有大電流在芯片中產(chǎn)生,也會(huì)導(dǎo)致SCR的觸發(fā)(信號(hào)過壓導(dǎo)致閂鎖);

ESD靜電加壓,可能會(huì)從保護(hù)電路中引入少量帶電載流子到nwell或substrate中,也會(huì)引起SCR的觸發(fā)(ESD導(dǎo)致閂鎖,VDD過壓);

當(dāng)很多的驅(qū)動(dòng)器同時(shí)動(dòng)作,負(fù)載過大使VDD和GND突然變化,也有可能打開SCR的一個(gè)BJT;

nwell側(cè)面漏電流過大。

4、Latch up的防護(hù)措施

針對(duì)上述產(chǎn)生原因,Latch up的防護(hù)方法主要有以下幾個(gè)方面入手:

在基體(substrate)上改變金屬的摻雜,降低BJT的增益;

避免source和drain的正向偏壓;

增加一個(gè)輕摻雜的layer在重?fù)诫s的基體上,阻止側(cè)面電流從垂直BJT到低阻基體上的通路;

使用Guard ring:P+ ring環(huán)繞NMOS并接GND;N+ ring環(huán)繞PMOS并接VDD,一方面可以降低Rwell和Rsub的阻值,另一方面可阻止載流子到達(dá)BJT的基極。如果可能,可再增加兩圈ring;

Substrate contact和well contact應(yīng)盡量靠近source,以降低Rwell和Rsub的阻值;使NMOS盡量靠近GND,PMOS盡量靠近VDD,保持足夠的距離在PMOS和NMOS之間以降低引發(fā)SCR的可能;

除在I/O處需采取防Latch up的措施外,凡接I/O的內(nèi)部MOS也應(yīng)接guard ring;

I/O處盡量不使用PMOS(nwell)。

CMOS電路由于輸入太大的電流,內(nèi)部的電流急劇增大,除非切斷電源,電流一直在增大這種效應(yīng)就是鎖定效應(yīng)。當(dāng)產(chǎn)生鎖定效應(yīng)時(shí),CMOS的內(nèi)部電流能達(dá)到40mA以上,很容易燒毀芯片。

針對(duì)CMOS的閂鎖效應(yīng),板級(jí)設(shè)計(jì)可以從以下幾個(gè)方面采取相應(yīng)的防御措施:

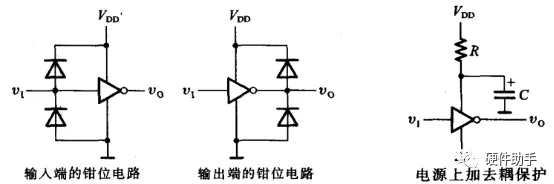

在輸入端和輸出端加鉗位電路,使輸入和輸出不超過規(guī)定電壓,二極管通常選用導(dǎo)通壓降較低的鍺二極管或肖特基勢壘二極管;

芯片的電源輸入端加去耦電路,防止VDD端出現(xiàn)瞬間的高壓;

在VDD和外電源之間加限流電阻,即使有大的電流也不讓它進(jìn)去,但這種方法降低了電源的利用率,在電流消耗較小的情況下使用;

上電時(shí)序:當(dāng)系統(tǒng)由幾個(gè)電源分別供電時(shí),開關(guān)要按下列順序:開啟時(shí),先開啟COMS電路的電源,再開啟輸入信號(hào)和負(fù)載的電源;關(guān)閉時(shí),先關(guān)閉輸入信號(hào)和負(fù)載的電源,再關(guān)閉COMS電路的電源。

5、guard ring

guard ring是為了防止閂鎖效應(yīng),隔離噪聲,提供襯底連接的作用。保護(hù)環(huán)分為兩種:多數(shù)載流子保護(hù)環(huán)和少數(shù)載流子保護(hù)環(huán)。guard ring分為兩種:double guard ring和dual guard ring,把兩個(gè)P型環(huán)接GND的稱作double guard ring,把通常的P型和N型的稱作dual guard ring。

編輯:hfy

-

CMOS

+關(guān)注

關(guān)注

58文章

5724瀏覽量

235707 -

VDD

+關(guān)注

關(guān)注

1文章

312瀏覽量

33309 -

GND

+關(guān)注

關(guān)注

2文章

539瀏覽量

38787

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

淺談IGBT的閂鎖效應(yīng)

閂鎖效應(yīng)(Latch-up)原理及其抑制方法解析

芯片設(shè)計(jì)都不可避免的考慮要素—閂鎖效應(yīng)latch up

Latch UP

什么是閂鎖效應(yīng)?

如何解決CMOS電路中的閂鎖效應(yīng)在現(xiàn)實(shí)生活中有什么具體的...

失效分析和熱點(diǎn)測試

寄生電路的效應(yīng):Latch-Up(鎖定)

什么是閂鎖效應(yīng)?閂鎖效應(yīng)的觸發(fā)方式有哪幾種?

CMOS閂鎖效應(yīng)

Latch-Up White Paper

CMOS電平的介紹和CMOS的閂鎖效應(yīng)詳細(xì)概述

避免電路中閂鎖效應(yīng)的3個(gè)實(shí)用方法!

單片機(jī)發(fā)生閂鎖效應(yīng)的因素,如何防止發(fā)生單片機(jī)閂鎖效應(yīng)?

芯片失效機(jī)理之閂鎖效應(yīng)

CMOS的閂鎖效應(yīng):Latch up的原理分析

CMOS的閂鎖效應(yīng):Latch up的原理分析

評(píng)論