閂鎖效應,latch up,是個非常重要的問題。現在的芯片設計都不可避免的要考慮它。我今天就簡單地梳理一下LUP的一些問題。

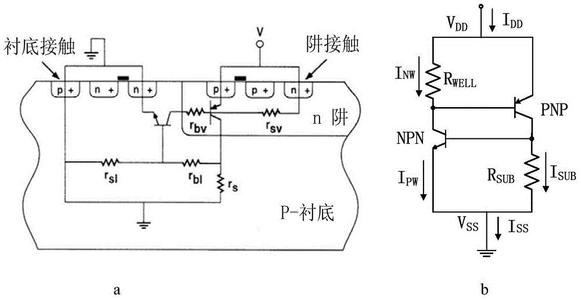

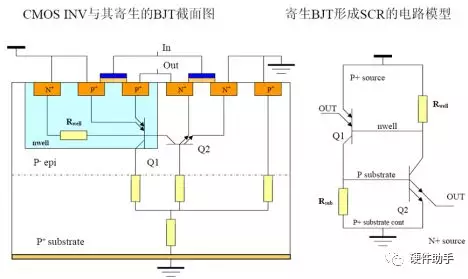

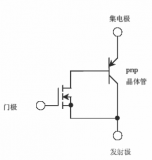

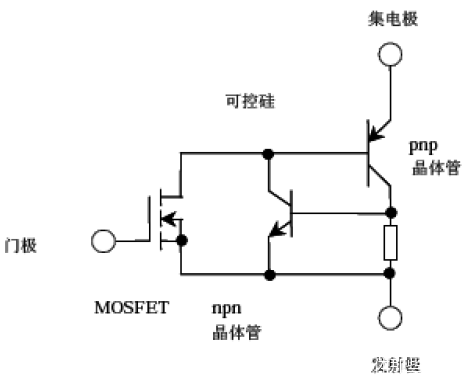

啥是所謂的latch up呢?一句話總結起來很簡單:CMOS中形成了兩個BJT,基極和集電極接在了一起,形成正反饋回路,電流大到一定程度可能會使芯片失效甚至燒壞芯片。這兩個BJT其實就是一個npnp的結構,pmos的源/漏、n阱、nmos的p襯底構成一個pnp的BJT,而pmos的n阱、nmos的p襯底、nmos的源漏構成一個npn的BJT。

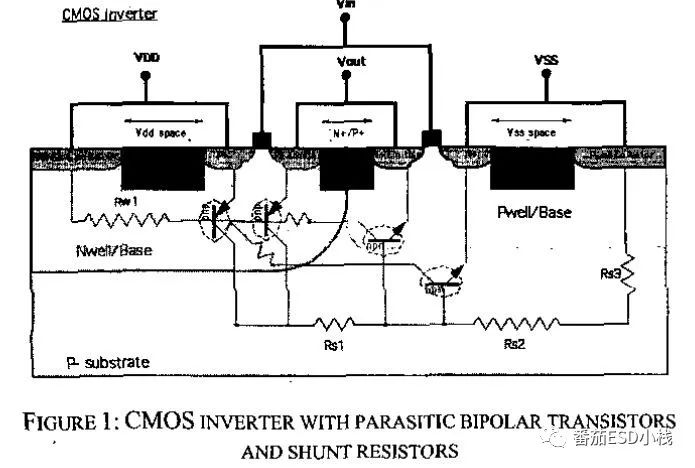

這兩個BJT共用了nmos的p substrate、pmos的n well,其等效電路圖相當于這兩個BJT的base和collector接在一起了。我在網上隨便找了個圖大家可以參考,圖中的各種電阻啥的可以忽略,就看三極管怎么連的就行。

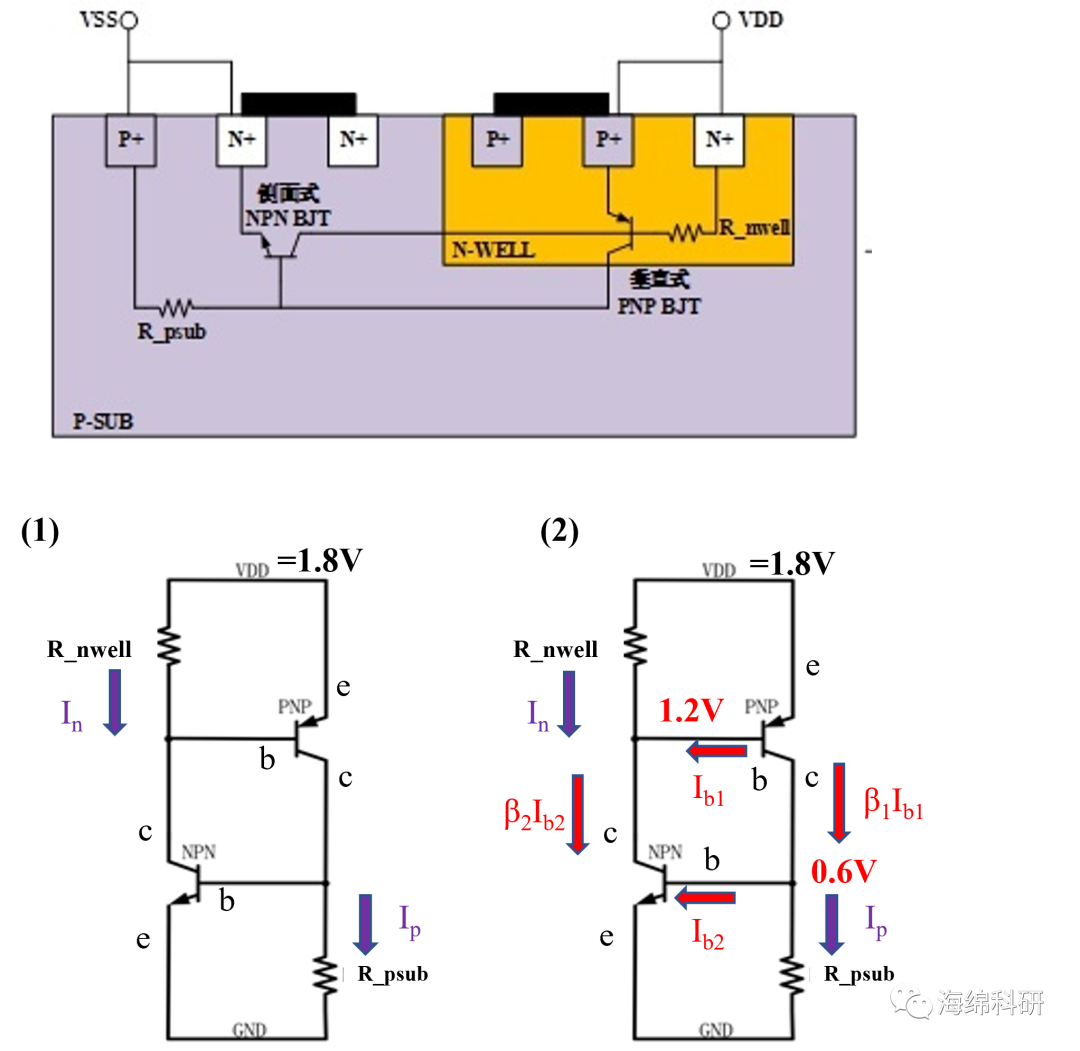

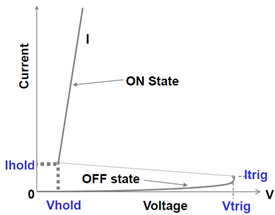

重點來了,假設現在有一個擾動,使得pmos的n well電勢小于Vdd,其電勢差大于PNP的開啟電壓,發射極正偏,PNP就工作在放大狀態了,集電極出來的放大的電流將是基極電流的一個倍數,而這個電流也相當于NPN基極電流,此時NPN也會在放大區,NPN放大出來的電流又是PNP的基極電流。這就形成了一個正反饋的回路,你放大我,我放大你,只要這兩個放大系數之積大于1,那么這里的電流就會越來越大,直至爆炸。

開個玩笑,爆炸應該是不會爆炸的,但是芯片停止工作是一定的。這個時候就只能把芯片斷電,然后重新開啟才行了——前提是芯片電路沒有被燒壞。想想如果一個芯片隔一會必須斷電一次,那誰受得了,所以這個latch up一定要消除才行。我就講一講目前我所能理解的集中消除latch up的方法。

第一,從源頭出發,既然latch up的發生來自于擾動,那我們就盡量消除這個擾動對我們cell的影響。我這里所謂的擾動,基本都是來自于靜電,所以越靠近IO的cell越要注意latch up的問題。一般來說,越靠近IO的cell所要遵循的LUP rule越嚴格。一種方法是加guard ring,可以減小噪聲和靜電的影響。這也是我目前唯一知道的方法哈哈。

第二,可以在BJT的放大系數上做文章。只要能保證兩個BJT的beta之積小于1,就能有效消除latch up。一種方法是盡量讓nmos和pmos隔的遠一些,這個具體原理我還不是很清楚,需要非常深入的器件知識才行。

第三,盡量保證BJT基極與發射極電勢相差不大,也就是不讓BJT工作在放大區。一種方法是把n well接Vdd,p substrate接Vss。注意,這里可能就有疑惑了,我在上學的時候學的標準的CMOS本來就是n well接Vdd,p substrate接Vss的呀。實際上在老的工藝貌似確實是是這樣,每一個cell都是這么接,但是這樣會有點浪費面積。現在的工藝cell的layout應該不會畫這部分了,而是需要我們后端擺放cell時候加進來tap cell,其作用就是接n well和p substrate到Vss和Vdd上。因為std cell一個一個排在一起的時候,它們的n well和p substrate是公用的,所以不需要每個cell都連,只需要隔一段距離擺一個tap cell就行了。這個方法可能也是和我們后端關系最大的了,前兩種多是layout要考慮的吧。

-

CMOS

+關注

關注

58文章

5721瀏覽量

235560 -

芯片設計

+關注

關注

15文章

1019瀏覽量

54908 -

BJT

+關注

關注

0文章

236瀏覽量

18185 -

閂鎖效應

+關注

關注

1文章

30瀏覽量

9393 -

基極電流

+關注

關注

1文章

32瀏覽量

3238

發布評論請先 登錄

相關推薦

CMOS的閂鎖效應:Latch up的原理分析

淺談IGBT的閂鎖效應

什么是閂鎖效應?

寄生電路的效應:Latch-Up(鎖定)

避免電路中閂鎖效應的3個實用方法!

芯片設計都不可避免的考慮要素—閂鎖效應latch up

芯片設計都不可避免的考慮要素—閂鎖效應latch up

評論