一、引言

集成電路是現(xiàn)代電子技術(shù)的基石,而外延片作為集成電路制造過(guò)程中的關(guān)鍵材料,其性能和質(zhì)量直接影響著最終芯片的性能和可靠性。本文將深入探討集成電路外延片的組成、制備工藝及其對(duì)芯片性能的影響。

二、集成電路外延片的組成

外延片是在經(jīng)過(guò)精細(xì)加工和嚴(yán)格處理的襯底之上,運(yùn)用特定的外延生長(zhǎng)技術(shù),精確生長(zhǎng)出一層或多層具備一定物理、化學(xué)和電學(xué)性能,以及特定晶體結(jié)構(gòu)和厚度的半導(dǎo)體薄膜。外延片主要由襯底和外延層兩部分組成。

(一)襯底

襯底是外延片的基礎(chǔ),為外延層提供生長(zhǎng)的基礎(chǔ)。常用的襯底材料包括單晶硅、碳化硅和藍(lán)寶石等。

單晶硅襯底:具有優(yōu)異的晶體完整性和電學(xué)性能,能為外延層提供理想的晶格匹配和生長(zhǎng)基礎(chǔ)。單晶硅襯底是集成電路制造中最常用的襯底材料,其純度、晶格完整性和電學(xué)性能對(duì)最終芯片的性能有著重要影響。

碳化硅襯底:具有高擊穿電場(chǎng)、高熱導(dǎo)率等特性,適用于高頻、高壓、高功率的集成電路應(yīng)用。碳化硅襯底在射頻功率器件、電力電子器件等領(lǐng)域有著廣泛的應(yīng)用前景。

藍(lán)寶石襯底:憑借良好的絕緣性能和化學(xué)穩(wěn)定性,在光電器件等領(lǐng)域的外延片中應(yīng)用廣泛。藍(lán)寶石襯底在LED、激光器等光電器件的制造中發(fā)揮著重要作用。

(二)外延層

外延層是在襯底上生長(zhǎng)的一層或多層半導(dǎo)體薄膜,其性能直接影響最終芯片的性能。外延層的組成、摻雜濃度、晶體結(jié)構(gòu)和厚度等參數(shù)都是精確控制的。

組成:外延層的組成與襯底材料可以相同(同質(zhì)外延)也可以不同(異質(zhì)外延)。同質(zhì)外延生長(zhǎng)的外延層和襯底是同一種材料,具有相同的晶格結(jié)構(gòu)和化學(xué)性質(zhì);異質(zhì)外延生長(zhǎng)的外延層與襯底材料不同,或者生長(zhǎng)化學(xué)組分、物理結(jié)構(gòu)與襯底完全不同的外延層。

摻雜濃度:外延層的雜質(zhì)濃度可通過(guò)精確的摻雜工藝進(jìn)行調(diào)控。如在制造高性能晶體管時(shí),可在N型外延層中精確控制磷、砷等雜質(zhì)原子的濃度,以實(shí)現(xiàn)特定的電子遷移率和導(dǎo)電性。

晶體結(jié)構(gòu)和厚度:外延層的晶體結(jié)構(gòu)缺陷密度極低,可確保載流子在其中的高效傳輸,減少散射和損耗。同時(shí),外延層的厚度也是精確控制的,以滿(mǎn)足不同器件的設(shè)計(jì)要求。

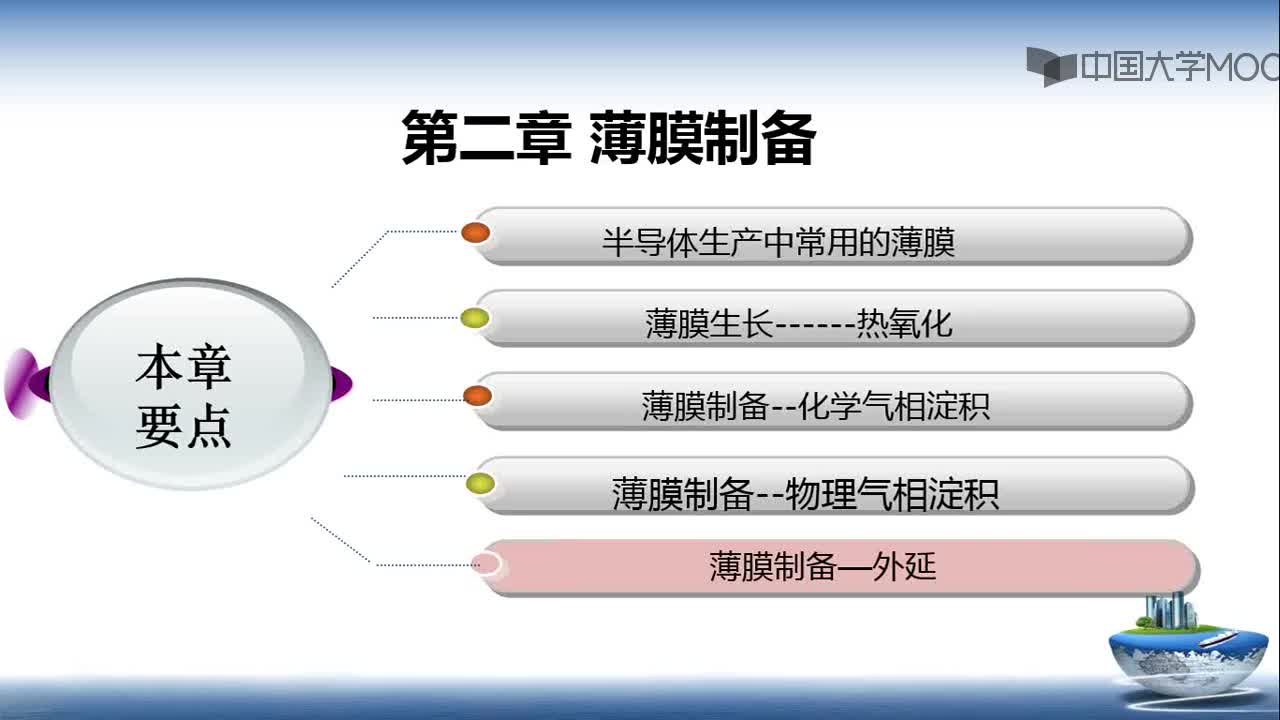

三、集成電路外延片的制備工藝

外延片的制備工藝是集成電路制造過(guò)程中的關(guān)鍵步驟之一,其工藝水平直接影響最終芯片的性能和可靠性。常用的外延片制備工藝包括化學(xué)氣相沉積(CVD)和分子束外延(MBE)等。

(一)化學(xué)氣相沉積(CVD)

化學(xué)氣相沉積是外延片制備中最常用的方法之一。以金屬有機(jī)化學(xué)氣相沉積(MOCVD)為例,在生長(zhǎng)氮化鎵(GaN)外延層時(shí),通常以三甲基鎵(TMGa)和氨氣(NH?)作為源氣體,在高溫和催化劑的作用下,TMGa分解出鎵原子,NH?分解出氮原子,它們?cè)谝r底表面發(fā)生化學(xué)反應(yīng)并沉積,逐漸生長(zhǎng)出GaN外延層。通過(guò)精確控制反應(yīng)溫度、氣體流量、壓力等參數(shù),可以精確調(diào)控外延層的生長(zhǎng)速率、厚度和質(zhì)量。

(二)分子束外延(MBE)

分子束外延是一種高真空度下的外延生長(zhǎng)技術(shù)。在MBE系統(tǒng)中,有多個(gè)分別裝有不同元素的蒸發(fā)源,如生長(zhǎng)砷化鎵(GaAs)外延層時(shí),將裝有鎵(Ga)和砷(As)的蒸發(fā)源加熱,使Ga和As原子蒸發(fā)成束狀射向襯底。利用反射式高能電子衍射等技術(shù)實(shí)時(shí)監(jiān)測(cè)襯底表面的原子生長(zhǎng)情況,精確控制蒸發(fā)源的溫度和蒸發(fā)時(shí)間,就能實(shí)現(xiàn)原子級(jí)別的精確生長(zhǎng)。MBE技術(shù)可以生長(zhǎng)出厚度僅為幾個(gè)原子層的超薄外延層,用于制造量子阱、量子點(diǎn)等先進(jìn)的半導(dǎo)體器件。

四、集成電路外延片對(duì)芯片性能的影響

外延片作為集成電路制造過(guò)程中的關(guān)鍵材料,其性能和質(zhì)量直接影響著最終芯片的性能和可靠性。

(一)提高芯片性能

提高電子遷移率:在高速集成電路中,通過(guò)在硅外延層中采用應(yīng)變工程技術(shù),可使硅原子晶格產(chǎn)生一定的拉伸或壓縮應(yīng)變,能顯著提高電子或空穴的遷移率。這有助于提高器件的工作頻率和響應(yīng)速度。

實(shí)現(xiàn)復(fù)雜功能:在系統(tǒng)級(jí)芯片(SoC)中,需要在同一外延片上集成多種不同功能的器件。如在CMOS工藝中,通過(guò)在外延片上依次生長(zhǎng)不同摻雜類(lèi)型和濃度的外延層,可分別用于制作PMOS和NMOS晶體管,再結(jié)合金屬互連等工藝,就能實(shí)現(xiàn)邏輯運(yùn)算、存儲(chǔ)等多種復(fù)雜功能。

優(yōu)化電學(xué)性能:外延層的摻雜濃度、晶體結(jié)構(gòu)和厚度等參數(shù)都是精確控制的,可以?xún)?yōu)化器件的電學(xué)性能。例如,通過(guò)精確控制外延層的摻雜濃度,可以調(diào)整器件的閾值電壓、漏電流等關(guān)鍵參數(shù),提高器件的可靠性和穩(wěn)定性。

(二)提高芯片可靠性

減少散射和損耗:外延層的晶體結(jié)構(gòu)缺陷密度極低,可確保載流子在其中的高效傳輸,減少散射和損耗。這有助于提高器件的工作效率和降低功耗。

實(shí)現(xiàn)電氣隔離:在功率集成電路中,通常會(huì)生長(zhǎng)一層厚的絕緣外延層,如二氧化硅(SiO?)外延層,用于實(shí)現(xiàn)高壓器件與低壓器件之間的電氣隔離。這種絕緣外延層具有高擊穿電壓和低漏電特性,能有效防止不同電位區(qū)域之間的電流泄漏和信號(hào)串?dāng)_,確保電路在高電壓、大電流環(huán)境下的穩(wěn)定運(yùn)行。

提高熱穩(wěn)定性:某些特殊的外延層材料,如碳化硅襯底,具有高熱導(dǎo)率等特性,有助于提高器件的熱穩(wěn)定性。在高溫環(huán)境下,碳化硅襯底能夠迅速將熱量散發(fā)出去,避免器件因過(guò)熱而損壞。

五、結(jié)論

集成電路外延片作為集成電路制造過(guò)程中的關(guān)鍵材料,其組成、制備工藝及對(duì)芯片性能的影響是半導(dǎo)體技術(shù)領(lǐng)域的重要研究課題。通過(guò)精確控制外延層的組成、摻雜濃度、晶體結(jié)構(gòu)和厚度等參數(shù),可以顯著提高芯片的性能和可靠性。隨著半導(dǎo)體技術(shù)的不斷發(fā)展,外延片制備工藝也將不斷創(chuàng)新和完善,為集成電路產(chǎn)業(yè)的發(fā)展提供有力支撐。

未來(lái),隨著5G通信、人工智能、物聯(lián)網(wǎng)等新興技術(shù)的快速發(fā)展,對(duì)集成電路的性能和可靠性提出了更高要求。外延片作為集成電路制造過(guò)程中的關(guān)鍵材料,其研究和開(kāi)發(fā)將更加注重高性能、低成本和環(huán)保等方面。通過(guò)不斷優(yōu)化外延片制備工藝和提高材料性能,將有助于推動(dòng)集成電路產(chǎn)業(yè)的持續(xù)發(fā)展和創(chuàng)新。

-

集成電路

+關(guān)注

關(guān)注

5391文章

11614瀏覽量

362795 -

半導(dǎo)體封裝

+關(guān)注

關(guān)注

4文章

271瀏覽量

13805 -

外延片

+關(guān)注

關(guān)注

0文章

34瀏覽量

9733

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

半導(dǎo)體制造之外延工藝詳解

#硬聲創(chuàng)作季 #集成電路 集成電路制造工藝-02.5外延生長(zhǎng)-外延生長(zhǎng)

[分享]全方位剖析BGA布線(xiàn)規(guī)則與技巧

雙極型集成電路的特點(diǎn)有哪些?

詳解數(shù)字集成電路分類(lèi)是怎么分的?

什么是集成電路?集成電路的分類(lèi)

集成電路工藝專(zhuān)題實(shí)驗(yàn) Topic Experiments o

集成電路構(gòu)成的光柵電路

集成電路外延片詳解:構(gòu)成、工藝與應(yīng)用的全方位剖析

集成電路外延片詳解:構(gòu)成、工藝與應(yīng)用的全方位剖析

評(píng)論