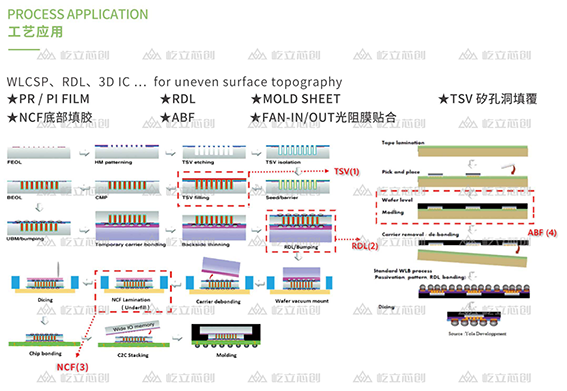

高性能計算機中日益廣泛采用“處理器+存儲器”體系架構,近兩年來Intel、AMD、 Nvidia都相繼推出了基于該構架的計算處理單元產品,將多個存儲器與處理器集成在一個TSV硅轉接基板上,以提高計算處理單元的整體性能。

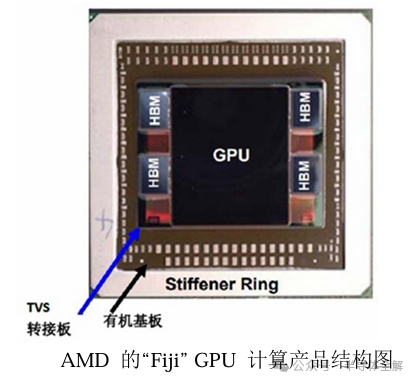

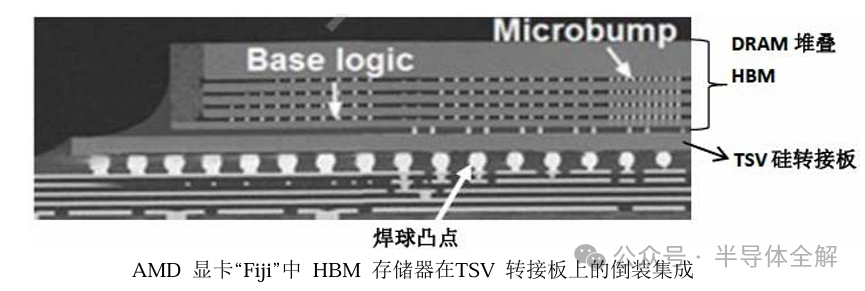

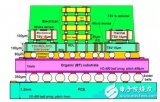

2015年,AMD推出新一代旗艦級顯卡“Fiji”,下圖為“Fiji”計算產品結構圖。

在TSV 硅轉接板上4顆高帶寬存儲器顯存(High Bandwidth Memory,HBM)依靠在臺積電的28nm工藝節點制造的GPU芯片兩側,TSV硅轉接基板采用UMC的65nm工藝,尺寸28mm×35mm。

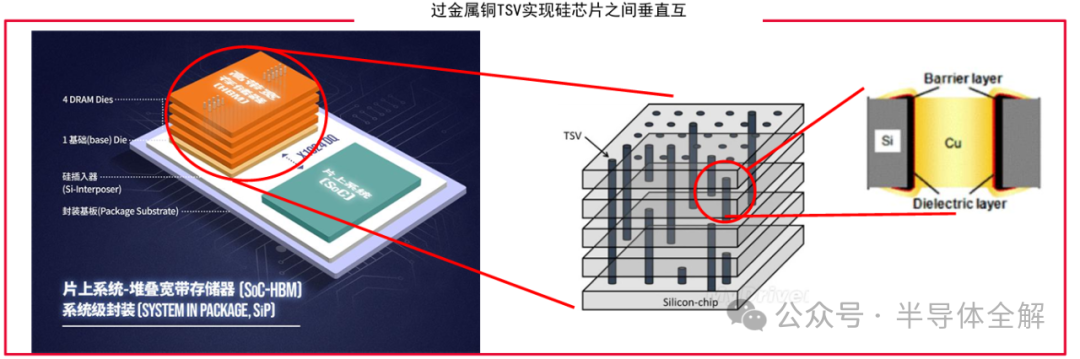

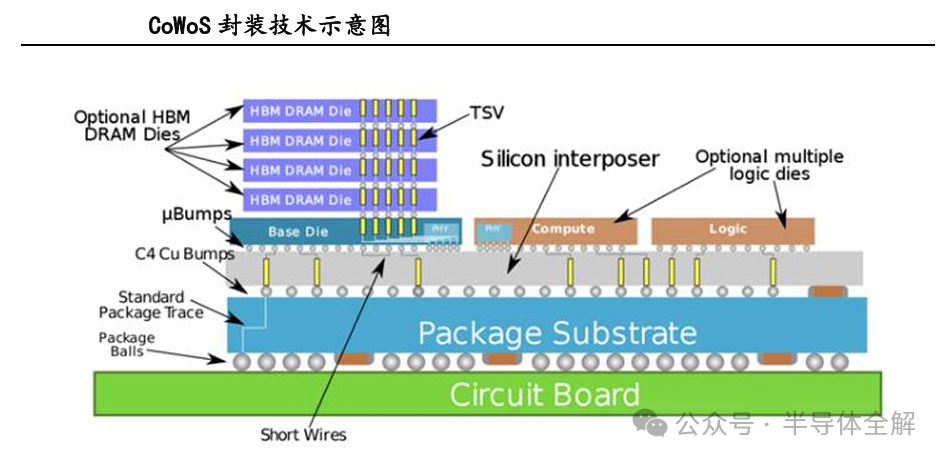

HBM是一種封裝存儲器,可通過同一封裝內的硅中介層與SoC集成在一起。通過這種方法,便可以克服傳統片外封裝存在的數據I/O封裝引腳限制的最大數量。

DRAM通過堆疊的方式,疊在一起,Die之間用TVS方式連接;DRAM下面是DRAM邏輯控制單元,對DRAM進行控制;

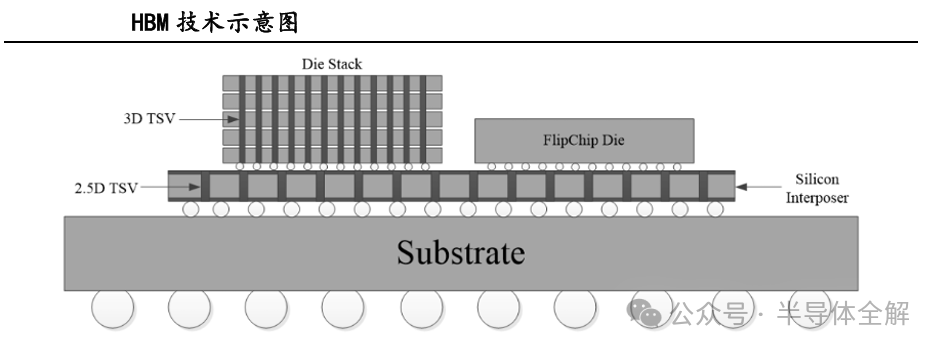

GPU和DRAM通過uBump和Interposer(起互聯功能的硅片)連通Interposer再通過Bump和 Substrate(封裝基板)連通到BALL;最后BGA BALL 連接到PCB上。

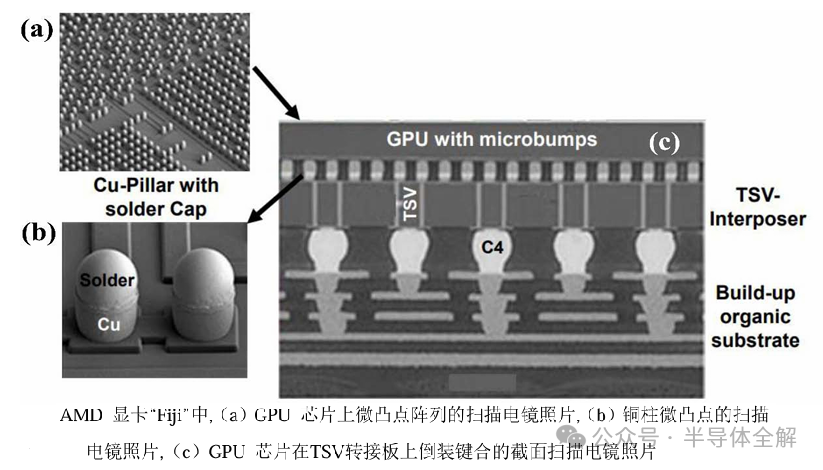

該GPU芯片外接形式為銅柱焊錫帽的微凸點陣列,為提高硅轉接板TSV通孔的可靠性,采取了TSV 通孔冗余設計。即多個TSV通孔對應一個焊球凸點。

GPU和HBM顯存間的互連已經在TSV 硅轉接板的RDL層上完成,使得 “GPU+4HBM”的對外引腳數遠小于GPU本身的對外引腳數,TSV硅轉接板成功實現了GPU芯片的高密度窄節距的微凸點陣列到外接有機基板的低密度寬節距的焊球凸點間的轉換。

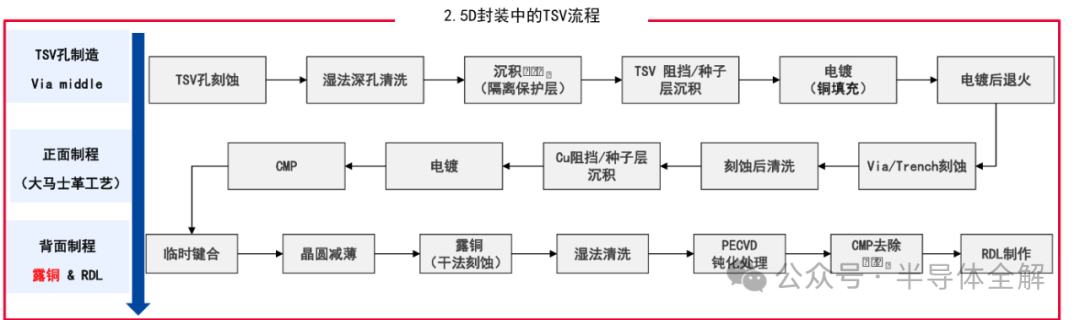

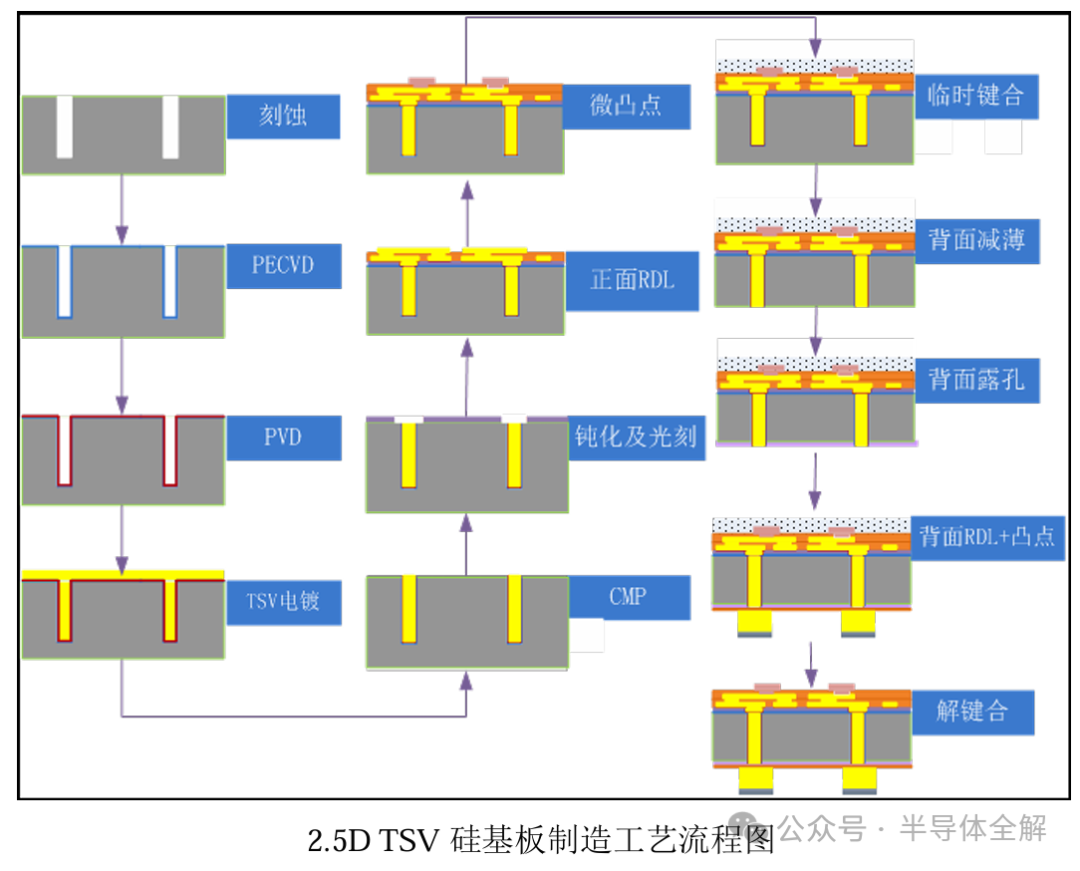

TSV制造工序主要包括以下幾個步驟:

首先,在芯片的硅襯底上采用DRIE(Deep Reactive Ion Etching,深反應離子刻蝕)的方法刻孔,制造出直徑數微米、深度50-100μm的盲孔;

然后,依次采用CVD或者PVD方法在盲孔側壁制作出厚度幾十納米到幾百納米的絕緣層/阻擋層/種子層;

然后,將芯片放在硫酸銅溶液中,以種子層為陰極進行電鍍,將盲孔填充滿;

最后,將背面多余的硅襯底去除,露出TSV填銅,形成芯片上表面下表面的垂直互連通道。

其詳細的工藝過程如下圖所示:

(1)晶圓通孔刻蝕工藝

通過TSV刻蝕工藝在硅襯底上制備高深寬比的TSV盲孔結構,其形貌、尺寸甚至側壁粗糙程度都將對后續工藝產生影響。

TSV硅刻蝕工藝通常有電化學腐蝕技術、激光刻蝕和基于等離子體的反應離子深刻蝕等幾種方法。

隨著TSV孔徑的減小、深寬比的增大,業界開發了基于深反應離子刻蝕(Deep Reactive Ion Etching,DRIE)技術的Bosch工藝。

反應離子刻蝕(ReactiveIon Etching,RIE)工藝,是采用物理轟擊和化學反應雙重作用的刻蝕,使得它成為目前應用范圍最為廣泛的干法刻蝕技術。

Bosch工藝通過刻蝕和保護兩個步驟交替進行來提高TSV的各向異性,保證TSV通孔的垂直度。

在TSV通孔的Bosch工藝刻蝕過程中,首先向工藝腔室中通入SF6氣體,在射頻源的作用 在SF6電離成為等離子體,等離子體中的高活性的F原子基團與未制備掩膜區域硅發生化學反應生成可揮發的硅氟化合物。

而等離子體中的高能離子則在偏壓源下獲得能量發生物理轟擊,不僅能為硅氟化學反應提供能量還能夠加速表面生成物的解吸附。

在TSV通孔的Bosch工藝保護過程中,停止通入SF6氣體,通入C4F8氣體,使C4F8電離形成等離子體,但并不會對硅進行刻蝕,而是在所有暴露的硅表面形成一定厚度的碳氟聚合物層,充當保護鈍化層。

最后物理轟擊使得TSV孔的底部聚合物被移除,從而裸露在SF6等離子體中,但已刻蝕的TSV孔側壁仍然被碳氟聚合物覆蓋,這樣就避免了高活性的F自由基與TSV孔側壁繼續反應,從而能夠保證刻蝕的方向垂直向下。

通過不斷重復這一過程就能夠形成垂直的TSV孔。

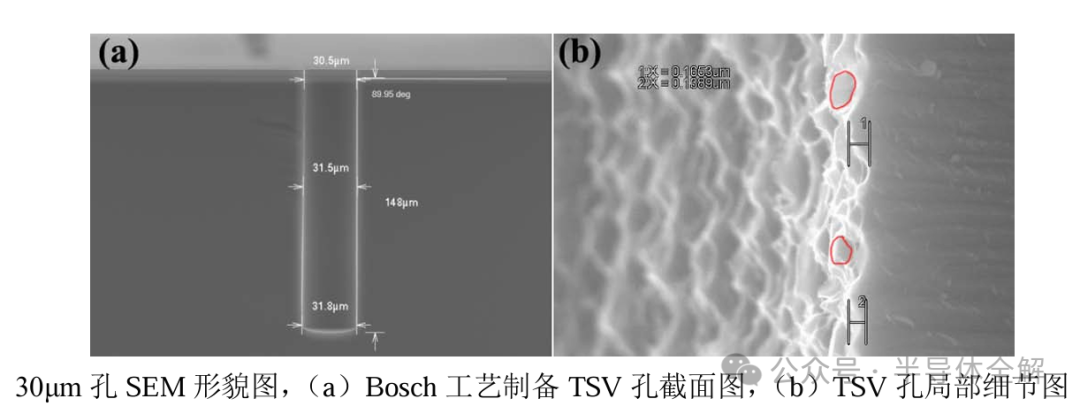

下圖是30μm孔徑TSV刻蝕后截面圖,可以看出Bosch工藝制備TSV孔垂直取向性優異,孔底尺寸和孔口尺寸差異微小。刻蝕反應和保護反應交替進行將會在TSV孔壁產生扇貝紋如圖所示,優化扇貝紋的尺寸也是Bosch刻蝕工藝研究的重點之一。

(2)晶圓TSV側壁絕緣層工藝

TSV孔內絕緣層用于實現硅襯底與孔內傳輸通道的絕緣,防止TSV通孔之間漏電和TSV間的串擾。

TSV孔內絕緣層的質量將直接影響TSV硅轉接板的信號完整性和電源完整性,是保證2.5D TSV轉接板性能的關鍵工藝之一。

在TSV孔刻蝕和深孔清洗完畢后,在TSV孔壁沉積絕緣材料形成孔壁介質絕緣層,孔壁絕緣介質層需要完全覆蓋TSV孔的內壁和TSV硅轉接基板表面以達到良好的絕緣性能。

TSV孔壁絕緣介質材料選用無機介質材料,如二氧化硅、氮化硅、或二氧化硅和氮化硅構成的復合材料。

研究表明二氧化硅與硅界面的界面缺陷越少,對硅表面的鈍化性能越優異,漏電流更低,所以優先選用二氧化硅作為孔壁絕緣介質層。

目前TSV孔壁無機絕緣介質材料的常用制備方法包括PECVD、SACVD、ALD和熱氧化法。PECVD可以實現較低的沉積溫度,如200℃以下,但對于孔徑較小且深寬比較大的垂直TSV孔的孔壁臺階覆蓋率不足;

SACVD的孔壁臺階覆蓋率優于PECVD,但沉積溫度較高,通常在400℃及以上;

ALD的孔壁臺階覆蓋率能達到80%以上,但沉積速度慢;

熱氧化法制備的二氧化硅層結構致密、孔壁臺階覆蓋率高,但熱氧化工藝溫度通常都在1000℃以上,同時熱氧化工藝可以在一爐中同時氧化多片,成本較低。

在2.5DTSV轉接板工藝過程中,由于TSV深寬比較大,傳統的單一的絕緣介質成膜技術無法滿足其臺階覆蓋要求,需開發新的孔壁絕緣層制備方法。

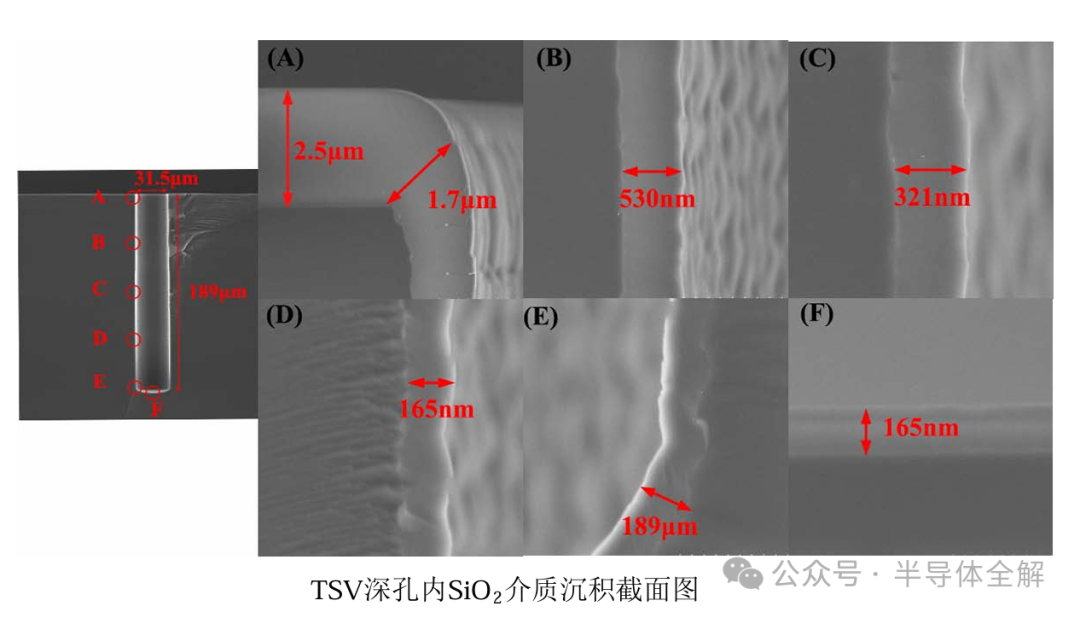

下圖為TSV孔內制備SiO2介質層SEM截面圖, 可知TSV孔頂部SiO2介質層厚度較大,沿著孔內壁向下孔壁沉積SiO2膜層后逐漸減小, 孔內均已完全覆蓋SiO2介質材料,無SiO2缺失區域。

(3)晶圓TSV側壁阻擋層/種子層工藝

在2.5DTSV轉接板工藝中,一般使用Cu作為TSV通孔內部金屬互聯材料。在電鍍Cu填充TSV通孔前,需要在TSV孔內制備電鍍阻擋/種子層,一般選用Ti、Ta、TiN、TaN等材料。

TSV電鍍種子層起著與電鍍電極電連接并實現TSV孔填充的作用。TSV深孔金屬濺射影響因素眾多,主要有濺射功率、基底溫度、濺射氣體純度、工藝壓力、設備結構、靶材與后處理等,都對TSV深孔金屬濺射有一定的影響。

對于 TSV 工藝來說,最需要關注的就是TSV深孔金屬濺射的覆蓋率,因為金屬的臺階覆 蓋率直接影響到后續TSV深孔電鍍工藝。若金屬濺射連續性差,會導致后續深孔電鍍形成空洞,會嚴重影響到TSV通孔可靠性。因此,實現粗糙TSV側壁的高粘附全覆蓋PVD工藝是實現TSV孔內完整電鍍填充的前置工藝。與其他阻擋層和種子層沉積工藝相比,磁控濺射工藝沉積Ti/Cu阻擋層/種子層的濺射效率和沉積效率以及對靶材的利用率更高。

優化磁控濺射工藝參數可以實現TSV孔內Ti/Cu阻擋層/種子層的全面覆蓋,為下一步電鍍填充提供基礎。

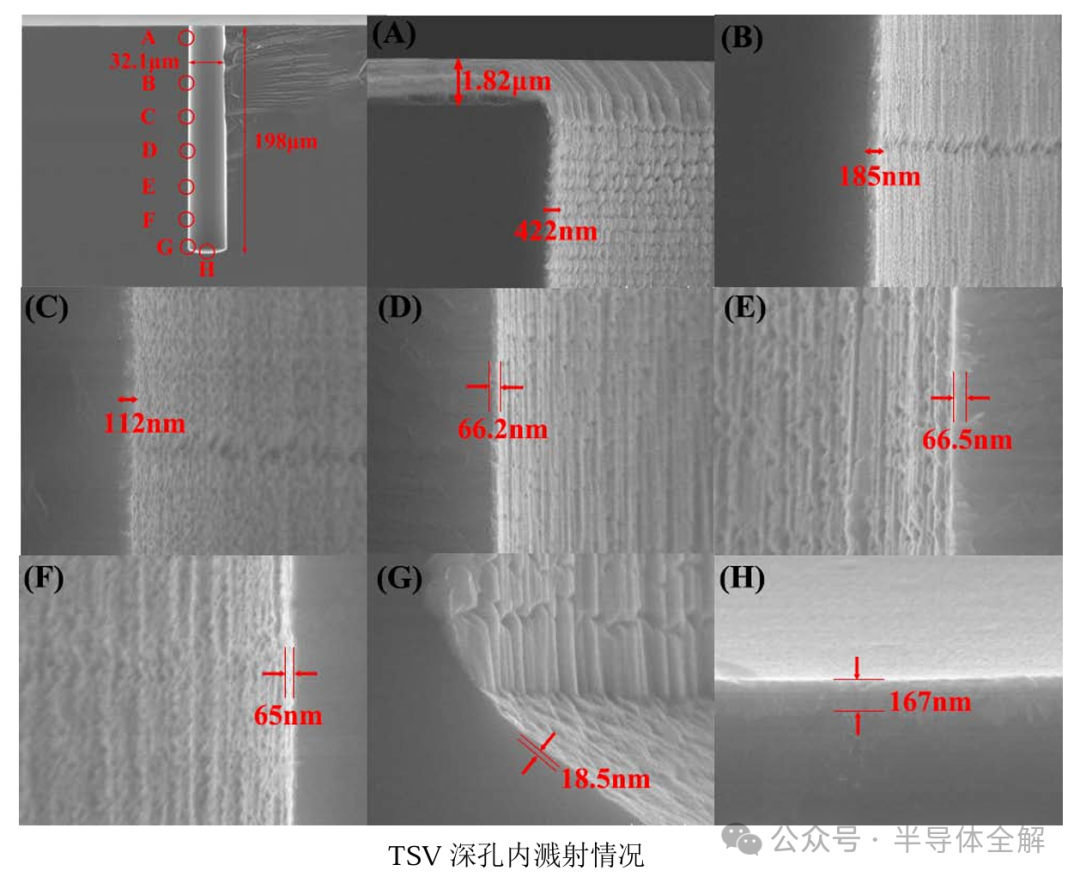

下圖為采用磁控濺射進行孔徑30μm,深寬比為7:1的TSV孔內Ti/Cu的濺射沉積結果,利用SEM觀察TSV孔內濺射覆蓋情況。可知TSV孔內均完整覆蓋了一層Ti/Cu金屬膜,TSV孔開口處膜層厚度最大,延孔壁向下膜層厚度迅速減小,孔底部過渡區域金屬膜層厚度最小,Ti/Cu阻擋層/種子層全部覆蓋TSV孔內壁無缺失出現。

(4)晶圓TSV電鍍填充工藝

TSV 孔電鍍填充是實現TSV硅轉接基板正背面導通和形成垂直方向的電流、信號通路的關鍵工藝,填充效果的好壞將直接影響后續器件的電學性能和可靠性。

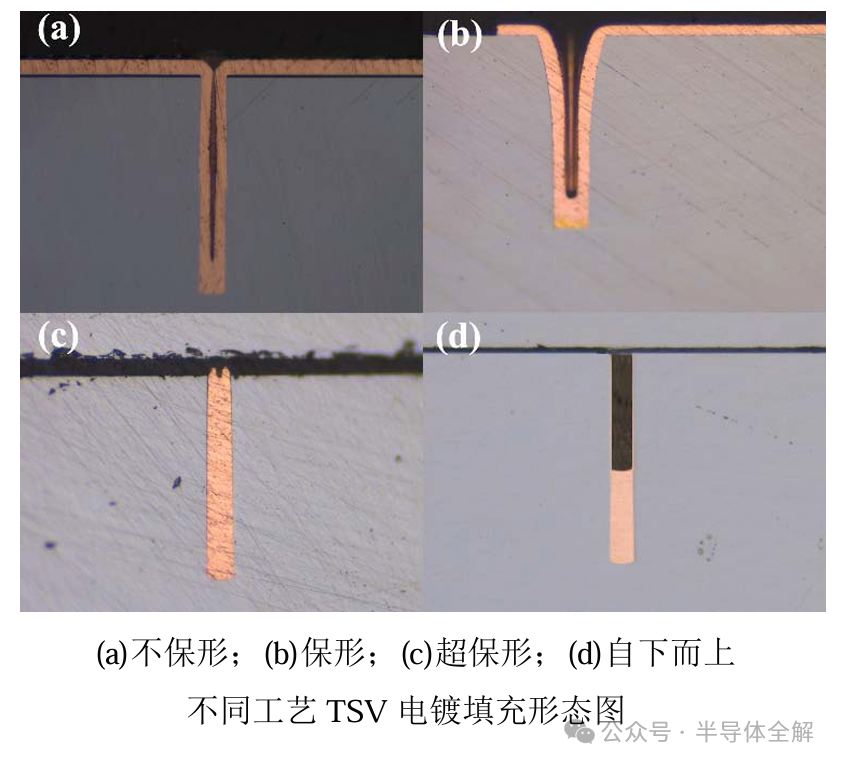

TSV電鍍填充共有四種工藝方法,分別為:不保形的,保形的,超保形的和自底向上生長的電鍍填充工藝,不同電鍍工藝填充效果如下圖所示。

四個階段進程代表著對TSV深孔電鍍藥水和晶圓電鍍機設備研發的各個時期。隨著對TSV深孔電鍍藥水體系研發的認識,以及配套設備的優化改進,實現最理想的自底向上電鍍。這種方式,一方面實現了孔底的填充效果,同時抑制了通孔側面和頂部的電化學抑制作用,實現了高深寬比TSV通孔電鍍填充完整性。

從TSV深孔電鍍液角度考慮,影響TSV 填充的因素有主鹽濃度和各種添加劑濃度。主鹽濃度主要考慮銅離子濃度,確保了藥液的導電性。

添加劑主要包括整平劑、抑制劑、加速劑等,通過添加劑溶度調配保證了自底向上沉積,同時抑制了孔口沉積。

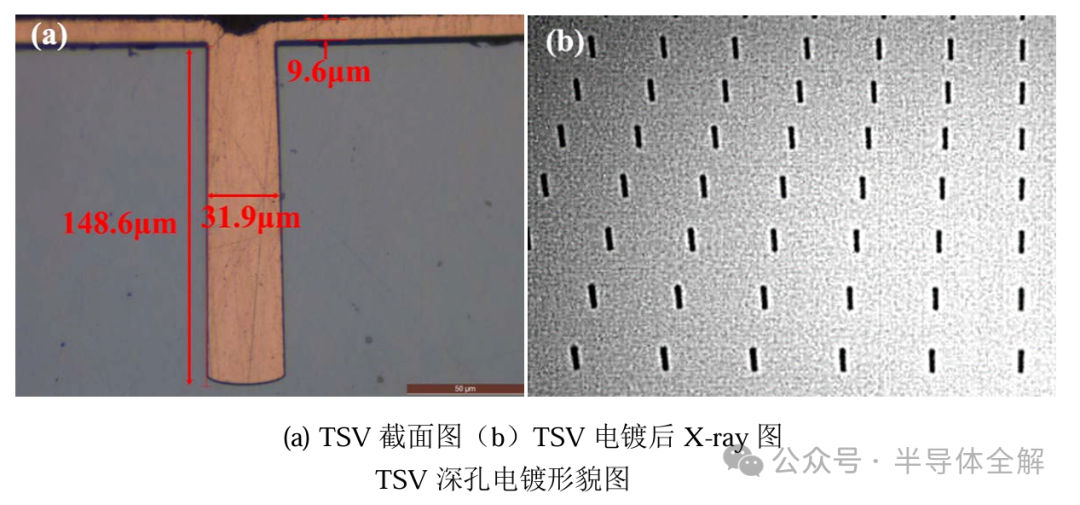

下圖為30μm孔徑TSV深孔電鍍填充Cu截面SEM圖,可見采用由下而上電鍍方法可以有效實現TSV孔內銅電鍍填充。圖(b)為TSV電鍍后X-ary檢測結果,可見自上而下電鍍工藝穩定性和均勻性良好,所有孔內均鍍滿,無漏鍍現象存在,滿足量產需求。

(5)晶圓正面CMP工藝

化學機械平坦化(ChemicalMechanical Planarization,CMP),是半導體前道中使材料表面實現全局平坦化的技術,主要應用于130nm以下制程中多層互連工藝中,確保高密度器件穩定性和可靠性。

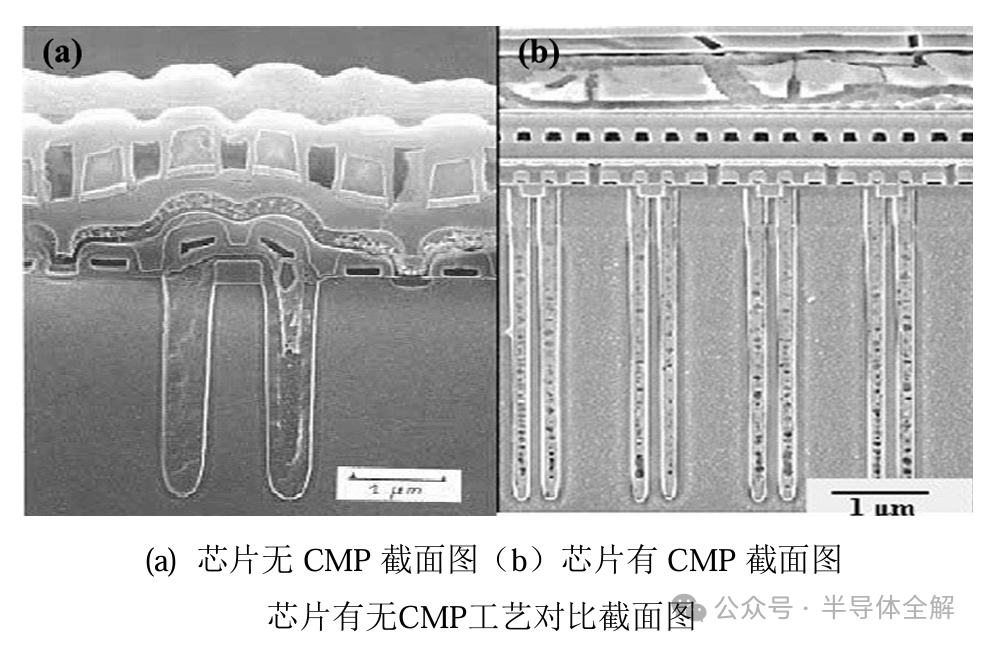

下圖為多層互連工藝中無CMP 工藝和有CMP 工藝時的截面圖。

由于TSV轉接板中涉及了高密度多層再布線,將CMP技術引入到TSV制程中,用于去除硅表面的SiO2介質層、阻擋層和種子層。

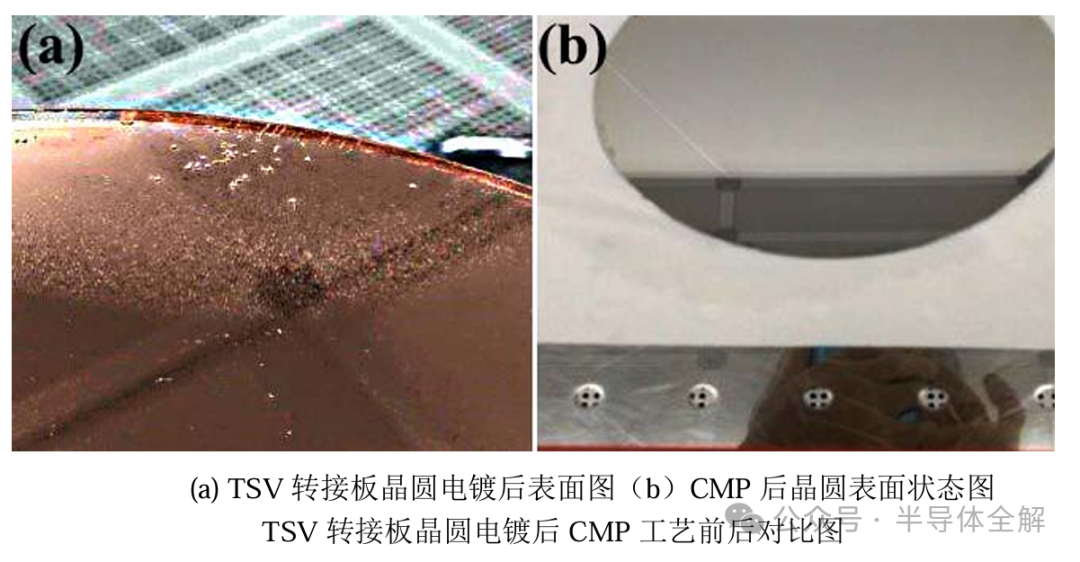

如下圖所示,通過CMP工藝去除表面電鍍的多余銅,要求銅的去除速率快,一致性高。其次去除阻擋層,要求拋光液的速率選擇性高,且盡量不出現缺陷;最后停止在介質絕緣層上。

在CMP工藝過程中,當Cu表面氧化物去掉時,拋光液中的化學成分就會氧化新露出的金屬表面,然后又被機械地磨除,這一過程重復進行直到多余銅金屬全部去除,去除表面Cu的TSV 晶圓,如圖(b)所示。

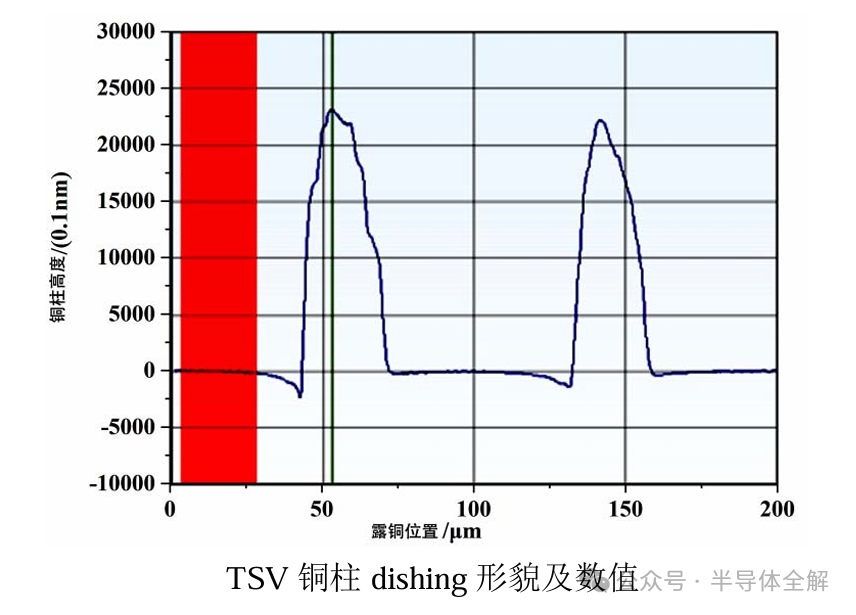

在2.5DTSV轉接板Cu CMP過程中,一般要求晶圓表面非均勻性小于3%,銅的去除速率大于2μm/min,碟形坑尺寸控制在-1μm至+3μm以內,且晶圓表面無劃傷出現。相反,在TSV阻擋層CMP中要求銅和隔離層的去除速率慢,阻擋層的去除速率快,只有這樣才能修正碟形坑且在不傷及下層介質絕緣層的情況下實現平坦化。

下圖為去除表面電鍍Cu后,表面蝶形坑測試圖。

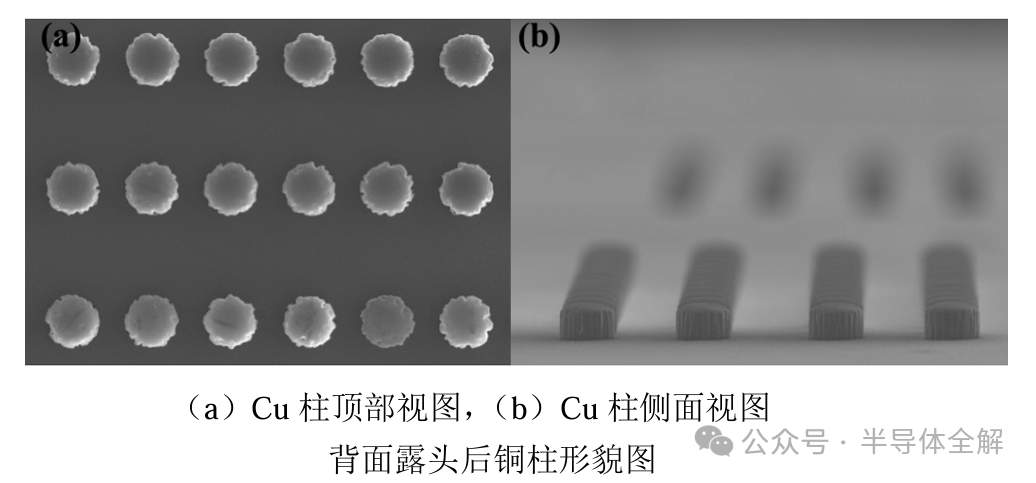

(6)晶圓TSV背面露頭工藝

TSV背面露頭技術是2.5D TSV轉接基板的關鍵工藝,包括晶圓減薄、干/濕法刻蝕工藝。在TSV立體集成工藝中,晶圓減薄工藝是需要極其關注的重要工藝。在TSV轉接板工藝中,需要晶圓厚度越來越小,一方面晶圓厚度越小其散熱特性越好,另一方面TSV深度也隨著越小,進而相應的互聯延遲和損耗也會減少。

一般晶圓厚度必須被減薄到100μm或者以下。但是當硅晶圓的厚度小于一定數量值時,材料內部生成的應力會隨著后續減薄工序的進行而增大使得硅片產生翹曲、粗糙和斷裂等缺陷,這些缺陷都會不同程度的影響后續工藝。

2.5D TSV轉接基板背面減薄之后,TSV柱子上面仍然覆蓋著一定厚度的殘余硅體,且表面會有一層硅損傷層,一般工藝上都是利用硅刻蝕工藝的高選擇性,從背面露出TSV銅柱。一般采用有兩種方法,干法工藝和濕法工藝。

濕法工藝為純化學腐蝕方法。

干法工藝為物理轟擊結合化學的刻蝕工藝。在2.5D TSV轉接板技術中,背面Cu露頭工藝關系到后續晶圓背面的電信號連接成功與否,要求露出的均勻性較高。考慮硅與二氧化硅的選擇比需要達到70:1,因此選擇采用干法工藝。

干法工藝不僅保證了TSV露頭部分具有足夠的高度,同時,露出來的導電銅柱外面還包覆著之前TSV工藝中所形成的絕緣層,避免了導電柱銅金屬與硅的直接接觸而造成對晶圓的污染(銅離子在硅中的擴散速度較快,室溫下其擴散系數可高達1.6×10E-9cm2/s),TSV轉接板背面干法露銅結果如圖所示。

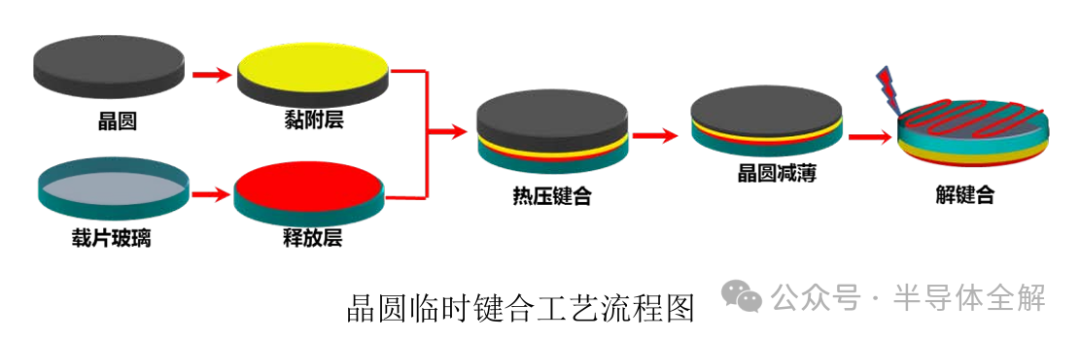

(7)超薄晶圓臨時鍵合/解鍵合工藝

減薄后的TSV轉接板晶圓易碎,需要臨時粘接在一個堅硬的載片上,完成后續的工藝以實現TSV轉接板背面工藝,該工藝過程為超薄晶圓臨時鍵合/解鍵合工藝。

經過近年來的研究和發展,該技術能夠和現有的半導體工藝很好的融合在一起,技術難度和成本要求相對較低,逐漸獨立于其它技術,成為解決薄晶圓拿持問題的關鍵。

臨時鍵合和解鍵合技術主要是利用承載晶圓來為薄晶圓提供足夠的機械支撐力。

臨時鍵合和解鍵合的一般方法就是通過臨時鍵合膠的作用,將2.5D TSV轉接板固定在臨時 載片上,從而增加薄晶圓的機械韌性,在完成晶圓減薄及隨后的背面互連結構的制備工步后,可從將TSV硅轉接基板從臨時載片上輕松剝離,清洗干凈后繼續加工直至封裝完成。

臨時鍵合和解鍵合的基本原理如下圖所示,具體步驟如下:

a.首先在臨時鍵合膠的作用下,將TSV轉接板和載片鍵合在一起;

b.在載片的機械支撐下,將TSV轉接板減薄到要求的厚度,完成背面工藝;

c.然后通過一定的方法再完整的將TSV轉接板與載片分離;

d.最后完成TSV轉接板表面鍵合膠的清洗。

采用激光臨時鍵合及解鍵合工藝對硅片進行拿持并完成后續工藝支撐,如下圖所示為臨時鍵合拿持超薄晶圓的工藝流程。

-

芯片

+關注

關注

456文章

51156瀏覽量

426480 -

TSV

+關注

關注

4文章

115瀏覽量

81532 -

先進封裝

+關注

關注

2文章

427瀏覽量

272

原文標題:一文詳解芯片先進封裝硅通孔(TSV)技術

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

3D IC集成與硅通孔TSV互連

什么是TSV封裝?TSV封裝有哪些應用領域?

先進封裝技術之爭 | 巨頭手握TSV利刃壟斷HBM市場,中國何時分一杯羹?

芯片先進封裝硅通孔(TSV)技術說明

芯片先進封裝硅通孔(TSV)技術說明

評論