簡介

TI60F100-DK是一款采用易靈思Ti60F100開發的評估板。

采用底板和核心板分離的方式來實現。單獨的核心板主要是考慮有客戶可能需要自己定制底板。

特性說明:

(1)單TypeC usb不僅支持供電,還同時實現JTAG下載、SOFT JTAG軟核調試及UART三個功能;

(2)千兆以太網。支持裕太的YT8531SH,高效穩定。

(3)HDMI輸出。LVDS實現HDMI輸出,分辨支持1080p@60,HDMI支持音頻輸出;

(4)外擴Flash。Ti60F100片上Flash為16Mb,而外擴Flash可以根據需要任意擴展;

(5)用戶LED。兩個;

(6)用戶按鍵。兩個;

(7)MIPI擴展。最大支持兩組MIPI x4發送,支持1組MIPI x4接收;

(8)LVDS擴展。10對差分對可用于LVDS接收或者發送;

(9)擴展IO。27個IO。

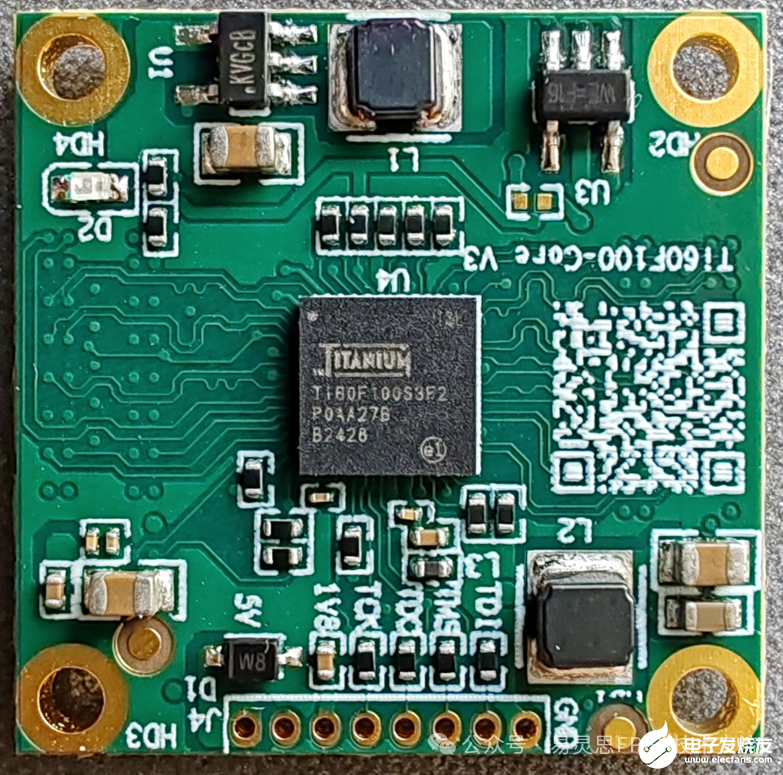

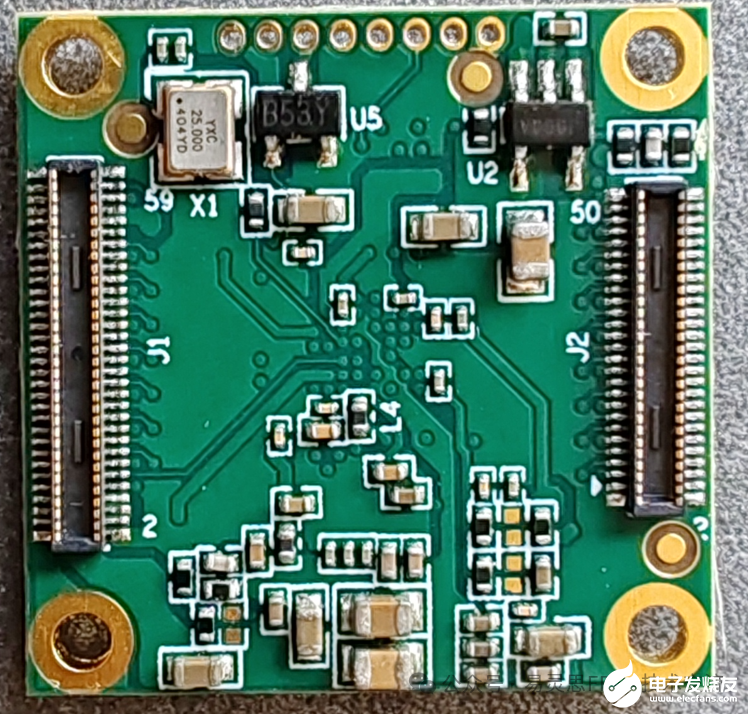

核心板

TI60F100-DK采用底板與核心板分離的結構。用戶可以通過核心板外擴自己的外設實現制定功能。以下是核心板的硬件設計說明。核心板主要是把IO引出來。方便客戶自己定義功能。

IO座子分別為50Pin和60Pin,可以確保防反插。Pin間距為0.4mm。

核心板尺寸為2.4cm x 2.4cm。

(1)核心板電源

核心板電源包括0.95V,1.8V和1.2V。保證核電壓及IO電壓供電,1.2V為MIPI Bank電壓供電。客戶可以根據需要配置Bank電壓為1.8V或者1.2V.

(2)時鐘

核心板配有一個25M的晶振

| 編號 | 時鐘頻率 | 管腳名 | 管腳號 | Bank電壓 | Bank |

| X1 | CLK_25M | GPIOL_P_07_CLK0_P | F4 | 1.8V | 1A_4B |

表1

(3)上電時序

Ti60F100對上電時序是有要求的。Demo板按上電要求進行了配置。

(4)差分對等長處理

核心板做了三組等長的差分對,以備客戶進行底板開發時有底板需求。等長為3mil,請確認三組分別等長,組與組之間沒有等長關系。

| 組 | 差分對 | 用作MIPI | 用作LVDS | 說明 |

|

第 一 組 |

GPIOR_PN_00 | MIPI_DATA | PLL_RX_CLK |

MIPI_RX_CLK:說明 該差分對可以用作MIPI RX的時鐘; PLL_RX_CLK:說明 該管腳可以連接 LVDS的參考時鐘。 |

| GPIOR_PN_01 | MIPI_DATA | DATA | ||

| GPIOR_PN_02 | MIPI_RX_CLK | DATA | ||

| GPIOR_PN_03 | MIPI_DATA | DATA | ||

| GPIOR_PN_04 | MIPI_DATA | DATA | ||

| GPIOR_PN_05 | MIPI_DATA | DATA | ||

| GPIOR_PN_06 | MIPI_DATA | DATA | ||

| GPIOR_PN_07 | MIPI_DATA | DATA | ||

| GPIOR_PN_08 | MIPI_DATA | DATA/GCLK | ||

| GPIOR_PN_09 | MIPI_DATA | DATA/GCLK | ||

|

第 二 組 |

GPIOR_PN_10 | MIPI_RX_CLK | DATA/GCLK | |

| GPIOR_PN_11 | MIPI_DATA | DATA/GCLK | ||

| GPIOR_PN_12 | MIPI_DATA | DATA | ||

| GPIOR_PN_13 | MIPI_DATA | DATA | ||

| GPIOR_PN_14 | MIPI_DATA | DATA | ||

|

第 三 組 |

GPIOL_PN_09 | MIPI_RX_CLK | DATA/GCLK | |

| GPIOL_PN_10 | MIPI_DATA | DATA/GCLK | ||

| GPIOL_PN_11 | MIPI_DATA | DATA | ||

| GPIOL_PN_12 | MIPI_DATA | DATA | ||

| GPIOL_PN_13 | MIPI_DATA | DATA | ||

| GPIOL_PN_18 | PLL_RX_CLK |

表2

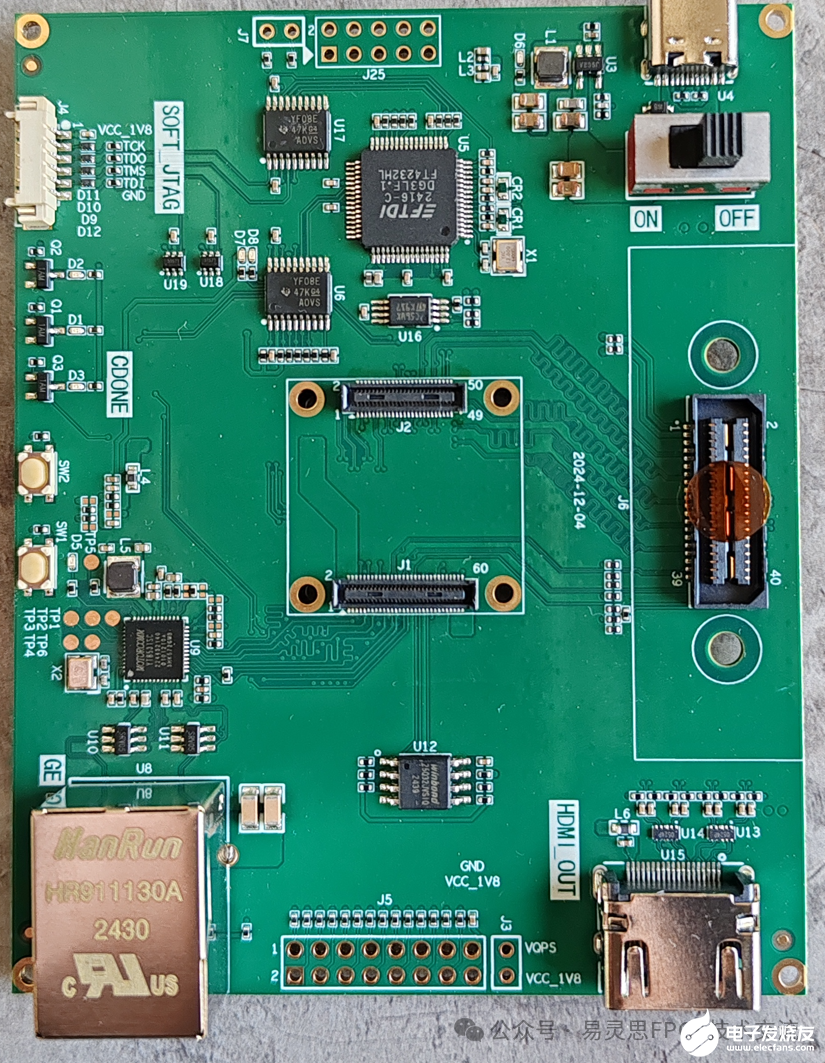

底板

目前底板主要提供了,尺寸為10x8cm

(1)電源

底板通過TypeC USB供電。使用方便簡單。另外只需要一個USB線就可以同時實現JTAG下載、softJTAG軟核調試及UART。所以在使用上會非常簡單。

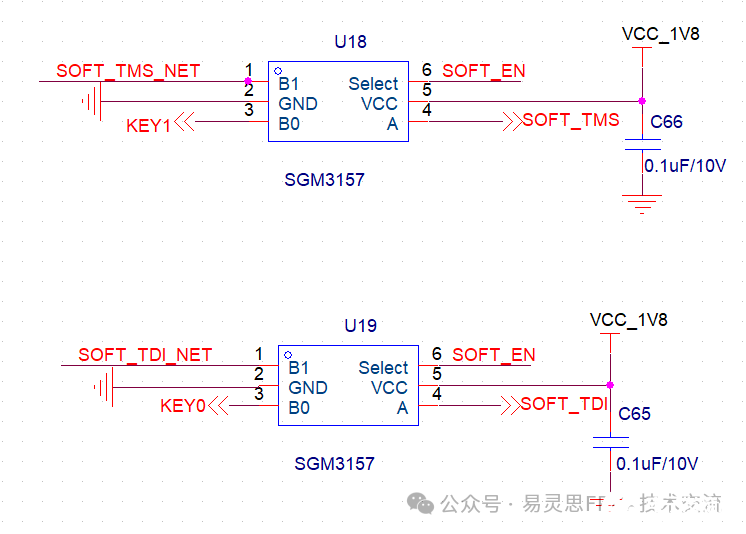

(2)用戶按鍵

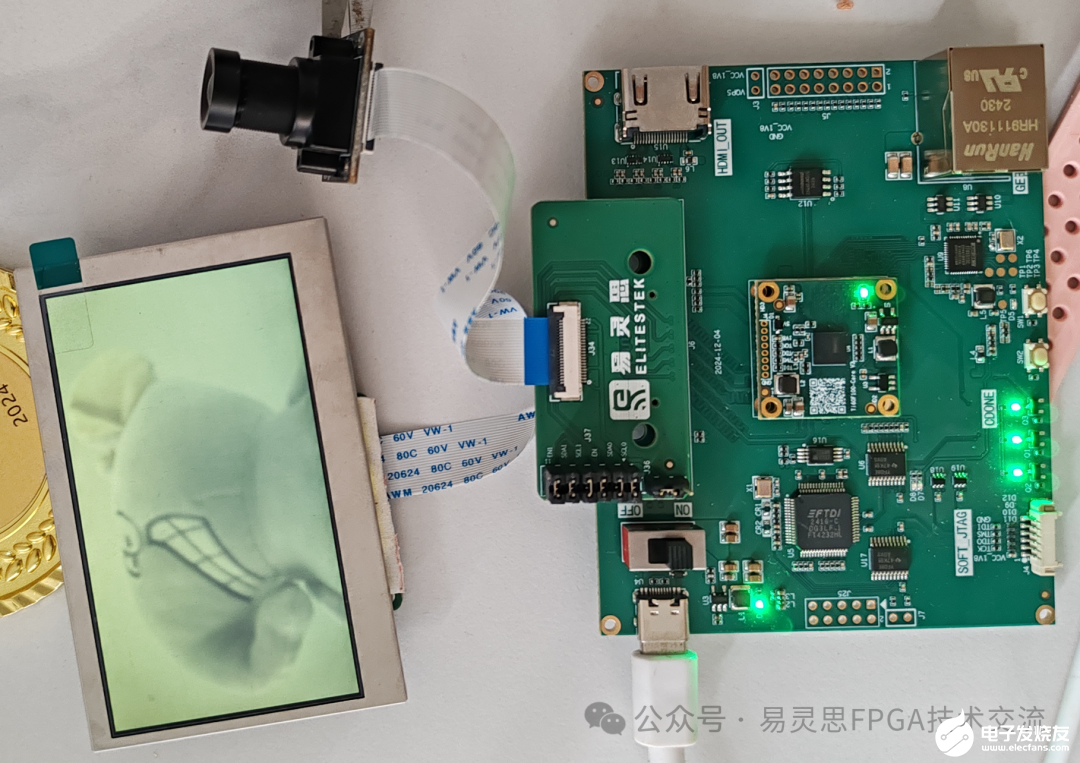

硬件圖片

| 按鍵絲印 | 按鍵編號 | FPGA Name | FPGA Num | 說明 |

| SW2 | KEY0 | GPIOR_P_19_PLLIN0 | A9 | 如果使用按鍵需要J7 Header短接,并且按鍵與SOFT JTAG共用IO |

| SW1 | KEY1 | GPIOR_N_19 | A10 |

表5

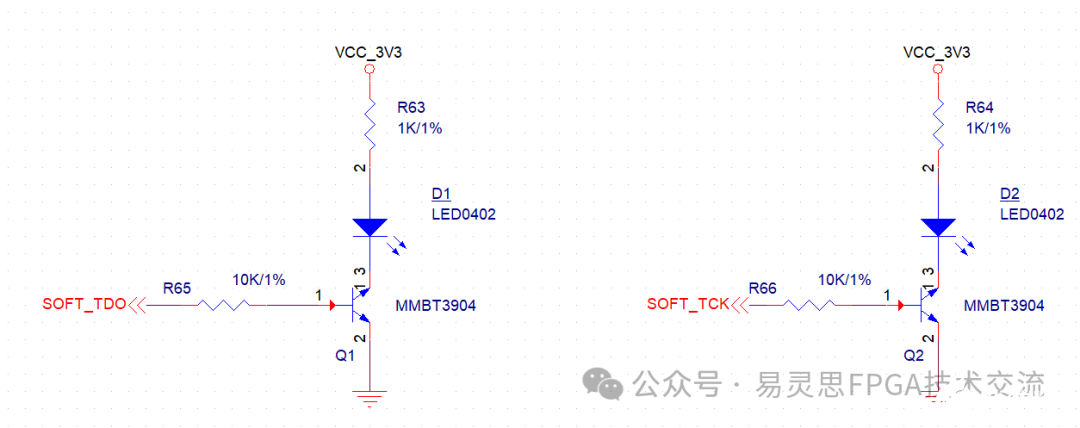

(3)用戶LED

| 按鍵編號 | FPGA Name | FPGA Num | 說明 |

| D1 | GPIOL_P_11 | E2 | 請注意LED與SOFT JTAG共用IO |

| D2 | GPIOL_N_11 | E3 |

表6

請注意:由于Ti60F100 IO有限,所以LED,按鍵是和soft JTAG共用IO

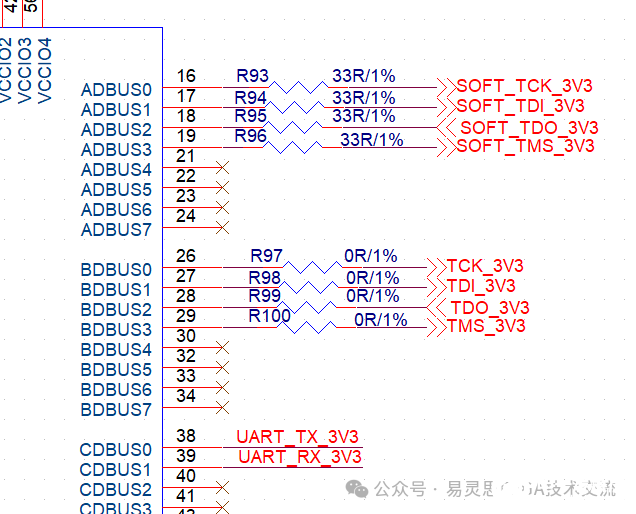

(4)板載下載器、SOFT JTAG及UART

底板配有FT4232板載程序配置方案,不需要外掛,所以連線非常簡單,穩定性也更好;另外FT4232還可以同時支持UART,所以實現一線三用的功能。

Demo板使用下載芯片的第三路作為UART

| SIGNAL | FPGA Name | FPGA Num | 說明 |

| UART_RX | GPIOR_N_10_CLK9_N | C7 | UART_RX:FPGA為input;UART_TX:FPGA為output; |

| UART_TX | GPIOR_P_10_CLK9_P | D6 |

表7

易靈思的soc與邏輯不能共用JTAG同時調試,所以需要通過IO模擬JTAG,該demo板,下載芯片可以同時實現JTAG下載及SOFT JTAG高度功能。

| SIGNAL | FPGA Name | FPGA Num | 說明 |

| SOFT_TMS | GPIOR_P_19_PLLIN0 | A9 | 對于FPGA來說,SOFT_TDO為output,其余為input。使用softJTAG需要把J7短接。 |

| SOFT_TCK | GPIOL_N_11 | E3 | |

| SOFT_TDI | GPIOR_N_19 | A10 | |

| SOFT_TDO | GPIOL_P_11 | E2 |

表8

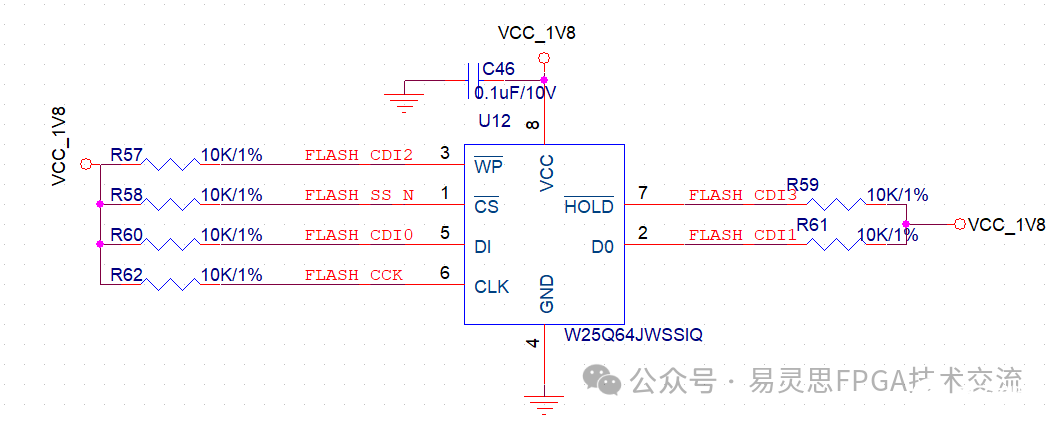

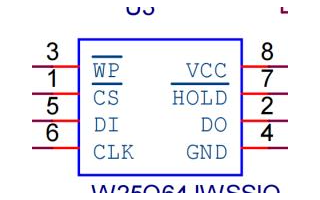

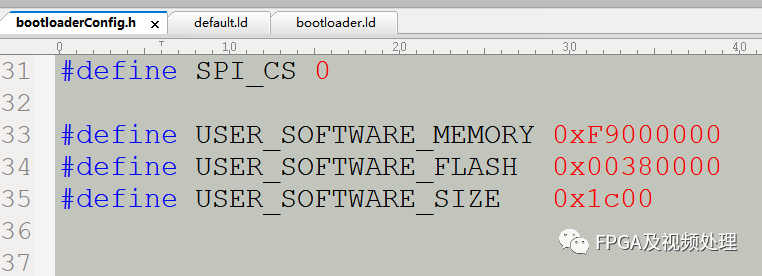

(5)擴展flash

Ti60F100內部自帶16Mb的Flash,但是很多客戶反饋片上Flash容量偏小,需要擴展。所以底板上提供一個外部GD25LQ64的flash 用于擴展使用,并支持4線。

| 按鍵編號 | FPGA Name | FPGA Num | 說明 |

| FLASH_CDI0 | GPIOL_P_03 | H2 | 注意,外部擴展flash與合封的flash是共用CCK,CDI0和CDI1. |

| FLASH_CDI1 | GPIOL_P_03 | H1 | |

| FLASH_CDI2 | GPIOL_P_05 | G4 | |

| FLASH_CDI3 | GPIOL_N_05 | G3 | |

| FLASH_SS_N | GPIOT_P_01 | A4 | |

| FLASH_CCK | GPIOL_N_01 | J2 |

表9

(6)HDMI輸出

底板J3為HDMI輸出,分辨率最高支持1080p60,方便畫面顯示。

| SIGNAL | FPGA Name | FPGA Num | 說明 |

| TX_TMDS_CLK_P | GPIOR_P_11_CLK8_P | D8 | |

| TX_TMDS_CLK_N | GPIOR_N_11_CLK8_N | D9 | |

| TX_TMDS_DATA_P2 | GPIOR_P_13 | C8 | |

| TX_TMDS_DATA_N2 | GPIOR_N_13 | B8 | |

| TX_TMDS_DATA_P1 | GPIOR_P_14 | B9 | |

| TX_TMDS_DATA_N1 | GPIOR_N_14 | B10 | |

| TX_TMDS_DATA_P0 | GPIOR_P_12 | D10 | |

| TX_TMDS_DATA_N0 | GPIOR_N_12 | C10 |

表9

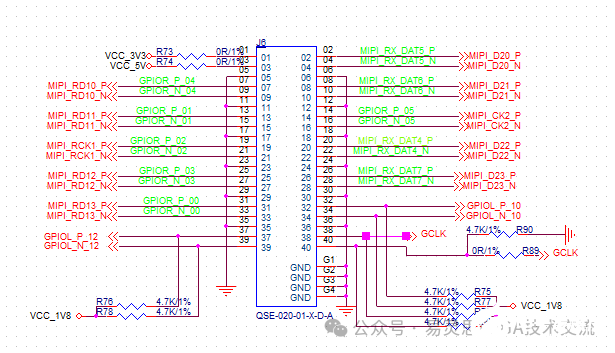

(7)MIPI擴展

在J1座子上預留了10對差分對,可以用于1組4lane的MIPI CSI/DSI接收和1組4lane CSI/DSI發送,也可以用組MIPI CSI/DSI 發送。等長為3mil

當該Bank電壓配置為1.8V時,可以用作LVDS,最大10對差分對接收或者發送。

| PIN | PIN | ||

| 1 | 3.3V | 2 | GPIOR_P_08_CLK11_P |

| 3 | 5V | 4 | GPIOR_N_08_CLK11_N |

| 5 | GND | 6 | GND |

| 7 | GPIOR_P_04 | 8 | GPIOR_P_07 |

| 9 | GPIOR_N_04 | 10 | GPIOR_N_07 |

| 11 | GND | 12 | GND |

| 13 | GPIOR_P_01 | 14 | GPIOR_P_05 |

| 15 | GPIOR_N_01 | 16 | GPIOR_N_05 |

| 17 | GND | 18 | GND |

| 19 | GPIOR_P_02 | 20 | GPIOR_P_09_CLK10_P |

| 21 | GPIOR_N_02 | 22 | GPIOR_N_09_CLK10_N |

| 23 | GND | 24 | GND |

| 25 | GPIOR_P_03 | 26 | GPIOR_P_06 |

| 27 | GPIOR_N_03 | 28 | GPIOR_N_06 |

| 29 | GND | 30 | GND |

| 31 | GPIOR_P_00_PLLIN0 | 32 | GPIOL_P_10 |

| 33 | GPIOR_N_00 | 34 | GPIOL_N_10 |

| 35 | GND | 36 | GND |

| 37 | GPIOL_P_12 | 38 | GPIOL_P_09 |

| 39 | GPIOL_N_12 | 40 | GPIOL_P_09 |

表10

MIPI分配規則,當作為發送時,可支持兩組MIPI X4發送;當作為接收時,只有紫色一組可以作為接收,因為只有GPIOR_PN_02可以作為接收時鐘。下圖是同時接有Senosr和屏的圖片。

(8)LVDS擴展

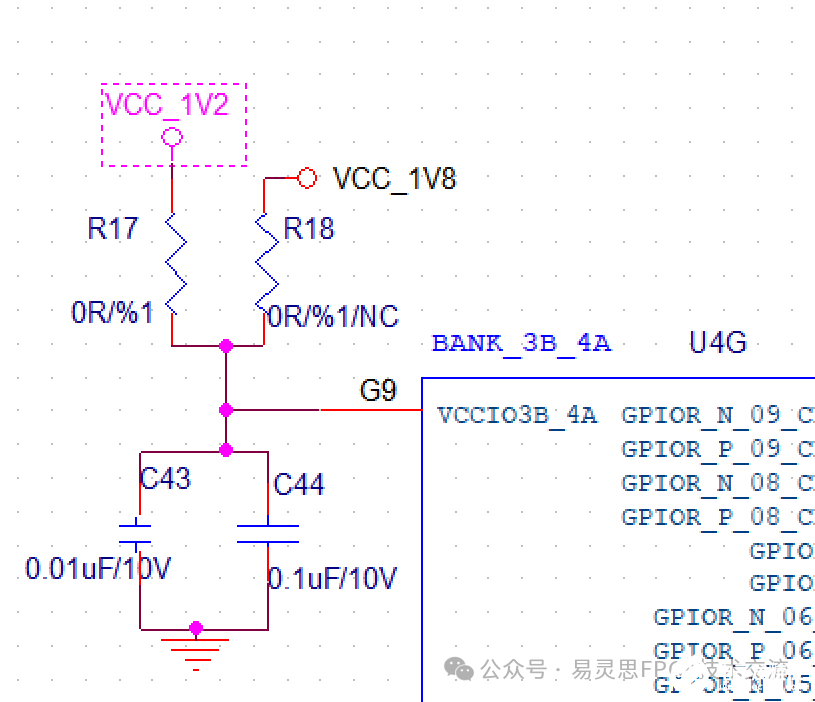

在表10中,10對帶顏色的差分做都做了等長,底板3mil,核心板3mil。其中GPIOR_PN_00可以用作LVDS時鐘接收連接于PLL。在設計中這些差分對所在的Bank默認Bank電壓是1.2V,所以如果要用作LVDS需要把該Bank的電壓修改成1.8V,也就是貼上R18,斷開R17.

請注意MIPI和LVDS是共用IO的。

(9)GE口

底板提供了三速以太網接口。采用的是裕泰的YT8531SH。

| SIGNAL | FPGA Name | FPGA Num | 說明 |

| TX_CLK | GPIOL_P_06 | G1 | |

| TXD0 | GPIOL_N_06 | F1 | |

| TXD1 | GPIOL_P_15 | C5 | |

| TXD2 | GPIOL_N_15_TEST_N | D5 | |

| TXD3 | GPIOL_N_18 | B2 | |

| TX_CTL | GPIOL_N_09_MIPI_CKN | F2 | |

| RX_CLK | GPIOL_P_08 | E4 | |

| RXD0 | GPIOL_P_17 | B4 | |

| RXD1 | GPIOL_N_07 | F5 | |

| RXD2 | GPIOL_N_08 | E5 | |

| RXD3 | GPIOL_P_18_PLLIN | B3 | |

| RX_CTL | GPIOL_N_17 | C4 | |

| MDIO | GPIOL_P_13 | B1 | |

| MDC | GPIOL_N_13 | C1 |

表11

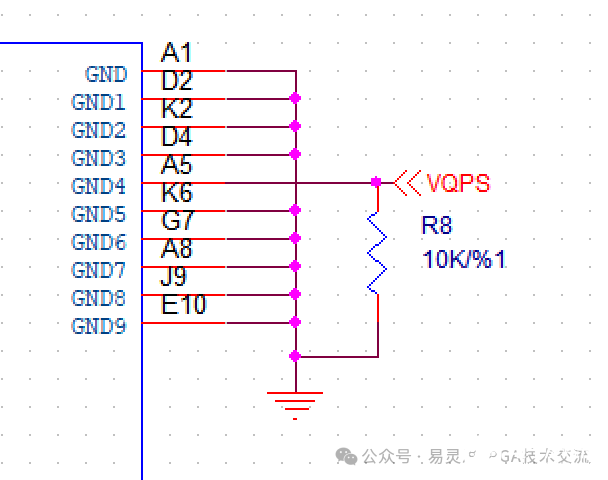

(10)加密驗證

Ti60F100-DK支持加密驗證。VQPS默認10K電阻下拉到地。如果需要驗證加密功能,短接J3座子給VQPS供電,加密燒寫完成之后再斷開J3;如果不需要驗證直接把J3斷開即可。

-

FPGA

+關注

關注

1630文章

21786瀏覽量

605088 -

評估板

+關注

關注

1文章

559瀏覽量

29390 -

易靈思

+關注

關注

5文章

48瀏覽量

4903

發布評論請先 登錄

相關推薦

Ti60F100 內外flash操作方案

三星S5PV210之芯靈思Sin210與TI Beaglebone Black之對比

請問6678評估板上的60針接口是TI標準接口嗎,XDS560 v2 System Trace可否用于評估板的仿真調試?

PWD13F60 STMicroelectronics PWD13F60柵極驅動器

PWD5F60TR STMicroelectronics PWD5F60高密度功率驅動器

Ti60F100用片內flash啟動RISCV程序不能成功的解決辦法

PCA7412F-100/PCA7412L-100/PCA7412G-100/PCA7413F-80 用戶手冊(PROM Adapter for M16C/60 Series)

采用易靈思Ti60F100的Ti60F100I3評估板詳解

采用易靈思Ti60F100的Ti60F100I3評估板詳解

評論