文章來源:老虎說芯

原文作者:老虎說芯

本文簡單介紹了多芯片封裝的概念、技術、工藝以及未來發展趨勢。

多芯片封裝技術(Multi-Chip Packaging, MCP)是現代集成電路(IC)領域的一項關鍵技術,用于在一個封裝中集成多個芯片或功能單元。這項技術通過空間的優化和功能的協同,大幅提升了器件的性能、帶寬及能源效率,是未來高性能計算、人工智能、通信等領域的核心基礎。

1. 多芯片封裝的基本概念

1.1 定義與核心思想

多芯片封裝是一種將多個芯片(邏輯芯片、存儲芯片、射頻芯片等)集成到一個封裝體中的技術。它包括2.5D封裝(通過硅中介層連接)和3D封裝(垂直堆疊芯片),實現更高的集成度和性能。

比喻:可以將多芯片封裝理解為搭建“微型城市”:每個芯片是一個功能區域,通過“道路”(互連結構)連接,實現高效協作。

1.2 優勢

提升性能:縮短芯片間信號傳輸路徑,降低延遲和功耗。

節省空間:更小的封裝體積適用于移動設備和高密度服務器。

模塊化設計:便于不同功能芯片的靈活組合,降低設計復雜性。

2. 關鍵技術要點

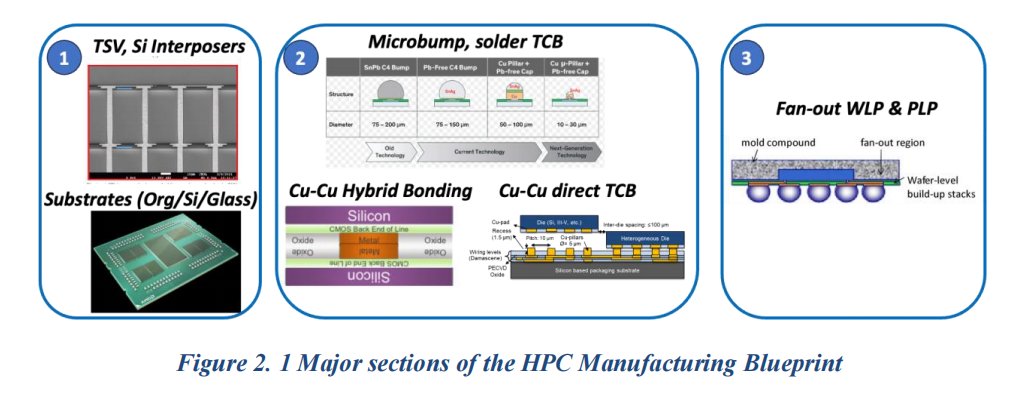

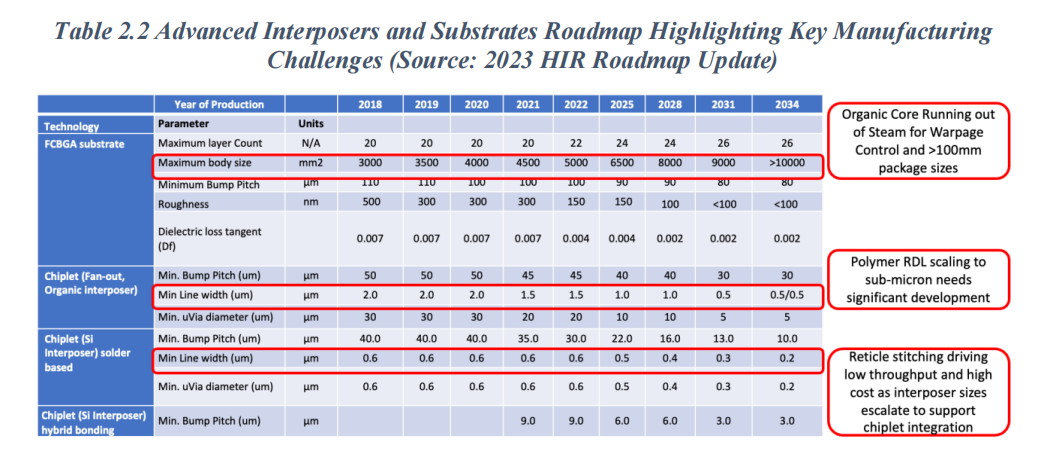

2.1 先進基板

先進基板是多芯片封裝的物理載體,其性能直接決定信號傳輸的速度和功耗。當前技術要求先進基板的線寬/線距在1/1μm甚至更小,以滿足高帶寬和低功耗的需求。

當前缺口:美國產業鏈在先進基板制造方面落后于亞洲,特別是在精細間距重新布線層(RDL)技術上。

未來目標:HIR計劃到2030年實現0.5/0.5μm線寬/線距。

2.2 互連技術

芯片間互連是多芯片封裝的核心挑戰。包括以下兩種主流技術:

硅中介層(Interposer):提供高密度互連,支持更大的帶寬,但制造成本高。

有機基板:成本較低,但信號完整性和散熱性能略差。

2.3 熱管理

封裝功率密度的增加對熱管理提出了更高要求。

挑戰:200-400W的熱設計功耗(TDP)需要有效散熱方案。

解決方案:引入先進的封裝內熱導材料、集成熱界面材料(TIM)和液冷等技術。

2.4 電源傳輸

高帶寬需求使電源傳輸成為一大瓶頸。

問題:傳統分立電源組件已無法滿足封裝內高功率密度要求。

解決方法:基于封裝內電壓調節器(IVR)的技術,利用電感和開關電容實現高效電源傳輸。

3. 工藝挑戰

3.1 制造工藝

多芯片封裝的實現依賴高精度制造工藝,主要包括:

精細間距RDL制造:當前投資主要集中在亞洲,需要突破以實現更高的線寬/線距。

面板級封裝(PLP):針對大尺寸封裝提供更高性價比的解決方案。

3.2 材料升級

多芯片封裝需要新型材料的支持:

中介層替代材料:如高密度陶瓷基板,具備更高熱導率和機械強度。

封裝材料:需要支持更高的熱導率和更低的電阻。

3.3 可靠性

堆疊芯片和細間距互連帶來的機械應力、熱膨脹失配需要解決封裝長期可靠性問題。

4. 未來發展趨勢

4.1 小芯片(Chiplet)和異構集成

小芯片技術將不同工藝節點、功能模塊芯片進行集成。相比傳統的單片設計,小芯片提供了更高的靈活性和性能。

HBM3應用:如高帶寬存儲(HBM3)需要每通道4-6Gbps的數據速率,封裝中的I/O數量快速增長,每個硅節點的HBM數量將增加1.4倍。

4.2 2.5D與3D封裝的擴展

2.5D封裝:擴展EMIB技術,提高帶寬密度并降低成本。

3D封裝:通過垂直堆疊實現更高的性能密度,但對熱管理和制造精度提出更高要求。

4.3 高密度基板技術

未來目標是將有機基板和面板級基板的性能提高到1/1μm以下,從而實現更低的電阻和更高的傳輸速度。

4.4 電源集成

封裝內電源集成技術將進一步優化,通過局部電壓調節器和高效電源傳輸組件,支持高功率應用。

5. 總結與展望

多芯片封裝技術已經成為集成電路產業的關鍵方向,其優勢在于提升性能、節省空間和支持多樣化應用。然而,該技術仍面臨基板制造、熱管理、電源傳輸等多方面的挑戰,需要從材料、工藝、設計等多個維度進行持續創新。

-

集成電路

+關注

關注

5389文章

11572瀏覽量

362223 -

制造工藝

+關注

關注

2文章

179瀏覽量

19771 -

多芯片封裝

+關注

關注

0文章

5瀏覽量

6022

原文標題:多芯片封裝(MCP)的全面解析

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【視頻】智能家居系統關鍵技術分析與應用

軟件無線電的功能結構、關鍵技術和難點以及應用和發展前景討論

GPS芯片的關鍵技術是什么

嵌入式實時系統的關鍵技術是什么?

RAM技術的基本概念

智能天線的基本概念

歸納碳化硅功率器件封裝的關鍵技術

視覺導航關鍵技術及應用

ptn技術要素及關鍵技術

電磁技術與電場的基本概念

多芯片封裝的基本概念和關鍵技術

多芯片封裝的基本概念和關鍵技術

評論