如今,由于對大電流和高功率應用的需求不斷增加,單一的MOSFET已經(jīng)無法滿足整個系統(tǒng)的電流要求。在這種情況下,需要多個MOSFET并聯(lián)工作,以提供更高的電流和功率,這有助于減少導通損耗,降低工作溫度,從而提高系統(tǒng)的可靠性。然而,當兩個或更多MOSFET并聯(lián)時,應考慮電流的一致性,以便在瞬態(tài)和穩(wěn)態(tài)條件下平衡通過每個MOSFET的電流。

在本篇應用文章中,主要集中討論了導致電流不平衡的動態(tài)參數(shù),如閾值電壓(Vth)和輸入電容(Ciss)等,進一步討論了驅(qū)動回路和功率回路寄生電感的影響,并提出了優(yōu)化的PCB布局供設計參考。

*本篇應用文章主題為“Paralleling and Driving Power MOSFETs in High-Power Applications”,是由AOS AE團隊成員(Alvin Liu, PhoebusChang, Peter Huang, Shaowei Cui, Bugao Wang, Chengyuan He)聯(lián)袂撰寫,以下是原文節(jié)選翻譯。

01、閾值電壓不匹配 電流不平衡

閾值電壓(Vth)的變化在許多MOSFET產(chǎn)品中是常見的,尤其是在不同的生產(chǎn)批次中。本實驗選取了具有不同閾值電壓(Vth),同時保持其他參數(shù)(如Rg、Ciss和Gfs)不變的器件。為了便于研究MOSFET并聯(lián)時的電流均流特性,進行了簡化處理,研究了2個、3個和5個MOSFET并聯(lián)時的均流特性。實驗器件(DUT)為AOTL66912,采用典型的TOLL封裝,具有100V的BVDSS,RDS(on)為1.4mΩ。

02、多管并聯(lián)應用 參數(shù)設計影響均流效果

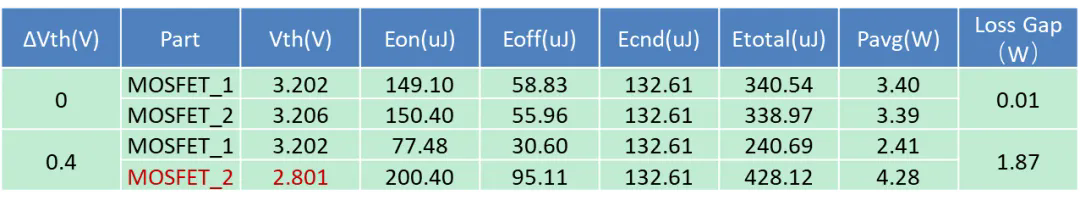

當并聯(lián)的兩個MOSFETs具有相同的參數(shù),如內(nèi)在閾值電壓(Vth)、Rg和Ciss時,它們的開通能量(Eon)和關斷能量(Eoff)非常相似,功率損耗的差距僅為0.01W。當2號MOSFET被Vth較低的器件替換時,其Eon和Eoff顯著增大,功率損耗比Vth較高的1號MOSFET器件高出1.87W,如表1所示。

圖▲ Two MOSFETs parallel Test Result (Ton=250ns, Toff=100ns, Fs=10KHz)

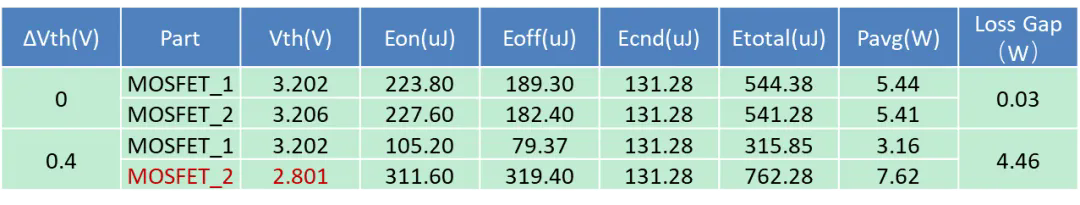

MOSFET開關速度是影響電流平衡的另一個因素。在測試中,采用了更長的開通時間(Ton)和關斷時間(Toff),以及較高的外部驅(qū)動電阻Rg,此時不同Vth的器件之間的功率損耗差距會變大,如表2所示。當關斷時間為100ns時,Vth較低的2號MOSFET與1號MOSFET之間的總功率損耗差(包括開關損耗和導通損耗)約為1.87W;而當關斷時間為300ns時,功率損耗差距將增大到4.46W。其原因在于,當關斷時間更長時,兩個MOSFET的Vgs達到Vth的間隔時間變長,從而使得功率損耗差距也變大。

根據(jù)測試結果,具有相同Vth值的MOSFET并聯(lián)時,MOSFET外部驅(qū)動速度的快慢是實現(xiàn)更好電流平衡性能的關鍵因素。

圖 ▲ Two MOSFETs Parallel Test Result (Ton=380ns, Toff=300ns, Fs=10KHz)

03、MOSFET柵極驅(qū)動不匹配 電流不平衡

驅(qū)動參數(shù)的一致性,包括驅(qū)動回路的電阻、電容和電感,是影響電流平衡特性的另一個因素。

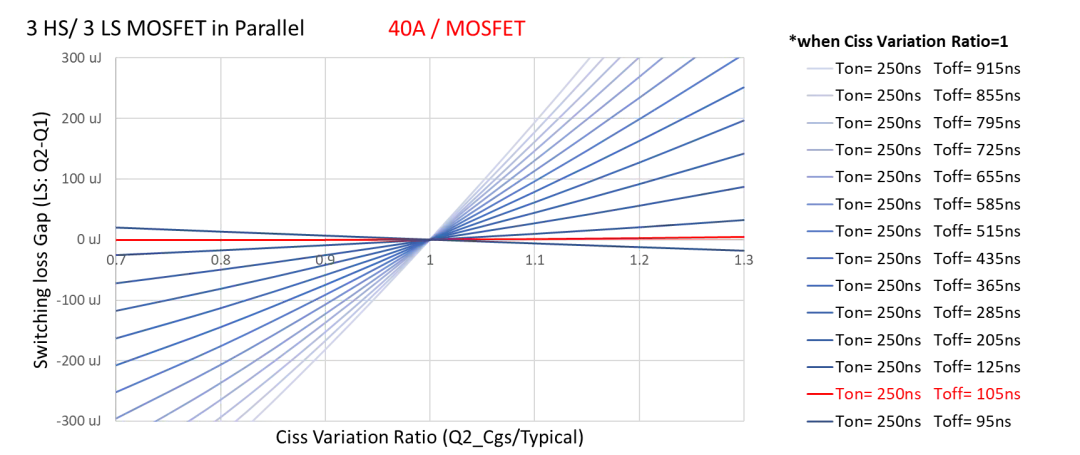

當兩個MOSFET并聯(lián)且其驅(qū)動回路的電容不同,具有較大輸入電容(Ciss)的MOSFET的開通時刻將比另一個MOSFET延遲,這會導致具有較大Ciss的MOSFET的開通能量(Eon)較小。然而,關斷過程則不同,較大的Ciss會導致關斷時刻延遲,從而導致較大的關斷能量(Eoff)。

通常情況下,當兩個MOSFET并聯(lián)時,具有較大Ciss的MOSFET的Eon較小,但Eoff較大。

MOSFET的輸入電容或驅(qū)動回路對Eon和Eoff具有相反的影響。如果一個MOSFET的Ciss高于其他并聯(lián)MOSFET的Ciss,其Eon將減小,而Eoff則會增大。實際上,在某些條件下,Eon和Eoff的總和可以進行權衡,進而達到最小值。因此,不同Ciss對電流平衡的影響可以忽略不計,如圖1所示。在實際應用中,建議Toff應約為Ton的40%以實現(xiàn)最佳系統(tǒng)設計。

Ciss Variation Ratio vs Switching Loss Gap | 1 圖 ▲

04、驅(qū)動參數(shù)優(yōu)化與電流共享 外部Rg選擇對電流平衡的影響

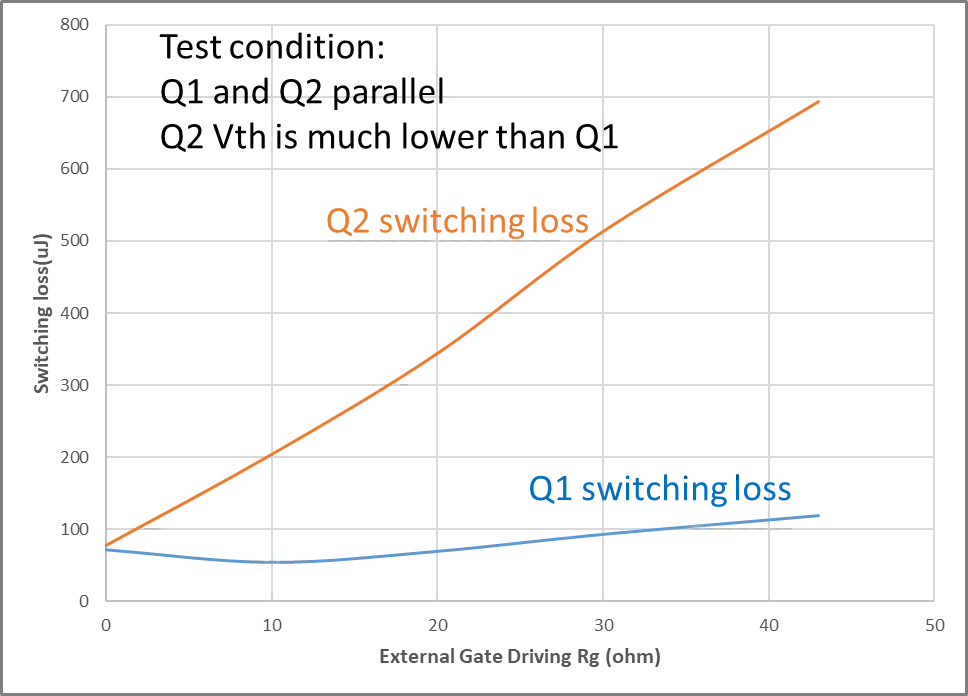

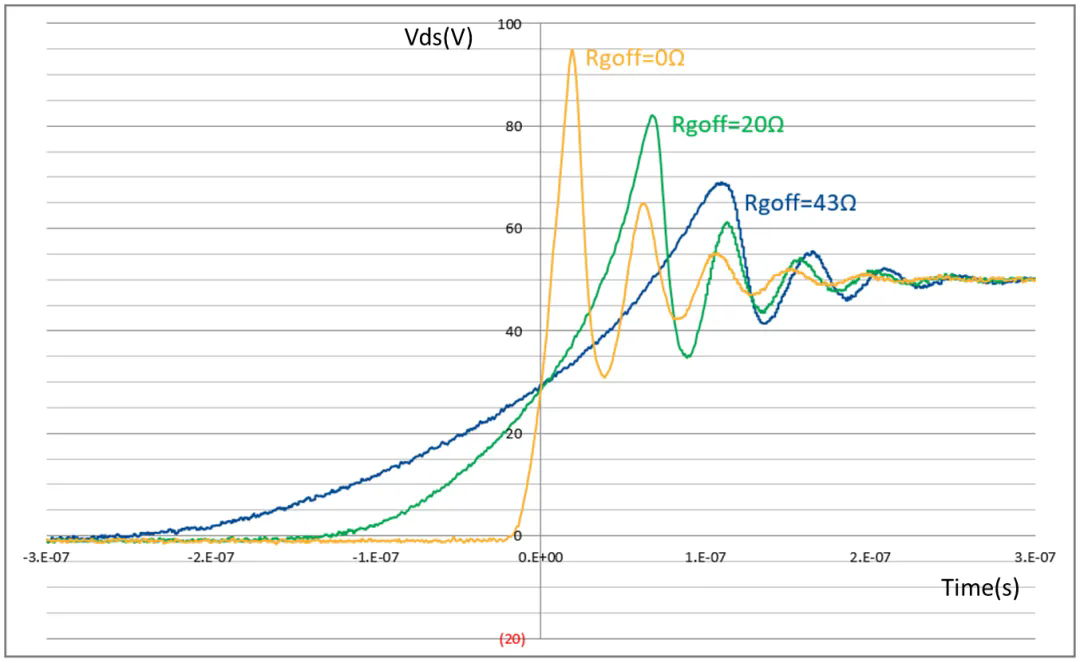

柵極驅(qū)動回路的一致性將極大地影響電流平衡性能。驅(qū)動回路應保持一致,以滿足電流平衡的要求。其次,為了滿足系統(tǒng)效率的要求,開關速度應盡可能快。更快的開關速度將導致并聯(lián)MOSFET之間的開關損耗差距變小,如圖2所示。然而,快速的開關速度可能會引發(fā)過大的電壓尖峰,如圖3所示,因此電流平衡特性和電壓尖峰之間存在權衡,在系統(tǒng)設計中應找到平衡點。

Differences in Total Switch Losses Under Different Rg | 2 圖 ▲

Vds Spike Voltage vs Rgoff | 3 圖 ▲

05、結論

在高電流并聯(lián)應用中,影響電流一致性的因素主要來自兩個方面:一是MOSFET參數(shù)的一致性,如Vth和Ciss;二是應用中驅(qū)動回路設計和功率回路設計的不一致性。對于MOSFET制造商來說,控制生產(chǎn)工藝以獲得參數(shù)一致性至關重要。從應用角度來看,合適的驅(qū)動設計、一致的驅(qū)動回路和功率回路電感設計同樣是確保電流一致性的關鍵因素。

唯樣是國內(nèi)知名的電子元器件線上授權代理商。致力于服務終端研發(fā)、高校科研、工程師等廣大客戶高品質(zhì)、少量多樣、快速交付的元器件采購需求。

唯樣擁有3.5萬㎡倉儲、超13萬種現(xiàn)貨庫存、2500w+產(chǎn)品型號數(shù)據(jù),已獲得YAGEO、TDK、TE Connectivity、nexperia、ROHM、Panasonic、MPS等全球數(shù)十家一線品牌代理授權。

審核編輯 黃宇

-

MOSFET

+關注

關注

147文章

7195瀏覽量

213598 -

高功率

+關注

關注

1文章

192瀏覽量

18424 -

AOS

+關注

關注

0文章

23瀏覽量

314

發(fā)布評論請先 登錄

相關推薦

是否可以將6片TLV5638的REF腳并聯(lián)在一起接到基準電壓?

MOSFET并聯(lián)在高功率設計中的應用

串聯(lián)和并聯(lián)在家居布線中的應用

壓敏電阻是串聯(lián)還是并聯(lián)在電路中

兩片THS3091并聯(lián)在低頻波形完好,到高頻波形有失真,為什么?

熔斷器是串聯(lián)還是并聯(lián)在電路中

成功并聯(lián)功率MOSFET的技巧

并聯(lián)電路總功率與各部分功率的關系

大功率IGBT和SiC MOSFET的并聯(lián)設計方案

MOSFET并聯(lián)(并聯(lián)功率MOSFET之間的寄生振蕩)

功率 MOSFET、其電氣特性定義

AOS推出新款100V MOSFET AONA66916

AOS推出創(chuàng)新型雙面散熱 DFN 5x6 封裝

AOS MOSFET并聯(lián)在高功率設計中的應用

AOS MOSFET并聯(lián)在高功率設計中的應用

評論