以下文章來源于LPIoT,作者水鳥LPIoT

Pcie數據鏈路層

PCIe的數據鏈路層在事務層和物理層之間,用來負責鏈路管理,其主要功能是保證來自事務層的TLP在PCIe鏈路中的正確傳輸,為此數據鏈路層定義了一系列的DLLP報文,數據鏈路層使用了容錯和重傳機制保證數據傳輸的完整性和一致性(TLP ACK/NAK),此外數據鏈路層還需要對PCIe鏈路進行管理(電源管理)和監控(流量控制)。

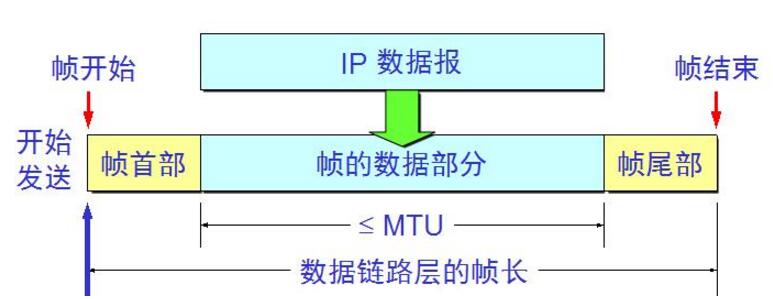

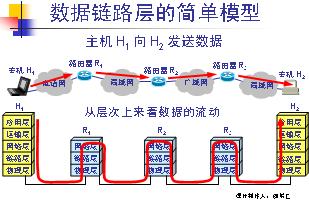

與事務層不同的是,數據鏈路層主要處理端到端(同一條PCIe物理鏈路相鄰兩端設備的發送端和接收端)的數據傳輸;而事務層是源設備和目標設備之間的數據傳輸(源設備與目標設備之間傳輸距離更長,可能經過多個Switch并有多條PCIe物理鏈路)。此處類似于網絡通訊的概念,鏈路層通訊在直接物理相連的設備端口進行,網絡層通訊可以跨過多個設備進行。

數據鏈路層結構

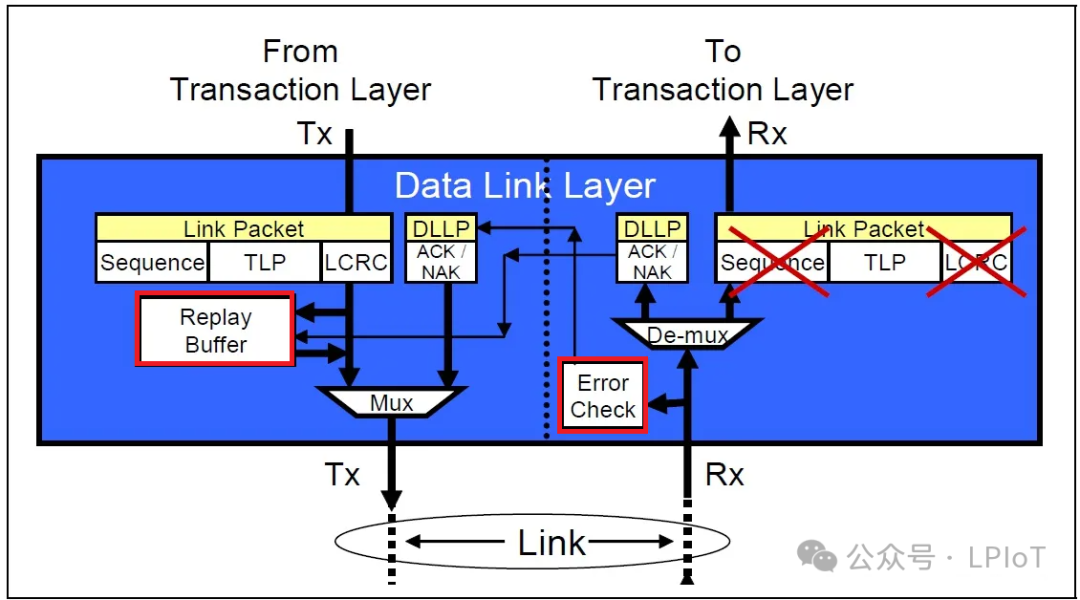

數據鏈路層使用ACK/NAK協議發送和接收TLP(事務層報文),由發送部件和接收部件組成(每個PCIe設備的數據鏈路層包含了這兩部分,而兩個PCIe設備間的通信是發送部件和接收部件成對實現的),如下圖所示;

發送部件由1.Replay Buffer、2.ACK/NAK DLLP接收邏輯和3.TLP接收邏輯組成;

接收部件由1.“Error Check”邏輯、2.ACK/NAK DLLP發送邏輯和3.TLP發送邏輯組成。

PCIe總線數據鏈路層使用Replay Buffer和Error Check部件共通保證數據傳輸的可靠性和完整性;來自事務層的TLP先暫存在Replay Buffer中,然后發送到目標設備;源設備的數據鏈路層根據來自目標設備的ACK/NAK DLLP報文來決定是重發這些TLP,還是清除存放在Replay Buffer中的TLP。

1.Replay Buffer的大小決定過了事務層可以暫存在數據鏈路層的報文數量;

2.PCIe設備使用Error Check檢查接收到的TLP,并決定如何向對端設備進行報文回應;

數據鏈路層狀態

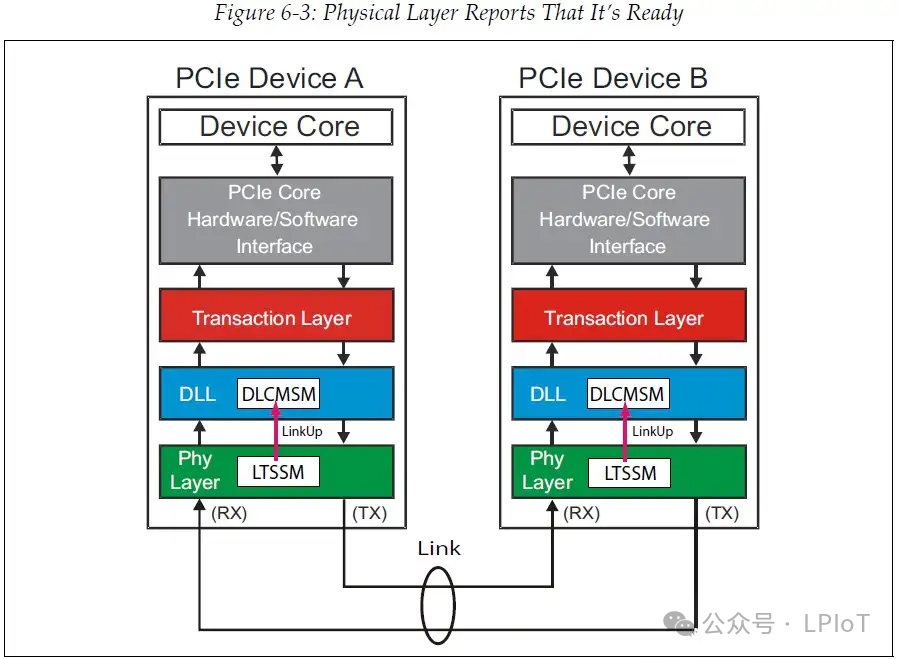

數據鏈路層需要通過物理層來監控PCIe鏈路狀態,并維護數據鏈路層的“控制與管理狀態機”(Data Link Control and Management State Machine,DLCMSM),可以從物理層獲得與當前PCIe鏈路相關的狀態,如下圖所示:

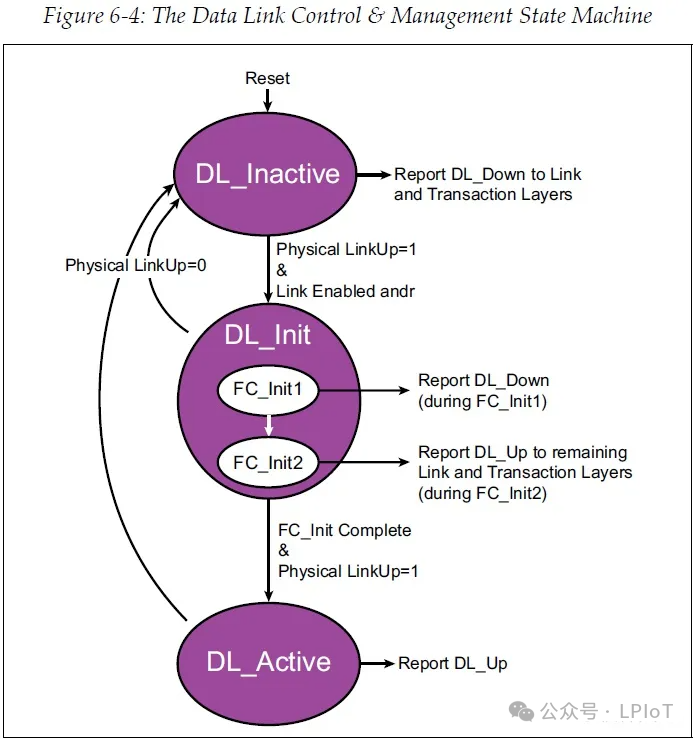

DLCMSM主要包含三個狀態:DL_Inactive、DL_Iinit、DL_Active

DL_Inactive狀態:物理層通知數據鏈路層當前PCIe鏈路狀態不可用,沒有檢測到PCIe鏈路的對端連接了PCIe設備;PCIe設備從復位狀態進入DL_Inactive狀態時,進行如下操作:

(1)對PCIe數據鏈路層進行徹底復位:將與PCIe鏈路相關的寄存器置為復位值,并丟棄在Replay Buffer中保存的所有報文;

(2)數據鏈路層向事務層提交DL_Down狀態信息;

(3)丟棄來自數據鏈路層和物理層的所有TLP,不再接收對端設備發送的DLLP;

(4)如果PCIe鏈路對端有PCIe設備相連,則物理層的LinkUp狀態位為1,且事務層并未禁止當前PCIe鏈路時,數據鏈路層將從DL_Inactive狀態遷移到DL_Init狀態。

(5)如果PCIe鏈路對端不存在PCIe設備,則物理層的LinkUp狀態位為0,此時數據鏈路層一直處于DL_Inactive狀態。

2.DL_Iinit狀態:物理層通知數據鏈路層當前PCIe鏈路可用(LinkUp = 1),且物理層正處理鏈路初始化狀態,此時數據鏈路層不能接收或發送TLP和DLLP;

3.DL_Active狀態:當前PCIe鏈路處于正常工作模式,物理層已完成PCIe鏈路訓練(LTSSM);此時數據鏈路層可以從事務層和物理層正常接收和發送TLP,并處理DLLP。在多數情況下數據鏈路層從DL_Active狀態遷移到DL_Init狀態,意味著處理器系統出現了異常,系統軟件需要處理這些異常;但如下情況的狀態遷移不會引發異常。

DLCMSM除了從物理層獲得當前PCIe鏈路狀態外,還可以使用狀態位向事務層報告數據鏈路層所處的狀態;如上圖所示,當數據鏈路層收到物理層的狀態信息后,DLCMSM狀態機將進行狀態轉換,并向事務層通知PCIe鏈路的狀態。

1.DL_Down:數據鏈路層處于該狀態時,表示PCIe鏈路暫時沒有檢測到對端連接設備(并非對端不存在物理設備);當數據鏈路層處于DL_Inactive時,該狀態位有效;

2.DL_Up:數據鏈路層處于該狀態時,表示PCIe鏈路的對端連接了設備;當數據鏈路層處于DL_Acive狀態時,該狀態位有效。

事務層對DL_Down/Up狀態的處理

當事務層收到數據鏈路層的DL_Down狀態信息時,則說明出現了如下狀況:

1.PCIe鏈路的對端沒有連接設備;

2.PCIe鏈路丟失了對端設備的連接;

3.數據鏈路層和物理層出現了某種錯誤,PCIe鏈路不能正常工作;

4.系統軟件禁用PCIe鏈路。

事務層受到DL_Down狀態信息后:

1.將不再從數據鏈路層中接收TLP,除了已經使用ACK/NAK報文確認過的TLP;

2.RC或Switch的下游端口將復位與鏈路相關的內部邏輯和狀態;

3.Switch和Bridge的上游端口將復位相關的內部邏輯和狀態,并丟棄正在處理的TLP;

——此時Switch和PCIe橋使用Hot Reset方式復位所有下游端口。

以上是《PCIE數據鏈路層整體架構》,敬請關注后續內容

-

PCIe

+關注

關注

15文章

1248瀏覽量

82954 -

數據鏈路層

+關注

關注

0文章

58瀏覽量

12017 -

狀態機

+關注

關注

2文章

492瀏覽量

27613 -

網絡通訊

+關注

關注

0文章

75瀏覽量

11284

原文標題:PCIE數據鏈路層整體架構

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

TLP的數據鏈路層組成與操作

數據鏈路層的作用

什么是OSI模型數據鏈路層

數據鏈路層到底是什么_數據鏈路層工作原理是怎樣的

數據鏈路層常用成紙法有哪些_數據鏈路層的作用

數據鏈路層和傳輸層的區別是什么

一文看懂數據鏈路層和網絡層的區別

數據鏈路層的任務

PCIe鏈路層里的ACK/NAK介紹

PCIE數據鏈路層架構解析

PCIE數據鏈路層架構解析

評論