與亞微米工藝類似,雙阱工藝是指形成NW和PW的工藝,NMOS 是制造在PW里的,PMOS是制造在NW里的。它的目的是形成PN 結(jié)隔離,使器件之間形成電性隔離,優(yōu)化晶體管的電學(xué)特性。

1)清洗。利用酸槽清洗晶圓,得到清潔的表面。

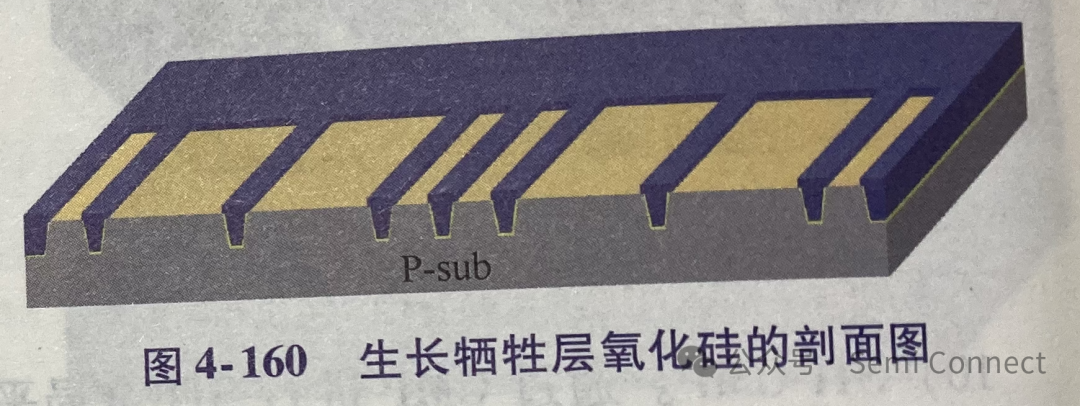

2) 生長(zhǎng)犧牲層氧化硅。利用爐管熱氧化生長(zhǎng)一層二氧化硅薄膜,它是干氧氧化法。利用高純度的氧氣在900°C左右的溫度下使硅氧化,形成厚度約200~300A的二氧化硅。犧牲層氧化硅可以防止離子注入隧道效應(yīng),隔離光刻膠與硅襯底,防止光刻膠接觸污染硅襯底,也可以捕獲硅表面的缺陷。同時(shí)為了消除Si3N4對(duì)有源區(qū)表面的影響,改善表面狀態(tài),生長(zhǎng)犧牲層氧化硅是必需的。如圖4-160所示,是生長(zhǎng)犧牲層氧化物的剖面圖。

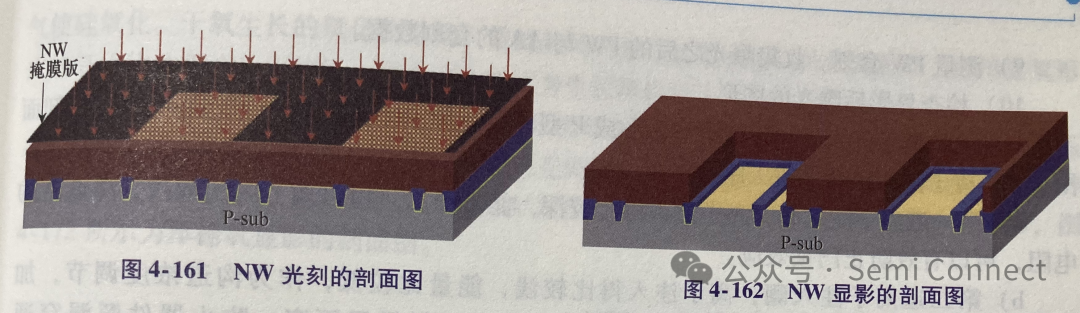

3)NW光刻處理。通過微影技術(shù)將 NW 掩膜版上的圖形轉(zhuǎn)移到晶圓上,形成NW的光刻膠圖案,非NW 區(qū)域保留光刻膠。AA作為NW光刻曝光對(duì)準(zhǔn)。如圖4-5所示,是電路的版圖,工藝的剖面圖是沿AA’方向。圖4-161 所示為 NW光刻的剖面圖。圖4-162 所示為NW顯影的剖面圖。

4)測(cè)量NW套刻,收集曝光之后的NW與 AA的套刻數(shù)據(jù)。

5)檢查顯影后曝光的圖形。

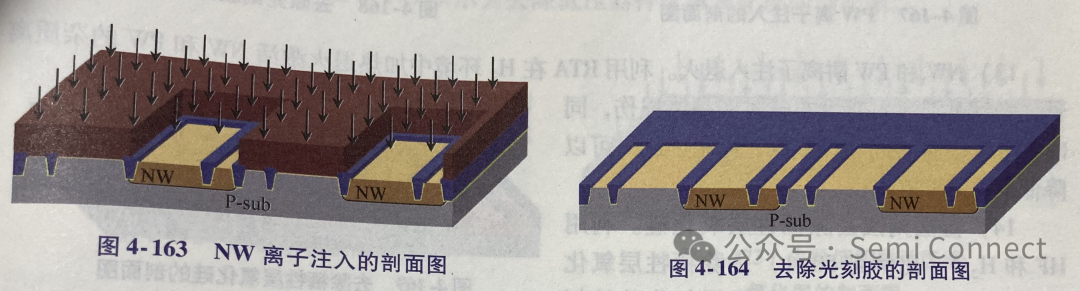

6)NW離子注入。利用離子注入形成n型的阱。圖4-163所示NW離子注入的剖面圖。NW 離子注入包括三道工序:

a)第一道離子注入磷,離子注入得比較深,能量很高,用以調(diào)節(jié)阱的濃度,降低阱的電阻,可以有效防止閂鎖效應(yīng)。

b)第二道離子注入磷,離子注入得比較淺,能量比較低,作為溝道濃度調(diào)節(jié),加大LDD 以下局部阱的濃度,使器件工作時(shí)該位置的耗盡層更窄,防止器件源漏穿通漏電。

c)第三道離子注入砷,離子注入表面,能量很低,調(diào)節(jié)PMOS閾值電壓Vt。

7)去光刻膠。利用干法刻蝕和濕法刻蝕去除光刻膠。圖4-164 所示為去除光刻膠的剖面圖。

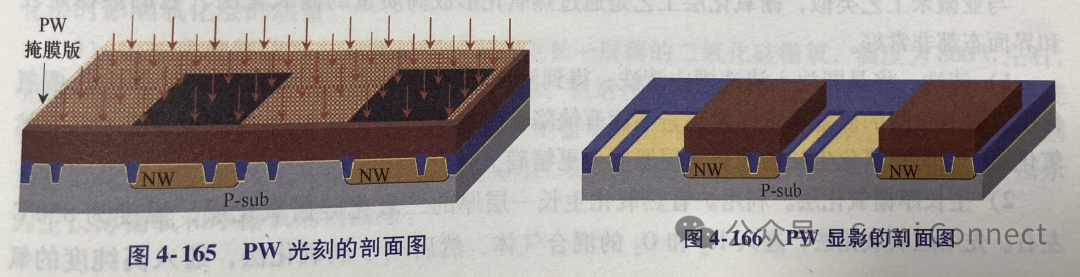

8)PW光刻處理。與NW光刻處理類似,通過微影技術(shù)將PW掩膜版上的圖形轉(zhuǎn)移到晶圓上,形成PW的光刻膠圖案,非PW區(qū)域保留光刻膠。AA作為PW光刻曝光對(duì)準(zhǔn)。圖4-5所示為電路的版圖,工藝的剖面圖是沿 AA'方向,圖4-165所示為PW光刻的剖面圖,圖4-166所示力PW 顯影的剖面圖。

9)測(cè)量PW套刻。收集曝光之后的PW與 AA的套刻數(shù)據(jù)。

10)檢查顯影后曝光的圖形。

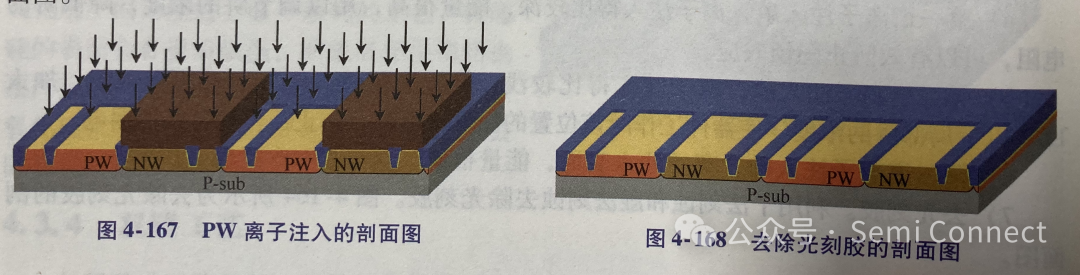

11)PW離子注入。利用離子注入形成P型的阱。圖4-167所示為PW 離子注入的剖面圖。PW 離子注入包括三道工序:

a)第一道離子注入硼,離子注入得比較深,能量很高,用以調(diào)節(jié)阱的濃度,降低阱的電阻,可以有效防止閂鎖效應(yīng)。

b)第二道離子注入硼,離子注入得比較淺,能量比較低,作為溝道濃度調(diào)節(jié),加大LDD以下局部阱的濃度,使器件工作時(shí)該位置的耗盡層更窄,防止器件源漏穿通漏電。

c)第三道離子注入BF2,離子注入表面,能量很低,調(diào)節(jié) NMOS 閾值電壓Vt。

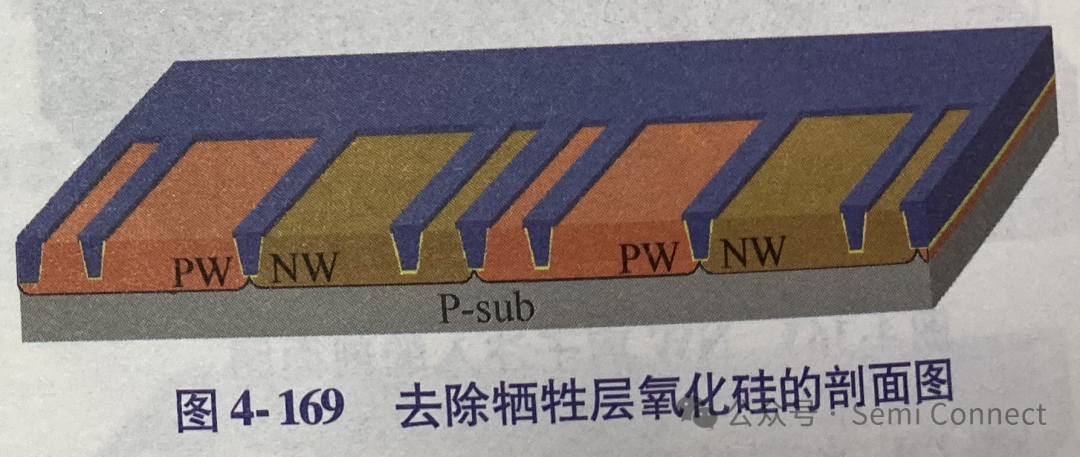

12) 去光刻膠。利用干法刻蝕和濕法刻蝕去除光刻膠。圖4-168所示去除光刻膠的剖面圖。

13)NW和PW阱離子注入退火。利用 RTA 在H2環(huán)境中加熱退火激活 NW和PW的雜質(zhì)離子,修復(fù)離子注入造成的硅襯底晶格損傷,同時(shí)會(huì)造成雜質(zhì)的進(jìn)一步擴(kuò)散,快速熱退火可以降低雜質(zhì)的擴(kuò)散。

14)濕法刻蝕去除犧牲層氧化硅。利用HIF 和H2O(比例是50:1)去除犧牲層氧化硅。圖4-169所示為去除犧牲層氧化硅的剖面圖。

-

集成電路

+關(guān)注

關(guān)注

5415文章

11858瀏覽量

366174 -

工藝

+關(guān)注

關(guān)注

4文章

656瀏覽量

29152 -

晶體管

+關(guān)注

關(guān)注

77文章

9908瀏覽量

140153

原文標(biāo)題:雙阱工藝-----《集成電路制造工藝與工程應(yīng)用》 溫德通 編著

文章出處:【微信號(hào):Semi Connect,微信公眾號(hào):Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【「大話芯片制造」閱讀體驗(yàn)】+芯片制造過程工藝面面觀

【「大話芯片制造」閱讀體驗(yàn)】+ 芯片制造過程和生產(chǎn)工藝

13um應(yīng)變補(bǔ)償多量子阱SLD臺(tái)面制作工藝的研究

機(jī)械加工廠制造工藝過程中熱處理工序位置

單片機(jī)晶圓制造工藝及設(shè)備詳解

《炬豐科技-半導(dǎo)體工藝》IC制造工藝

雙阱結(jié)構(gòu)含時(shí)量子輸運(yùn)的微擾論及輸運(yùn)方程

淺談晶圓制造工藝過程

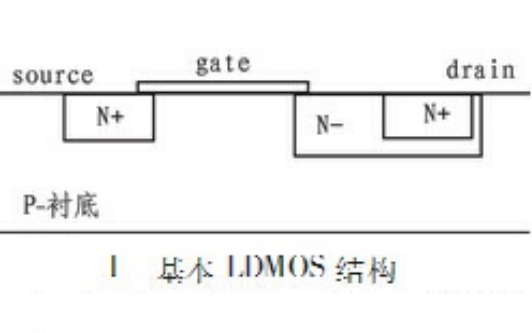

如何使用深阱工藝提高LDMOS的抗擊穿能力

模塊工藝——雙阱工藝(Twin-well or Dual-Well)

CMOS集成電路的雙阱工藝簡(jiǎn)析

半導(dǎo)體制造工藝 - 晶圓制造的過程

半導(dǎo)體芯片制造中倒摻雜阱工藝的特點(diǎn)與優(yōu)勢(shì)

評(píng)論