一、前言

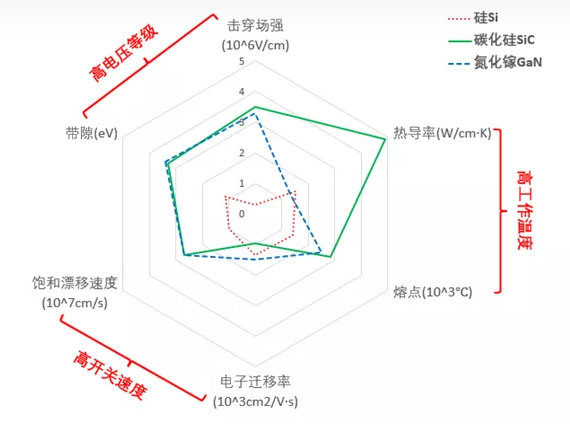

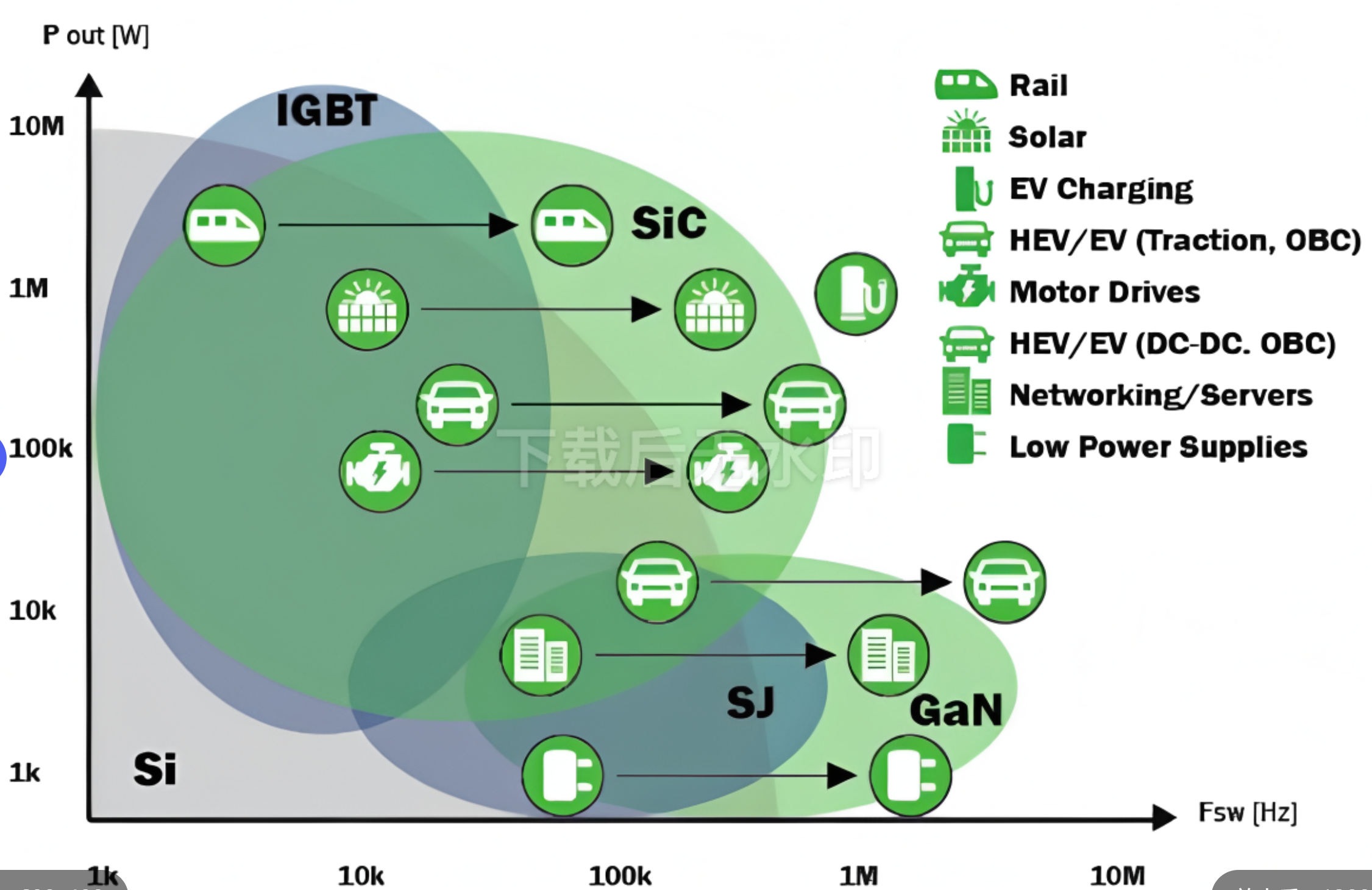

隨著電動(dòng)汽車的發(fā)展,汽車功率器件芯片也正在尋求能夠有效處理更高工作電壓和溫度的組件。此時(shí)碳化硅 MOSFET 成為牽引逆變器等電動(dòng)汽車構(gòu)建模塊的首選技術(shù)。基于碳化硅的逆變器可使高達(dá) 800V 的電氣系統(tǒng)顯著延長(zhǎng) EV 續(xù)航里程并將充電時(shí)間減半。據(jù)行業(yè)研究公司IHS Markit 的數(shù)據(jù),到 2025 年,全球高達(dá) 45% 的汽車生產(chǎn)將實(shí)現(xiàn)電氣化,每年將售出約 4600 萬(wàn)輛電動(dòng)汽車。據(jù)估計(jì),到 2030 年,這些數(shù)字將上升到 57%,每年的電動(dòng)汽車銷量約為 6200 萬(wàn)輛。功率器件正從硅基 IGBT 發(fā)展至碳化硅 MOSFET 時(shí)代。碳化硅的材料特性對(duì)比硅有了顯著的提升:碳化硅材料的臨界擊穿場(chǎng)強(qiáng)為硅的近10倍,體遷移率與硅接近,帶隙寬度是硅的3倍,電子飽和漂移速度是硅的2倍,熱導(dǎo)率也為硅的3倍。碳化硅器件和相同電壓檔硅器件相比,厚度約為硅器件的1/10,理論上通態(tài)壓降可以大大降低,在開關(guān)速率和開關(guān)損耗上優(yōu)勢(shì)則更加明顯。

△ 圖1SiC、GaN與Si材料特性比較

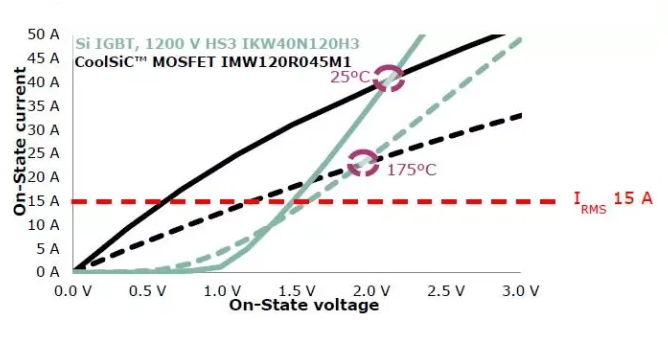

目前為止,碳化硅 MOSFET 在通態(tài)壓降上并未對(duì)硅基 IGBT 表現(xiàn)出預(yù)期的優(yōu)勢(shì)。碳化硅MOSFET 在襯底及外延層材料遷移率、SiC/SiO2界面表面遷移率方面的表現(xiàn)還有足夠的提升空間。圖2中顯示了碳化硅 Cool MOS與硅基 IGBT 導(dǎo)通損耗的對(duì)比。

△ 圖2 SiC MOSFET與SiIGBT特性比較二、碳化硅MOSFET器件比導(dǎo)通電阻的優(yōu)化降低碳化硅的比導(dǎo)通電阻,影響比導(dǎo)通電阻有以下幾個(gè)因素:

2.1碳化硅MOSFET的遷移率

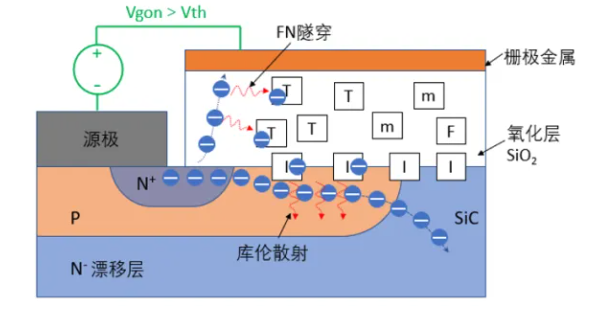

根據(jù)在MOSFET中的位置可以分為溝道遷移率和體遷移率:當(dāng)MOSFET導(dǎo)通時(shí),柵極下方的溝道內(nèi)的遷移率我們稱之為溝道遷移率;在遠(yuǎn)離柵極和材料表面的區(qū)域,我們稱之為體遷移率。溝道遷移率可通過(guò)測(cè)量MOSFET的輸出特性來(lái)得到:這里又可以將其分為(1)有效遷移率;(2)場(chǎng)效應(yīng)遷移率;3)飽和遷移率。溝道遷移率受到SiC/SiO2界面處的許多缺陷的限制,這導(dǎo)致器件的場(chǎng)效應(yīng)遷移率比其霍爾遷移率低兩個(gè)數(shù)量級(jí)。一般認(rèn)為:SiC中Si的選擇性氧化導(dǎo)致碳沉淀并在SiO2中形成碳團(tuán)簇(C-cluster),從氧化動(dòng)力學(xué)角度考慮界面的化學(xué)勢(shì)發(fā)現(xiàn),界面的動(dòng)態(tài)平衡性(dynamic equilibrium)限制了很高的碳化學(xué)勢(shì),從而導(dǎo)致了界面C-cluster缺陷具有較低的形成能,解釋了高的界面態(tài)密度的成因,而其缺陷能級(jí)位置靠近SiC的導(dǎo)帶底,因此降低了載流子的遷移率。SiC MOSFET反型溝道電子主要散射機(jī)制包括:界面態(tài)電荷的庫(kù)倫散射、體晶格散射、離化雜質(zhì)庫(kù)倫散射、表面粗糙散色以及表面聲子散射。下圖為SiC MOSFET溝道處的電子散射情況:

△ 圖3溝道處電子遷移率影響因素4H-SiC界面處主要由類受主缺陷對(duì)器件性能產(chǎn)生影響,庫(kù)倫遷移率決定于界面陷阱對(duì)溝道電子的散射。在降低比導(dǎo)通電阻方面,平面SiC MOSFET中JFET的電阻、MOSFET體電阻以及高濃度襯底電阻為總比導(dǎo)通電阻提供了相當(dāng)大的貢獻(xiàn)。在降低JFET電阻方面,出現(xiàn)了從平面MOSFET向Trench MOSFET的過(guò)度。

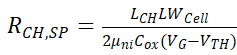

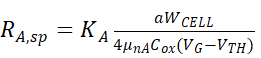

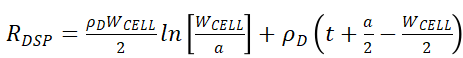

2.2.器件結(jié)構(gòu)設(shè)計(jì)優(yōu)化降低比導(dǎo)通電阻其中溝道電阻:

其中 積累電阻:

積累電阻: JFET區(qū)電阻:

JFET區(qū)電阻: 漂移區(qū)電阻為:

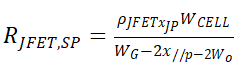

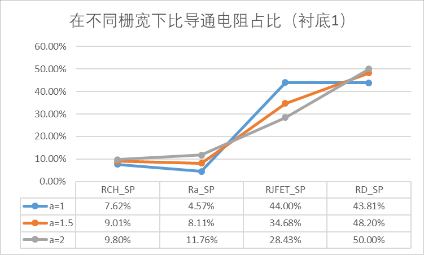

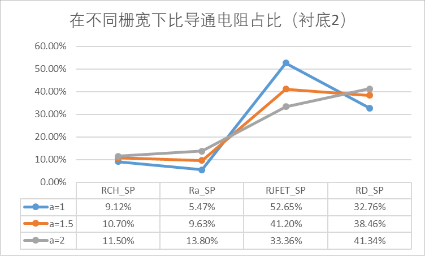

漂移區(qū)電阻為: 以一顆pitch 5.0μm的SiC MOSFET為例,柵氧化層厚度約450A,Vth~3.0V,LCH=0.5μm,改變柵寬來(lái)調(diào)整a的數(shù)值,在a=1μm,1.5μm,2μm條件下 ,以JFET平均濃度,漂移區(qū)厚度約10μm時(shí):

以一顆pitch 5.0μm的SiC MOSFET為例,柵氧化層厚度約450A,Vth~3.0V,LCH=0.5μm,改變柵寬來(lái)調(diào)整a的數(shù)值,在a=1μm,1.5μm,2μm條件下 ,以JFET平均濃度,漂移區(qū)厚度約10μm時(shí):

△表1使用襯底1時(shí)比導(dǎo)通電阻構(gòu)成

△ 表2 使用襯底2 時(shí)比導(dǎo)通電阻構(gòu)成

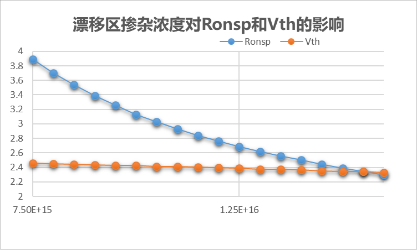

△ 表3 漂移區(qū)濃度對(duì)Ronsp和Vth的影響

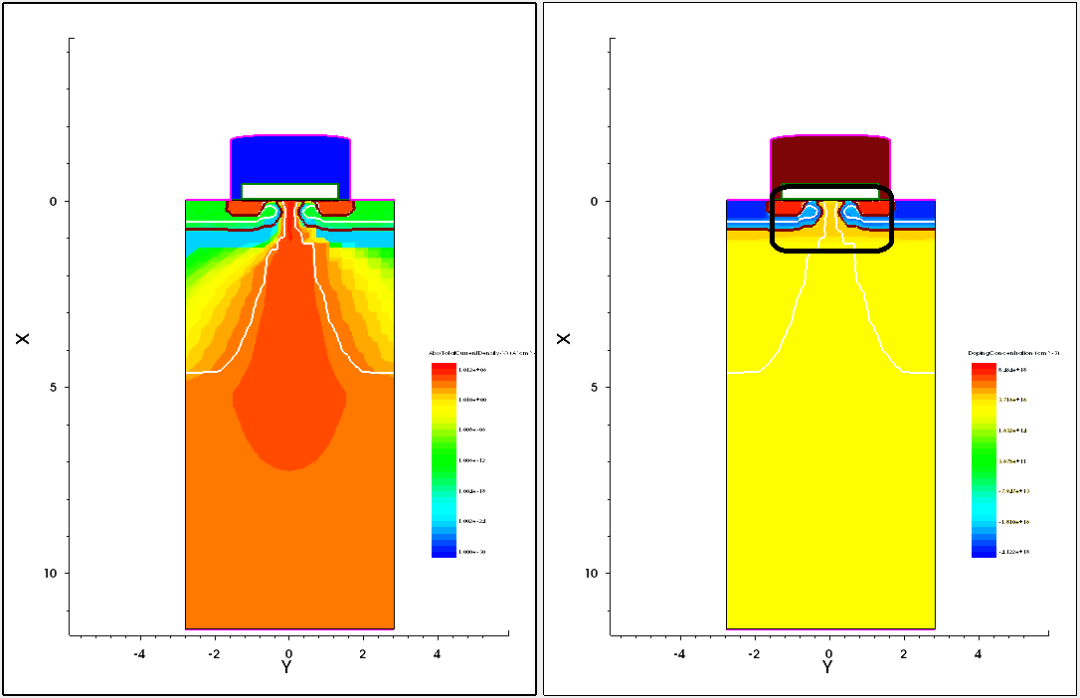

△ 圖4SiC MOSFET電流擴(kuò)展圖及JFET區(qū)域

摻雜分布外延層厚度和摻雜濃度一定的情況下:降低JFET區(qū)電阻、并優(yōu)化電流擴(kuò)展區(qū)濃度對(duì)降低總比導(dǎo)通電阻貢獻(xiàn)較大,RDsp與器件襯底狀態(tài)相關(guān)性高,需達(dá)到外延摻雜濃度和厚度的折中設(shè)計(jì)。減薄襯底厚度:當(dāng)減薄厚度由175μm降低到110μm時(shí),對(duì)于常見(jiàn)的1200V/80mohm SiC Planar Mosfet,預(yù)計(jì)導(dǎo)通電阻降低3mohm左右,換算成比導(dǎo)通電阻降低約0.13mohm.cm2。2.3.Trench MOSFET取代Planar MOSFET降低比導(dǎo)通電阻

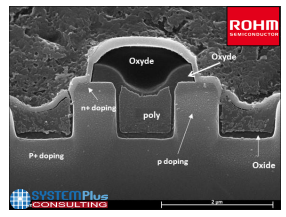

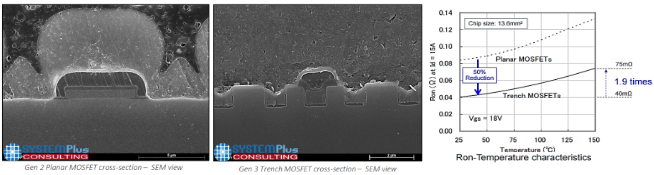

目前SiC MOSFET也正迎來(lái)從planar MOSFET向Trench MOS方向發(fā)展的趨勢(shì),Planar MOSFET JFET區(qū)域電阻在總導(dǎo)通電阻中占比較大,而Trench MOS理論上不存在JFET區(qū)域。

△ 圖5ROHM Trench MOSFET結(jié)構(gòu)

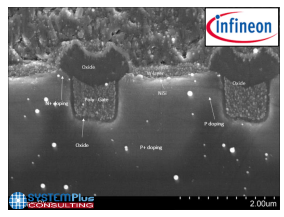

△ 圖6英飛凌Trench MOSFET結(jié)構(gòu)以ROHM代表的雙溝槽結(jié)構(gòu)和infineon為代表的半包結(jié)構(gòu)代表SiC Trench MOSFET獨(dú)立發(fā)展的兩種結(jié)構(gòu)。下圖為ROHM公司從平面結(jié)構(gòu)向Trench發(fā)展的Ron的表現(xiàn)。

△ 圖7ROHM 平面與溝槽MOSFET結(jié)構(gòu)對(duì)比即比導(dǎo)通電阻比較

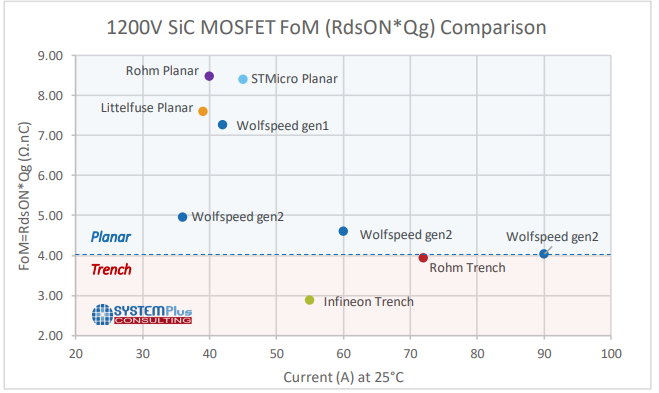

三、主流產(chǎn)品的性能比較下圖為目前市面上各主要大廠的MOSFET性能比較:

△ 圖8各主要廠商SiC MOSFET比導(dǎo)通電阻比較

四、結(jié)論

碳化硅MOSFET以低損耗,高阻斷,高溫工作,開關(guān)速度快等各優(yōu)勢(shì),不過(guò)在技術(shù)方面:SiC單晶材料雖然在導(dǎo)致SiC功率半導(dǎo)體性能和可靠性下降的致命缺陷微管密度降低和消除方面近年來(lái)取得很大進(jìn)展,但位錯(cuò)缺陷等其他缺陷對(duì)元件特性造成的影響仍未解決。碳化硅MOSFET器件目前存在兩個(gè)主要技術(shù)難點(diǎn)沒(méi)有完全突破:低反型層溝道遷移率和高溫、高電場(chǎng)下柵氧可靠性。在碳化硅MOSFET克服以上問(wèn)題后,將迎來(lái)爆發(fā)式的增長(zhǎng)。

-

MOSFET

+關(guān)注

關(guān)注

147文章

7234瀏覽量

213983 -

低功耗

+關(guān)注

關(guān)注

10文章

2418瀏覽量

103842 -

碳化硅

+關(guān)注

關(guān)注

25文章

2816瀏覽量

49193

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

碳化硅材料的特性和優(yōu)勢(shì)

40mR/650V SiC 碳化硅MOSFET,替代30mR 超結(jié)MOSFET或者20-30mR的GaN!

產(chǎn)SiC碳化硅MOSFET功率模塊在工商業(yè)儲(chǔ)能變流器PCS中的應(yīng)用

什么是MOSFET柵極氧化層?如何測(cè)試SiC碳化硅MOSFET的柵氧可靠性?

高導(dǎo)熱高絕緣低介電材料 | 氮化硼散熱膜

高絕緣散熱材料 | 石墨片氮化硼散熱膜復(fù)合材料

碳化硅 (SiC) 與氮化鎵 (GaN)應(yīng)用 | 氮化硼高導(dǎo)熱絕緣片

碳化硅與氮化鎵哪種材料更好

V0阻燃等級(jí)氮化硼高導(dǎo)熱絕緣片

5G通信散熱的VC及絕緣導(dǎo)熱透波氮化硼材料

碳化硅MOSFET與硅MOSFET的應(yīng)用對(duì)比分析

碳化硅壓敏電阻 - 氧化鋅 MOV

一文了解SiC碳化硅MOSFET的應(yīng)用及性能優(yōu)勢(shì)

低功耗碳化硅 MOSFET 的發(fā)展 | 氮化硼高導(dǎo)熱絕緣片

低功耗碳化硅 MOSFET 的發(fā)展 | 氮化硼高導(dǎo)熱絕緣片

評(píng)論