作者:Chang Fei Yee,是德科技(Keysight)

隨著物聯(lián)網(wǎng)(IoT)和5G行動(dòng)寬帶應(yīng)用的興起,預(yù)計(jì)總體數(shù)據(jù)流量將會(huì)迅速增長(zhǎng),400G以太網(wǎng)絡(luò)(400GbE)作為新一代有線通訊標(biāo)準(zhǔn),能夠有力支持這一趨勢(shì)。在400GbE通訊的實(shí)施中,其電氣接口在8信道上傳輸4電平脈沖幅度調(diào)制(PAM4)訊令。每信道50Gbps,總共8個(gè)信道結(jié)合起來(lái),使以太網(wǎng)絡(luò)的總帶寬可以達(dá)到400Gbps。IEEE802.3bs定義了使用50Gbps(即25GBaud)PAM4訊令的400GbE的電氣規(guī)范。

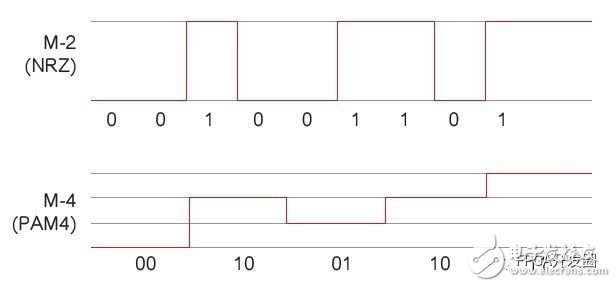

PAM4具有4種數(shù)字幅度電平,如圖1所示。與NRZ相比,PAM4的優(yōu)勢(shì)是每個(gè)電平或符碼都包含兩個(gè)信息bit,在相同的波特率下,吞吐量是NRZ的兩倍。

圖1 NRZ與PAM4的對(duì)比。在相同的波特率下,PAM4的吞吐量是NRZ的兩倍。

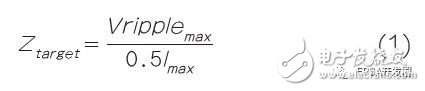

考慮電源完整性的關(guān)鍵設(shè)計(jì)實(shí)現(xiàn)一旦PDN上的開(kāi)關(guān)噪聲耦合至收發(fā)器集成電路(IC)的電源層,傳輸訊號(hào)中將感應(yīng)到抖動(dòng),這可能會(huì)增加接收IC中的bit誤碼率。為了讓噪聲波紋保持在較小水平,符合設(shè)計(jì)規(guī)范,PDN阻抗應(yīng)低于目標(biāo)阻抗。目標(biāo)阻抗由公式1決定。

公式中: Vripplemax= 電源軌上的最大波紋; Imax= 由集成電路載入的最大電流。

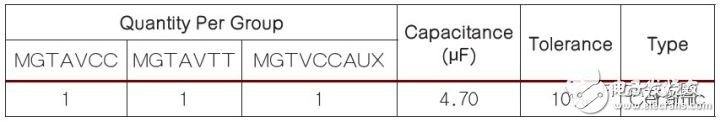

為了最大限度降低PDN阻抗,要特別關(guān)注去耦電容、互連電感和電源平面電容等印刷電路板(PCB)組件。去耦電容應(yīng)安裝在靠近高速收發(fā)器電源接腳的位置,以減少PDN阻抗,進(jìn)而在噪聲耦合進(jìn)收發(fā)器IC封裝電源平面之前,減少來(lái)自外部源(如穩(wěn)壓器和其他開(kāi)關(guān)IC)的噪聲,高速收發(fā)器電源接腳的噪聲將低于10mVpp。為賽靈思(Xilinx)FPGA上的高速收發(fā)器電源接腳推薦的最小電容數(shù)量如表1所示,在靠近每個(gè)高速收發(fā)器電源組(即MGTAVCC、MGTAVTT和MGTVCCAUX)的位置都安裝了1個(gè)4.7μF陶瓷電容器。

表1 為Xilinx FPGA上的高速收發(fā)器電源接腳推薦的電容數(shù)量。

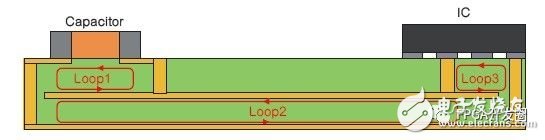

當(dāng)互連電感減少時(shí),PDN阻抗會(huì)相應(yīng)降低。互連電感主要由走線(連接電容的貼裝焊盤(pán)與過(guò)孔)的寄生電感引起。根據(jù)圖2所示的印刷電路板的剖面圖,每個(gè)互連回路(圖中標(biāo)示為回路1、2、3)中都會(huì)形成互連電感。去耦電容器要盡量安裝在靠近IC電源接腳的位置,以最大限度減少互連電感。

圖2 印刷電路板內(nèi)的互連電感。

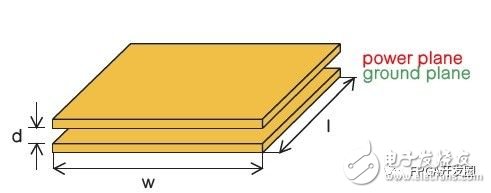

當(dāng)印刷電路板迭層中的電源平面和接地面之間形成的平面電容增加時(shí),PDN阻抗會(huì)降低。參見(jiàn)圖3所示的平面電容基礎(chǔ)模型和公式2,透過(guò)縮小平行面之間的厚度,增加電源平面與接地面之間并行面的面積,或使用具有較大介電常數(shù)的基片,電容會(huì)相應(yīng)升高。

公式中: εr = 基片的介電常數(shù); εo = 真空介電常數(shù); w = 銅片寬度; l = 銅片長(zhǎng)度; d = 基片厚度。

圖3 印刷電路板迭層中的平面電容基礎(chǔ)模型。

實(shí)現(xiàn)考慮訊號(hào)完整性的關(guān)鍵設(shè)計(jì)根據(jù)指南,印刷電路板上走線長(zhǎng)度達(dá)到8英吋的PAM4通道在14GHz和28GHz分別具有低于10dB和20dB的插入損耗,從而在收發(fā)器之間實(shí)現(xiàn)無(wú)縫數(shù)據(jù)通訊。以下將從訊號(hào)完整性的視角討論7個(gè)關(guān)鍵設(shè)計(jì)實(shí)踐。

1.為印刷電路板基片選擇低損耗材料 根據(jù)介電特性(例如損耗正切和介電損耗),印刷電路板基片介電材料可以分為3類。

如表2表示,高損耗材料(如Nelco N4000-6)的損耗正切值超過(guò)0.02,介電常數(shù)超過(guò)4;中等損耗材料(如Isola FR408)的損耗正切值約為0.01,介電常數(shù)在3和4之間;低損耗材料(如Duroid 5870)的損耗正切值約為0.001,介電常數(shù)低于3。介電衰減與損耗正切和介電常數(shù)的平方根成正比,如公式3所示。

介電衰減 = 0.91×.×損耗正切 ×√εr dB/cm (3)

公式中: εr = 介電常數(shù)(Dk); f= 頻率(GHz)

表2 介電材料種類。

利用公式1在14GHz頻率和8英吋走線長(zhǎng)度條件下進(jìn)行計(jì)算,從結(jié)果可見(jiàn),高、中和低損耗材料的介電衰減分別為12.35dB、4.91dB和0.47dB。之前已經(jīng)提到,在14GHz頻率、8英吋走線長(zhǎng)度條件下,插入損耗低于10dB,應(yīng)選擇較低損耗的材料,以便為其他通道損耗留出裕量。

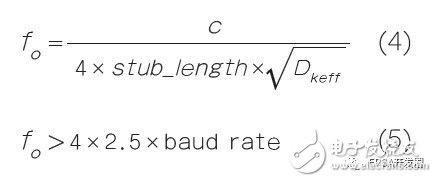

2.最大限度減少過(guò)孔殘樁 當(dāng)使用過(guò)孔來(lái)連接印刷電路板走線至IC時(shí),應(yīng)使用盲孔或反鉆孔(如圖4所示),以最大限度減少殘樁長(zhǎng)度,進(jìn)而提高1/4波諧振頻率,增加物理層鏈路的帶寬。參考公式4,1/4波諧振頻率與殘樁長(zhǎng)度成反比。重新排列公式4和5,對(duì)于使用低損耗材料的印刷電路板上的50Gbps(即25GBaud/s)PAM4傳輸,Dkeff為2.33,最大殘樁長(zhǎng)度可以達(dá)到大約16mil。

公式中: fo = 1/4波諧振頻率(Hz); c = 光速(約12英吋/ns); 殘樁長(zhǎng)度(英吋); Dkeff=有效介電常數(shù)。

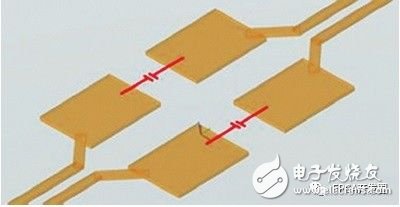

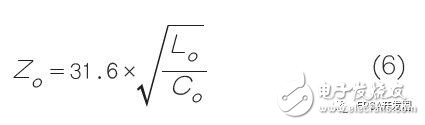

3.最大限度減少交流耦合電容表面貼裝焊盤(pán)造成的阻抗失配 與印刷電路板走線相比,交流耦合電容表面貼裝焊盤(pán)使用的銅片更寬。例如,0402封裝中的電容貼裝焊盤(pán)寬度為20mil,而0603封裝的焊盤(pán)寬度為30mil。圖5顯示與100Ω差分走線(differential trace)串聯(lián)的電容器表面貼裝焊盤(pán)的3D模型,從圖中可以看出,沿著這些6mil寬的銅片走線傳播的訊號(hào),一旦到達(dá)更寬的銅片焊盤(pán)(例如0603封裝的30mil寬度),會(huì)遇到阻抗不連續(xù)性。根據(jù)公式6和7,銅片的橫截面積越大,電容就越大,導(dǎo)致傳輸線特征阻抗出現(xiàn)電容不連續(xù)性(如下降)。

圖4 盲孔或反鉆孔。

圖5 使用Keysight EMPro建模電容表面貼裝焊盤(pán)與差分走線串聯(lián)。

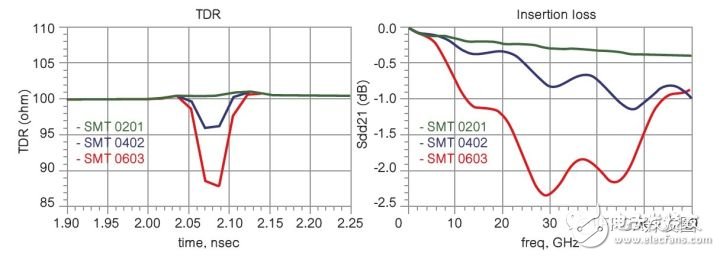

從圖6的時(shí)域反射計(jì)(TDR)和Sdd21曲線可知,焊盤(pán)越寬,阻抗不連續(xù)性就越大,這種不連續(xù)性會(huì)產(chǎn)生更嚴(yán)重的訊號(hào)反射,進(jìn)而引起更大的插入損耗。0603和0402在14GHz時(shí)的衰減分別為1.2dB和0.4dB,至少兩倍于0201(即0.2dB)的情況。因此,設(shè)計(jì)師應(yīng)該使用封裝更小的電容器,例如0201(即10mil寬焊盤(pán))來(lái)最大限度減小不連續(xù)性。

公式中: Lo = 傳輸線單位長(zhǎng)度的固有回路電感(nH/cm); Co = 傳輸線單位長(zhǎng)度的固有電容(pF/cm); Zo= 特征阻抗(Ω);

公式中: C = 電容(pF); Εr = 基片的相對(duì)介電常數(shù); εo = 真空介電常數(shù); w = SMT焊盤(pán)寬度(cm); l = SMT焊盤(pán)長(zhǎng)度(cm); d = SMT焊盤(pán)和參考面底部之間的距離(cm)。

圖 6及7 使用Keysight EMPro模擬不同表面貼裝焊盤(pán)寬度的TDR和Sdd21與500mil長(zhǎng)的印刷電路板走線串聯(lián)。

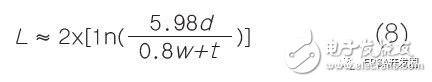

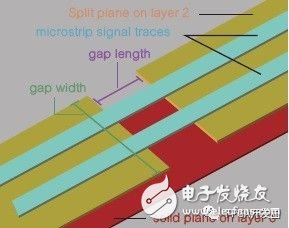

4.提供連續(xù)參考面 當(dāng)印刷電路板走線跨越2個(gè)分離平面之間的間隙時(shí)(圖7粗黑線所示),會(huì)遇到電感阻抗不連續(xù)性或瑕疵參考。這一現(xiàn)象可用公式6和8分別確定。為了研究瑕疵參考的影響,在EMPro中建立并模擬跨越分離平面的傳輸線3D模型,如圖8所示。微帶差分走線跨越了100mil長(zhǎng)和250mil寬的間隙,間隙深度為微帶差分走線與第三層固體面的間距,跨越間隙時(shí),走線與參考底面之間的距離會(huì)增加(即電流返回路徑變長(zhǎng)),導(dǎo)致電感升高,從而引起間隙的走線阻抗增加。

圖8 印刷電路板俯視圖—訊號(hào)跨越分離面。

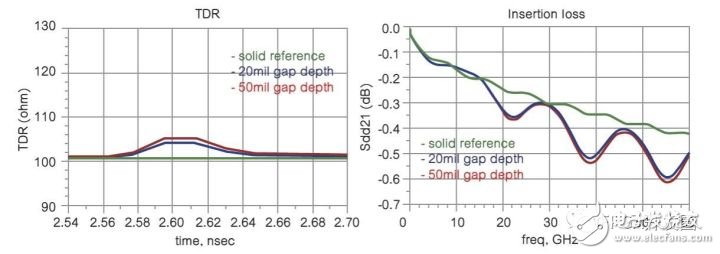

圖9中的TDR和Sdd21曲線證實(shí)了非固體參考面對(duì)訊號(hào)完整性的負(fù)面影響,跨越分離面會(huì)產(chǎn)生更大的電感阻抗不連續(xù)性,進(jìn)而導(dǎo)致更高的插入損耗。因此,確保固體參考面覆蓋整個(gè)走線長(zhǎng)度路徑十分重要。

公式中:L = 銅走線的寄生電感(nH); d = 銅走線和參考底面之間的距離(cm); w = 銅走線寬度(cm); t = 銅走線厚度(cm); x = 銅走線長(zhǎng)度(cm)。

圖9 Keysight EMPro中差分走線跨越分離面的模型。

5.最大限度減少訊號(hào)串?dāng)_ 串?dāng)_會(huì)引起受擾訊號(hào)出現(xiàn)噪聲感應(yīng),從而導(dǎo)致接收集成電路的誤碼增加。因此,帶狀在線使用非交叉布線,因?yàn)镕EXT相比NEXT更低;而在微帶在線使用交叉布線,因?yàn)榕cFEXT相比NEXT更低。除此之外,差分對(duì)間間隔應(yīng)至少是走線寬度的三倍。

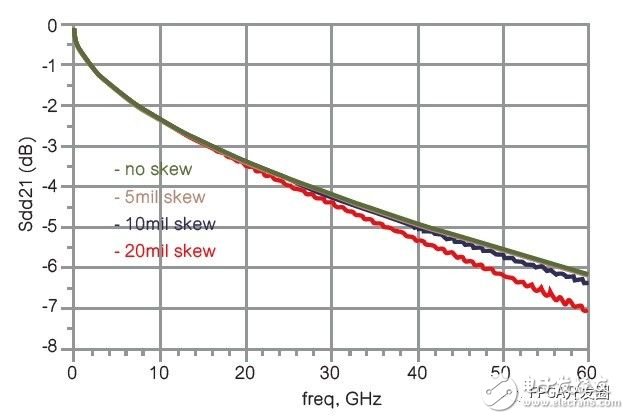

6.差分對(duì)內(nèi)偏移 印刷電路板走線中的差分對(duì)內(nèi)偏移會(huì)帶來(lái)更高的插入損耗,從而增加物理層鏈路的誤碼率。由于反相和非反相訊號(hào)的相位并不是正好相差180度,所以差分模式中的眼圖高度會(huì)變小。圖11中的Sdd21曲線顯示了差分對(duì)內(nèi)偏移對(duì)訊號(hào)完整性的影響,偏移越大,插入損耗越高。因此,每個(gè)物理層鏈路的差分對(duì)內(nèi)偏移都應(yīng)限制在5mil以內(nèi),以減少傳輸損耗,可以使用蛇形布線技術(shù)來(lái)最大限度減少偏移。

圖10 使用Keysight EMPro模擬、帶固體參考面并跨越分離面的500mil長(zhǎng)印刷電路板走線的TDR和Sdd21。

圖11 使用Keysight ADS模擬、具有不同差分對(duì)內(nèi)偏移的8英吋長(zhǎng)印刷電路板走線的Sdd21。

7.光纖編織 印刷電路板介電基片由編織玻璃纖維與環(huán)氧樹(shù)脂結(jié)合組成。圖12是使用顯微鏡看到的、采用纖維編織樣式106和7628制成的印刷電路板基片的俯視圖,淺棕色粗線是玻璃纖維編織部分;黑色的方塊是環(huán)氧樹(shù)脂。編號(hào)更高的玻璃纖維樣式,如7628,可以實(shí)現(xiàn)更密集的玻璃纖維編織。

圖12 印刷電路板的介電基片是利用玻璃纖維樣式106和7628編織的纖維織物。

玻璃纖維與環(huán)氧樹(shù)脂的介電屬性截然不同。例如,NE玻璃纖維的介電常數(shù)(Dk)和損耗正切(Df)分別為4.4和0.0006;E玻璃纖維的Dk和Df分別為6.6和0.0012,而環(huán)氧樹(shù)脂的Dk為3.2,遠(yuǎn)遠(yuǎn)低于玻璃纖維的對(duì)應(yīng)值。當(dāng)使用較為稀疏的纖維編織做基片時(shí),印刷電路板走線能夠更頻繁地穿過(guò)樹(shù)脂和玻璃纖維的不同區(qū)域,結(jié)果就是,訊號(hào)沿著走線從發(fā)送端傳輸?shù)浇邮斩耍渌俣然騻鞑パ舆t經(jīng)常會(huì)發(fā)生變化。它們之間的關(guān)系可以透過(guò)公式9來(lái)說(shuō)明。

公式中:V = 訊號(hào)在印刷電路板上的速度(英吋/ns); C = 光速(約12英吋/ns); Dk = 介電常數(shù)。

這種情況為50Gbps訊號(hào)傳輸帶來(lái)了巨大挑戰(zhàn)。例如,在最壞情況下,非反相訊號(hào)走線可能穿過(guò)玻璃纖維但沒(méi)有穿過(guò)環(huán)氧樹(shù)脂,而反相訊號(hào)的走線可能穿過(guò)很多樹(shù)脂區(qū)域。結(jié)果,由于反相訊號(hào)遇到不斷變化的傳播延遲,非反相訊號(hào)與反相訊號(hào)之間的相位差在接收端一般會(huì)遠(yuǎn)遠(yuǎn)小于180o。上升端和下降端之間的大偏移或錯(cuò)位,導(dǎo)致眼圖寬度和高度減少,而且,接收端會(huì)出現(xiàn)高誤碼率。因此,解決辦法就是采用更密集的纖維編織。

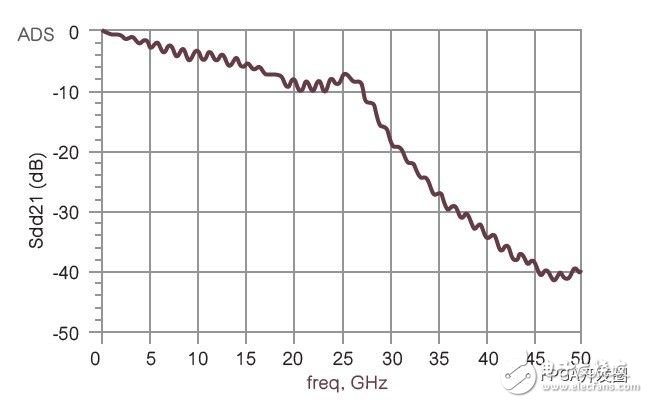

布局后的通道仿真一旦按照上述關(guān)鍵實(shí)踐完成了印刷電路板布局設(shè)計(jì),布局檔將導(dǎo)入Keysight EMPro進(jìn)行3DEM模擬。選擇圖13中突出顯示的8英吋長(zhǎng)差分走線進(jìn)行s參數(shù)抽取,將其導(dǎo)入Keysight ADS進(jìn)行布局后PAM4通道仿真。圖14中的插入損耗曲線顯示提取的差分走線符合規(guī)定的閾值,即在14GHz時(shí)低于10dB;在28GHz時(shí)低于20dB。

圖13 選擇差分走線用于3DEM模擬。

圖14 印刷電路板上所選PAM4差分走線的插入損耗曲線。

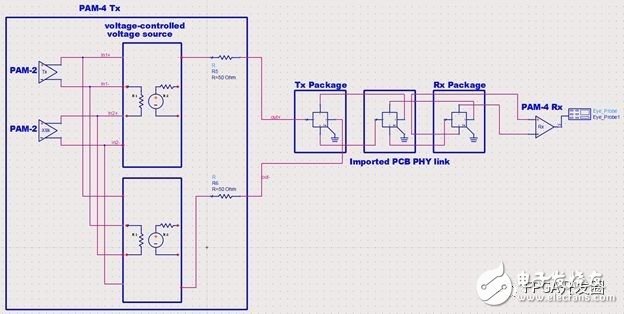

圖15顯示使用Keysight ADS生成的通道分析拓?fù)洌瑑蓚€(gè)25GBaud/s的PAM2訊號(hào)注入壓控電壓源以生成PAM4訊號(hào)。PAM4波形的傳播路徑為:發(fā)射端封裝、8英吋PCB走線(即圖13中顯示的傳輸線)、接收端封裝,最后是接收端。在發(fā)射端,訊號(hào)幅度和上升/下降時(shí)間分別為1.2Vpp和16ps。

圖15 使用Keysight ADS在25GBaud/s下進(jìn)行布局后PAM4通道仿真。

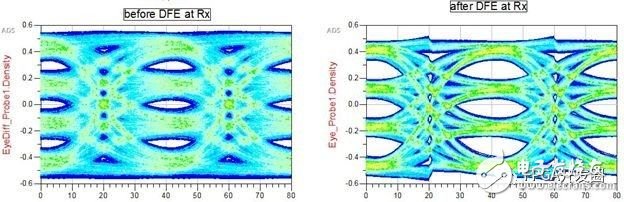

PAM4訊號(hào)的最小眼寬和眼高分別為1/4單位間隔(即25GBaud/s數(shù)據(jù)速率下為10ps)和50mV。如圖16所示,PAM4眼圖有4個(gè)數(shù)字幅度電平,因此有3個(gè)眼圖。在啟用決策回饋均衡(DFE)前,接收端訊號(hào)的眼高和眼寬分別為60mV和14ps,一旦啟用接收端的6接頭DFE,眼圖幾乎變大一倍(即140mV眼高和23ps眼寬),結(jié)果符合指南中的技術(shù)指針。均衡方案的選擇和接頭的調(diào)節(jié)很大程度上取決于通道的插入損耗或頻率響應(yīng)。本文進(jìn)行了多次嘗試來(lái)獲得更好的開(kāi)眼結(jié)果。

圖16 從圖15中的通道仿真結(jié)果得到的接收端眼圖。

結(jié)論實(shí)施50Gbps PAM4物理層鏈路時(shí)必須嚴(yán)格要求,確保在高速收發(fā)器之間實(shí)現(xiàn)穩(wěn)定的通訊。

-

物聯(lián)網(wǎng)

+關(guān)注

關(guān)注

2912文章

44882瀏覽量

375695 -

5G

+關(guān)注

關(guān)注

1356文章

48497瀏覽量

565393 -

耦合電容

+關(guān)注

關(guān)注

2文章

154瀏覽量

19873

原文標(biāo)題:實(shí)現(xiàn)優(yōu)化PAM4印刷電路板

文章出處:【微信號(hào):FPGA-EETrend,微信公眾號(hào):FPGA開(kāi)發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

是德示波器在電源完整性分析中的應(yīng)用

聽(tīng)懂什么是信號(hào)完整性

電源完整性分析參考解決方案

高速PCB的信號(hào)完整性、電源完整性和電磁兼容性研究

高速電路電源分配網(wǎng)絡(luò)設(shè)計(jì)與電源完整性分析

信號(hào)完整性與電源完整性-電源完整性分析

信號(hào)完整性與電源完整性-差分對(duì)的特性

信號(hào)完整性與電源完整性-信號(hào)的串?dāng)_

信號(hào)完整性與電源完整性 第一章 概論

示波器探頭在電源完整性測(cè)量上的應(yīng)用

搞定電源完整性,不如先研究PDN

電源完整性關(guān)鍵設(shè)計(jì)實(shí)現(xiàn)介紹

電源完整性關(guān)鍵設(shè)計(jì)實(shí)現(xiàn)介紹

評(píng)論