將浮點轉(zhuǎn)為定點,大幅降低功耗和成本

(WP491)

賽靈思器件和工具支持從二進制到雙精度在內(nèi)的多種數(shù)據(jù)類型。UltraScale 架構的可擴展精度提供極大靈活性,便于優(yōu)化功耗和資源利用,同時滿足設計性能目標要求。

摘 要

在數(shù)據(jù)中心、航空航天與軍用、5G 無線以及汽車等領域,客戶必須滿足高級駕駛員輔助 (ADAS)、雷達和深度學習等應用中嚴峻的散熱、功耗和成本要求。

要實現(xiàn)這些目標,一種極為有效的方法是用定點數(shù)實現(xiàn)信號處理鏈。賽靈思FPGA 和 SoC 具備固有的可變精度支持,允許客戶輕松調(diào)整以適應不斷演變的朝更低精度解決方案發(fā)展的這種行業(yè)趨勢。

賽靈思提供一種包含 Vivado? 高層次綜合 (HLS) 的工具流程,允許客戶方便地評估 C/C++ 設計的更低精度實現(xiàn)方案,諸如定點等。

點擊“閱讀原文”,可下載完整的中文版 WP491

正 文 章 節(jié)

● 簡介 :賽靈思支持的數(shù)據(jù)類型

賽靈思 All Programmable 器件和工具支持從二進制到雙精度浮點在內(nèi)的多種數(shù)據(jù)類型。用定點實現(xiàn)的設計總是比用浮點實現(xiàn)的同一設計更加高效,因為定點實現(xiàn)方案所占用的資源和消耗的功耗更少。若將設計遷移到定點,功耗和占用面積縮減一半并不稀奇。

●浮點轉(zhuǎn)換為定點的優(yōu)勢

對于目前幾乎所有的設計,最小化功耗是需要優(yōu)先處理的問題。大多數(shù)應用產(chǎn)品必須首先滿足嚴格的功耗和散熱范圍要求,才能投產(chǎn)。普遍接受的一個原則是,浮點設計較之低精度設計而言,功耗更大。

●實例 :將浮點 FIR 濾波器轉(zhuǎn)換為定點

Vivado HLS 中簡單的 FIR 濾波器設計可用來展示浮點 FIR 設計轉(zhuǎn)換為定點設計如何減少所用資源和功耗并實現(xiàn)相近的結果精度。

●大大減少 FPGA 資源占用

本例中的定點 FIR 所占資源不足原始浮點 FIR 的五分之一。

●實現(xiàn)顯著的功耗節(jié)省

將本白皮書中單個 FIR 濾波器的兩種實現(xiàn)方案的功耗估算結果進行比較,發(fā)現(xiàn)定點 FIR 的功耗減少 1.4W。

● 消減材料成本

將浮點設計轉(zhuǎn)換成定點方案,能大大減少 FPGA 資源占用。FPGA 資源的削減能降低材料成本。通過三種方法來實現(xiàn)。

● 相近的精度

通過比較單個 FIR 濾波器設計兩種實現(xiàn)方案的輸出,會發(fā)現(xiàn)定點實現(xiàn)方案提供相近的濾波器精度,精度損失僅為 -100dBm 至 -160dBm,同時能降低功耗和成本。

● 降低時延

對于單個 FIR 設計實例,可通過濾波器降低時延——定點實現(xiàn)方案為 12 個時鐘周期,浮點設計為 91 個時鐘周期。隨著資源用量減少,尤其是 DSP48E2 Slice 減少,有望降低時延。

點擊“閱讀原文”,可下載完整的中文版 WP491

-

Xilinx

+關注

關注

71文章

2170瀏覽量

121879

原文標題:[資料下載] WP_491 將浮點轉(zhuǎn)為定點,大幅降低功耗和成本

文章出處:【微信號:xilinx_inc,微信公眾號:賽靈思】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

#28335 浮點/定點 運用

利用業(yè)界成本最低、功耗最低的FPGA降低系統(tǒng)總成本需要面對哪些挑戰(zhàn)?

請問MATLAB是怎樣解決浮點定點轉(zhuǎn)換問題的?

擴充浮點運算集是否需要自己在FPGA板子上設置一個定點數(shù)轉(zhuǎn)為浮點數(shù)的部分?

德州儀器最新數(shù)據(jù)采集系統(tǒng)可大幅降低功耗、空間和成本

浮點模型的定點化到產(chǎn)品級代碼的生成

浙大研發(fā)的新型存儲器將大幅降低網(wǎng)絡芯片的成本

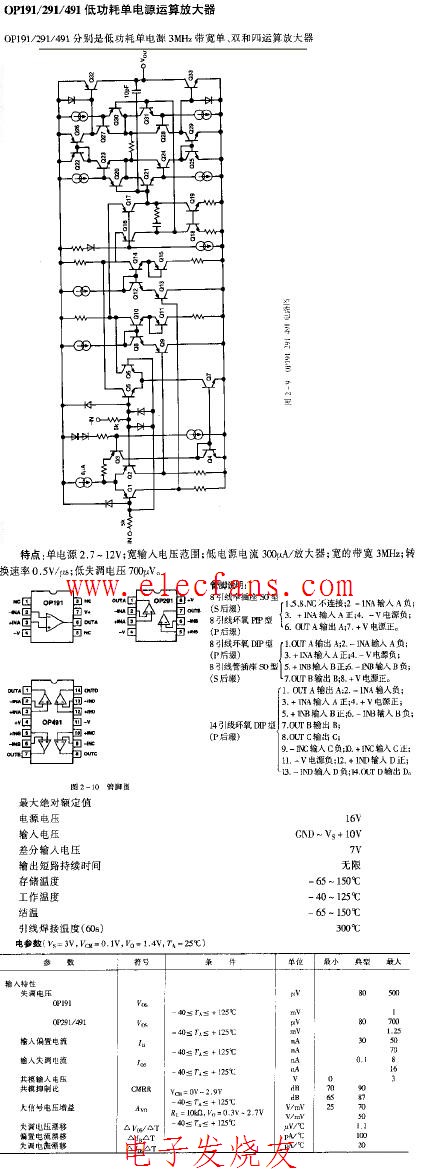

超低功耗浮點DSP TMS320C6745/47的特點性能及應用范圍

低功耗藍牙芯片的應用可顯著降低功耗和成本

WP003-面向物聯(lián)網(wǎng)的可靠、低功耗無線傳感器網(wǎng)絡

WP_491將浮點轉(zhuǎn)為定點,大幅降低功耗和成本

WP_491將浮點轉(zhuǎn)為定點,大幅降低功耗和成本

評論