1. FIFO簡(jiǎn)介

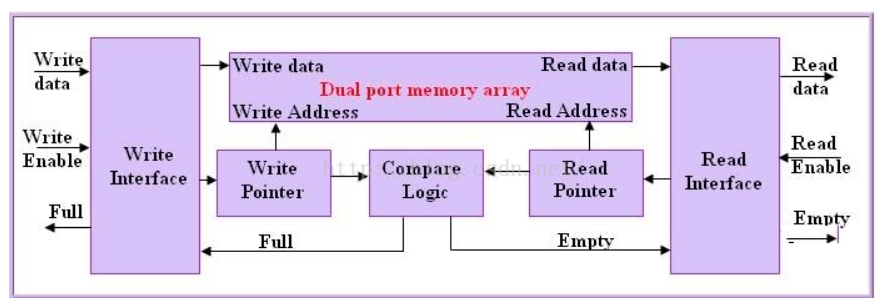

FIFO是一種先進(jìn)先出數(shù)據(jù)緩存器,它與普通存儲(chǔ)器的區(qū)別是沒有外部讀寫地址線,使用起來非常簡(jiǎn)單,缺點(diǎn)是只能順序讀寫,而不能隨機(jī)讀寫。

2. 使用場(chǎng)景

數(shù)據(jù)緩沖:也就是數(shù)據(jù)寫入過快,并且間隔時(shí)間長(zhǎng),也就是突發(fā)寫入。那么通過設(shè)置一定深度的FIFO,可以起到數(shù)據(jù)暫存的功能,且使得后續(xù)處理流程平滑。

時(shí)鐘域的隔離:主要用異步FIFO。對(duì)于不同時(shí)鐘域的數(shù)據(jù)傳輸,可以通過FIFO進(jìn)行隔離,避免跨時(shí)鐘域的數(shù)據(jù)傳輸帶來的設(shè)計(jì)和約束上的復(fù)雜度。比如FIFO的一端是AD,另一端是PCI;AD的采集速率是16位100KSPS,每秒的數(shù)據(jù)量是1.6Mbps。而PCI總線的速度是33MHz,總線寬度是32位

用于不同寬度的數(shù)據(jù)接口。例如單片機(jī)是8位,DSP是16。

3. 分類

同步FIFO:指讀時(shí)鐘和寫時(shí)鐘是同一個(gè)時(shí)鐘

異步FIFO:指讀寫時(shí)鐘是不同的時(shí)鐘。

4. FIFO的常見參數(shù)

FIFO的寬度:即FIFO一次讀寫操作的數(shù)據(jù)位;

FIFO的深度:指的是FIFO可以存儲(chǔ)多少個(gè)N位的數(shù)據(jù)(如果寬度為N)。

滿標(biāo)志:FIFO已滿或?qū)⒁獫M時(shí)由FIFO的狀態(tài)電路送出的一個(gè)信號(hào),以阻止FIFO的寫操作繼續(xù)向FIFO中寫數(shù)據(jù)而造成溢出(overflow)。

空標(biāo)志:FIFO已空或?qū)⒁諘r(shí)由FIFO的狀態(tài)電路送出的一個(gè)信號(hào),以阻止FIFO的讀操作繼續(xù)從FIFO中讀出數(shù)據(jù)而造成無效數(shù)據(jù)的讀出(underflow)。

讀時(shí)鐘:讀操作所遵循的時(shí)鐘,在每個(gè)時(shí)鐘沿來臨時(shí)讀數(shù)據(jù)。

寫時(shí)鐘:寫操作所遵循的時(shí)鐘,在每個(gè)時(shí)鐘沿來臨時(shí)寫數(shù)據(jù)。

5. FIFO設(shè)計(jì)

5.1 空滿標(biāo)志生成

FIFO設(shè)計(jì)的關(guān)鍵是產(chǎn)生可靠的FIFO讀寫指針和生成FIFO空/滿狀態(tài)標(biāo)志。

當(dāng)讀寫指針相等時(shí),表明FIFO為空,這種情況發(fā)生在復(fù)位操作時(shí);或者當(dāng)讀指針讀出FIFO中最后一個(gè)字后,追趕上了寫指針時(shí),這時(shí)FIFO處于滿的狀態(tài)。

為了區(qū)分到底是滿狀態(tài)還是空狀態(tài),可以采用以下方法:

方法1:在指針中添加一個(gè)額外的位(extra bit),當(dāng)寫指針增加并越過最后一個(gè)FIFO地址時(shí),就將寫指針這個(gè)未用的MSB加1,其它位回零。對(duì)讀指針也進(jìn)行同樣的操作。此時(shí),對(duì)于深度為2^n的FIFO,需要的讀/寫指針位寬為(n+1)位,如對(duì)于深度為8的FIFO,需要采用4bit的計(jì)數(shù)器,0000~1000、1001~1111,MSB作為折回標(biāo)志位,而低3位作為地址指針。

如果兩個(gè)指針的MSB不同,說明寫指針比讀指針多折回了一次;如r_addr=0000,而w_addr = 1000,為滿。

如果兩個(gè)指針的MSB相同,則說明兩個(gè)指針折回的次數(shù)相等。其余位相等,說明FIFO為空;

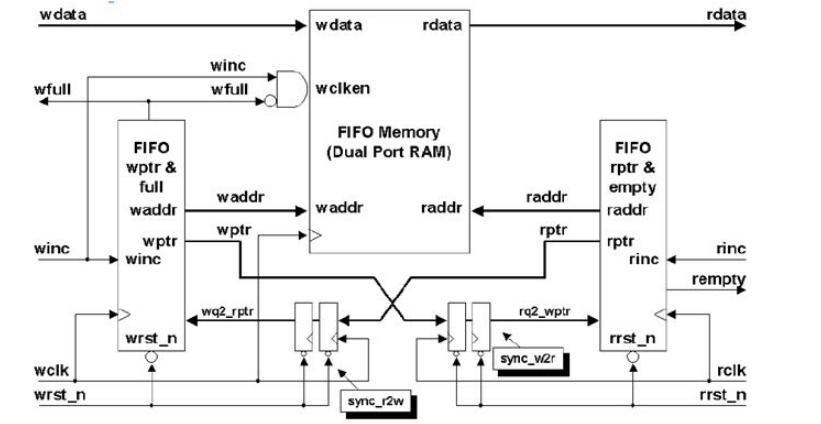

5.2 異步FIFO的設(shè)計(jì)還要注意跨時(shí)鐘域問題

將一個(gè)二進(jìn)制的計(jì)數(shù)值從一個(gè)時(shí)鐘域同步到另一個(gè)時(shí)鐘域的時(shí)候很容易出現(xiàn)問題,因?yàn)椴捎枚M(jìn)制計(jì)數(shù)器時(shí)所有位都可能同時(shí)變化,在同一個(gè)時(shí)鐘沿同步多個(gè)信號(hào)的變化會(huì)產(chǎn)生亞穩(wěn)態(tài)問題。而使用格雷碼只有一位變化,因此在兩個(gè)時(shí)鐘域間同步多個(gè)位不會(huì)產(chǎn)生問題。所以需要一個(gè)二進(jìn)制到gray碼的轉(zhuǎn)換電路,將地址值轉(zhuǎn)換為相應(yīng)的gray碼,然后將該gray碼同步到另一個(gè)時(shí)鐘域進(jìn)行對(duì)比,作為空滿狀態(tài)的檢測(cè)

5.3 gray碼如何判斷空滿

對(duì)于“空”的判斷:依然依據(jù)二者完全相等(包括MSB);

對(duì)于“滿”的判斷:如下圖,由于gray碼除了MSB外,具有鏡像對(duì)稱的特點(diǎn),當(dāng)讀指針指向7,寫指針指向8時(shí),除了MSB,其余位皆相同,不能說它為滿。因此不能單純的只檢測(cè)最高位了,在gray碼上判斷為滿必須同時(shí)滿足以下3條:

wptr和同步過來的rptr的MSB不相等,因?yàn)閣ptr必須比rptr多折回一次。

wptr與rptr的次高位不相等,如上圖位置7和位置15,轉(zhuǎn)化為二進(jìn)制對(duì)應(yīng)的是0111和1111,MSB不同說明多折回一次,111相同代表同一位置。

剩下的其余位完全相等

6.同步FIFO實(shí)現(xiàn)

代碼的核心部分主要是data_count,并且full 信號(hào)是當(dāng)data_count == DATA_DEPTH時(shí)拉高,除了data_count之外,還可以同過判斷r_ptr和w_ptr兩個(gè)指針是否相等來判斷空,滿信號(hào)

代碼的核心部分主要是data_count,并且full 信號(hào)是當(dāng)data_count == DATA_DEPTH時(shí)拉高,除了data_count之外,還可以同過判斷r_ptr和w_ptr兩個(gè)指針是否相等來判斷空,滿信號(hào)

ssign empty = (w_ptr == r_ptr) ? 1 : 0;

assign full = (w_ptr[2:0] == r_ptr[2:0] && (w_ptr[3] == ~r_ptr[3])) ? 1 : 0;

這里還有一個(gè)注意的點(diǎn),也就是w_ptr++會(huì)越界,同步FIFO就算用data_cnt來判斷空滿條件,在存數(shù)據(jù)和寫數(shù)據(jù)時(shí)還是應(yīng)該用w_ptr來表示,如果直接用data_cnt來表示,那么設(shè)計(jì)的就是一個(gè)棧而不是FIFO了。

module syn_fifo( clk, rst_n, data_in, w_en, full, data_out, r_en, empty); parameter DATA_WIDTH = 8; parameter DATA_DEPTH = 16; parameter ADDR_WIDTH = 4; input wire clk, rst_n; input wire [DATA_WIDTH-1:0] data_in; input wire w_en, r_en; output wire empty, full; output reg [DATA_WIDTH-1:0] data_out; reg [ADDR_WIDTH : 0] data_count; reg [ADDR_WIDTH-1 : 0] w_ptr, r_ptr; reg [DATA_WIDTH-1 : 0] mem[0 : DATA_DEPTH-1]; assign empty = (data_count == 'd0) ? 1 : 0; assign full = (data_count == DATA_DEPTH) ? 1 : 0; //data_count == DATA_DEPTH always @ (posedge clk or negedge rst_n) begin if (!rst_n) data_count <= 'd0; else if (w_en && r_en) data_count <= data_count; else if (!full && w_en) data_count <= data_count + 1'b1; else if (!empty && r_en) data_count <= data_count - 1'b1; else data_count <= data_count; end always @ (posedge clk or negedge rst_n) begin if (!rst_n) mem[w_ptr] <= 'd0; else if (!full && w_en) mem[w_ptr] <= data_in; end always @ (posedge clk or negedge rst_n) begin if (!rst_n) w_ptr <= 'd0; else if (w_en && !full) w_ptr <= w_ptr + 1'b1; else w_ptr <= w_ptr; end always @ (posedge clk or negedge rst_n) begin if (!rst_n) r_ptr <= 'd0; else if (r_en && !empty) r_ptr <= r_ptr + 1'b1; else r_ptr <= r_ptr; end always @ (posedge clk or negedge rst_n) begin if (!rst_n) data_out <= 'd0; else if (!empty && r_en) data_out <= mem[r_ptr]; end endmodule

7. 異步FIFO實(shí)現(xiàn)

設(shè)計(jì)難點(diǎn):

跨時(shí)鐘域數(shù)據(jù)比較,需要用到同步器,減少亞穩(wěn)態(tài)的傳遞

用到gray碼,進(jìn)一步減少亞穩(wěn)態(tài)的產(chǎn)生

gray碼相等信號(hào)的比較 空:兩個(gè)gray碼相等 滿:高兩位相反,其余位相同。

指針計(jì)數(shù)需要比ADDR的位寬多一位,這一點(diǎn)和同步FIFO的設(shè)計(jì)是一樣的。

https://www.cnblogs.com/BitArt/archive/2013/04/10/3010073.html

module asyn_fifo(

clk_w,

clk_r,

rst_n,

r_en,

w_en,

data_in,

data_out,

full,

empty

);

input wire clk_r, clk_w, rst_n;

input wire r_en, w_en;

input wire [7:0] data_in;

output wire full, empty;

output reg [7:0] data_out;

parameter DATA_DEPTH = 8;

parameter DATA_WIDTH = 8;

parameter ADDR_WIDTH = 3;

reg [3:0] w_ptr, r_ptr;

reg [7:0] mem[DATA_DEPTH-1 : 0];

always @ (posedge clk_w or negedge rst_n) begin

if (~rst_n)

w_ptr <= 'd0;

else if (w_en && !full)

w_ptr <= w_ptr + 1'b1;

else

w_ptr <= w_ptr;

end

wire [3:0] w_ptr_gray, r_ptr_gray;

assign w_ptr_gray = w_ptr ^ (w_ptr >> 1);

assign r_ptr_gray = r_ptr ^ (r_ptr >> 1);

//

reg [ADDR_WIDTH:0] rd1_wp, rd2_wp;

always @ (posedge clk_r or negedge rst_n) begin

if (!rst_n) begin

rd1_wp <= 'd0;

rd2_wp <= 'd0;

end else begin

rd1_wp <= w_ptr_gray;

rd2_wp <= rd1_wp;

end

end

assign empty = (rd2_wp == r_ptr_gray) ? 1 : 0;

always @ (posedge clk_r or negedge rst_n) begin

if (~rst_n)

r_ptr <= 'd0;

else if (r_en && !empty)

r_ptr <= r_ptr + 1'b1;

else

r_ptr <= r_ptr;

end

//wire [ADDR_WIDTH:0] r_ptr_gray;

assign r_ptr_gray = r_ptr ^ (r_ptr >> 1);

reg [ADDR_WIDTH:0] wd1_rp, wd2_rp;

always @ (posedge clk_w or negedge rst_n) begin

if (~rst_n) begin

wd1_rp <= 'd0;

wd2_rp <= 'd0;

end

else begin

wd1_rp <= r_ptr_gray;

wd2_rp <= wd1_rp;

end

end

assign full = ({(~wd2_rp[ADDR_WIDTH:ADDR_WIDTH-1]),wd2_rp[ADDR_WIDTH-2:0]} == w_ptr_gray) ? 1:0;

always @ (posedge clk_w or negedge rst_n) begin

if (~rst_n)

mem[w_ptr] <= 'd0;

else if (!empty && rd_en)

mem[w_ptr] <= data_in;

end

always @ (posedge clk_r or negedge rst_n) begin

if (~rst_n)

data_out <= 'd0;

else if (!full && w_en)

data_out <= mem[r_ptr];

end

endmodule

8. 對(duì)FIFO進(jìn)行約束

set_false_path

在設(shè)計(jì)中,不需要滿足setup/hold時(shí)序的數(shù)據(jù)路徑需要設(shè)置成false path

set_disable_timing:可以使庫(kù)單元的時(shí)間弧(timing arc)無效

總的來說,set_false_path 只對(duì)data path起作用, EDA 工具還會(huì)分析計(jì)算這條時(shí)序路徑, 只是不報(bào)出來是否有時(shí)序違例。

set_disable_timing 對(duì)timing arc起作用,完全不去分析這條timing arc

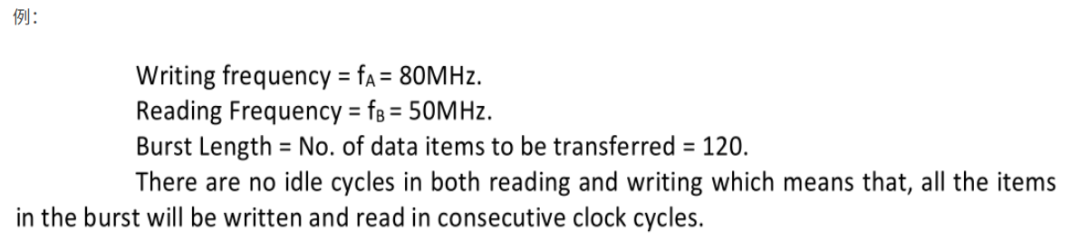

9. 關(guān)于異步FIFO最小深度的計(jì)算

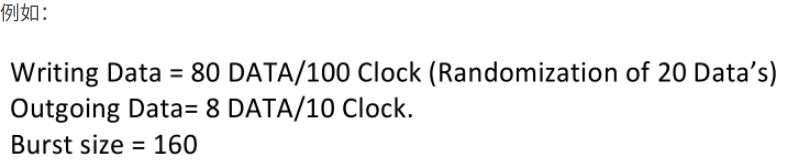

FIFO僅在數(shù)據(jù)突發(fā)時(shí)才有效,不使用與連續(xù)的數(shù)據(jù)輸出和輸入。如果存在連續(xù)的數(shù)據(jù)流,那么所需要的FIFO大小因該是無限的。因此需要知道突發(fā)速率,突發(fā)大小,頻率等,才能確定FIFO的深度。

最小深度的計(jì)算流程

確定讀時(shí)鐘fr和寫時(shí)鐘的頻率fw, 一般情況fw>fr的

根據(jù)fr和fw計(jì)算讀寫一次數(shù)據(jù)的周期Tr 和Tw,根據(jù)T= 1/f

根據(jù)突發(fā)寫長(zhǎng)度的大小,計(jì)算這么多數(shù)據(jù)需要寫多少時(shí)間 tw = Tw*len

根據(jù)寫的時(shí)間tw計(jì)算讀了多少數(shù)據(jù) n = tw/Tr

FIFO的最小深度等于 len-n

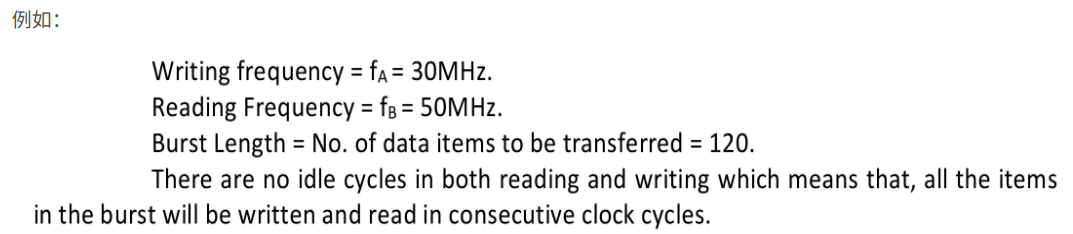

9.1 寫時(shí)鐘快于讀時(shí)鐘,寫和讀的過程中沒有空閑周期

分析過程:

寫時(shí)鐘周期Tw = 1000/80 ns = 12.5ns;同理讀時(shí)鐘周期為20ns;

突發(fā)寫長(zhǎng)度為120個(gè)數(shù)據(jù),寫120個(gè)數(shù)據(jù)耗時(shí)120 * 12.5 = 1500ns;

1500ns時(shí)間內(nèi)讀出數(shù)據(jù)1500/20ns = 75個(gè);

故最小FIFO深度為120 - 75 = 45;

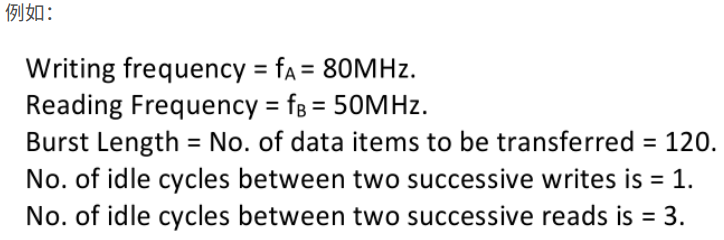

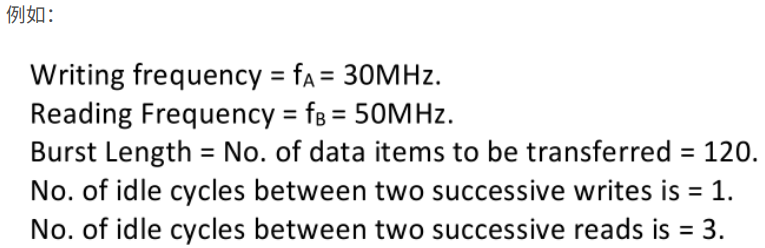

9.2 寫時(shí)鐘頻率大于讀時(shí)鐘頻率,但在讀寫的過程中存在空閑周期

分析:

寫時(shí)鐘周期T_A = 12.5ns,讀時(shí)鐘周期為T_B = 20ns;

兩個(gè)寫時(shí)鐘寫一個(gè)數(shù)據(jù),也就是寫一個(gè)數(shù)據(jù)需要時(shí)間2*T_A = 25ns,那么由于突發(fā)寫數(shù)據(jù)個(gè)數(shù)為120個(gè),寫這么多數(shù)據(jù)需要時(shí)間120 * 25ns = 3000ns;

4個(gè)讀時(shí)鐘周期讀一個(gè)數(shù)據(jù),因此讀一個(gè)數(shù)據(jù)需要時(shí)間80ns,3000ns讀了3000/80 = 37.5個(gè)數(shù)據(jù)(0.5不算一個(gè)數(shù)據(jù),沒讀完整),約等于37個(gè)數(shù)據(jù)。

所以,F(xiàn)IFO的最小深度為120 - 37 = 83;

9.3 寫時(shí)鐘慢于讀時(shí)鐘,且讀寫過程中沒有空閑周期

分析:

這種情況下永遠(yuǎn)也不會(huì)發(fā)生數(shù)據(jù)丟失的情況;

fifo的深度為1

9.4 寫時(shí)鐘頻率小于讀時(shí)鐘頻率,但讀寫過程中存在空閑周期

分析:

寫時(shí)鐘周期1000/30 ns = 100/3 ns;讀時(shí)鐘周期 20ns;

寫一個(gè)數(shù)據(jù)需要2個(gè)時(shí)鐘,也就是200/3 ns;讀一個(gè)數(shù)據(jù)需要4個(gè)時(shí)鐘,也就是80 ns;

寫120個(gè)數(shù)據(jù)需要時(shí)間8000ns,這段時(shí)間內(nèi)讀出數(shù)據(jù)8000/80 = 100個(gè);

因此,F(xiàn)IFO的最小深度為120 - 100 = 20;

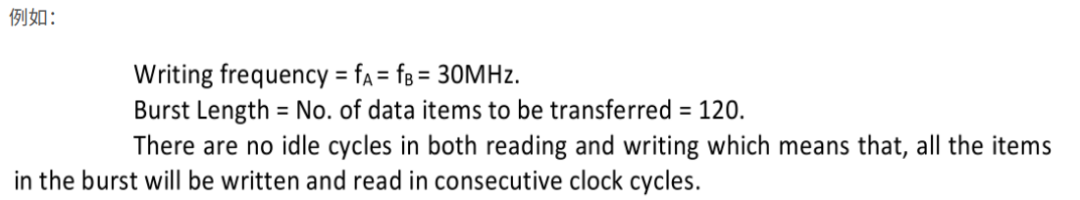

9.5 讀寫時(shí)鐘速率相同,且無空閑時(shí)鐘

分析:

如果讀寫時(shí)鐘之間沒有相位差,則不需要FIFO就可以進(jìn)行讀寫;

如果二者存在相位差,只需要FIFO的深度為1即可。

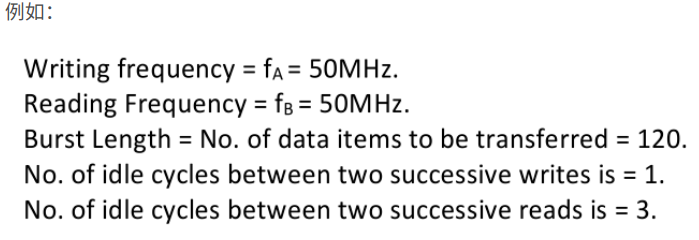

9.6 讀寫時(shí)鐘頻率一致,但在讀寫過程中存在空閑周期

分析:

兩個(gè)時(shí)鐘寫一個(gè)數(shù)據(jù),需要時(shí)間40ns;

4個(gè)時(shí)鐘讀一個(gè)數(shù)據(jù),需要80ns;

由于突發(fā)長(zhǎng)度為120,需要120*40 = 4800ns寫完;這段時(shí)間讀出數(shù)據(jù)個(gè)數(shù):4800/80 = 60;

所以,F(xiàn)IFO最小深度為120 - 60 = 60;

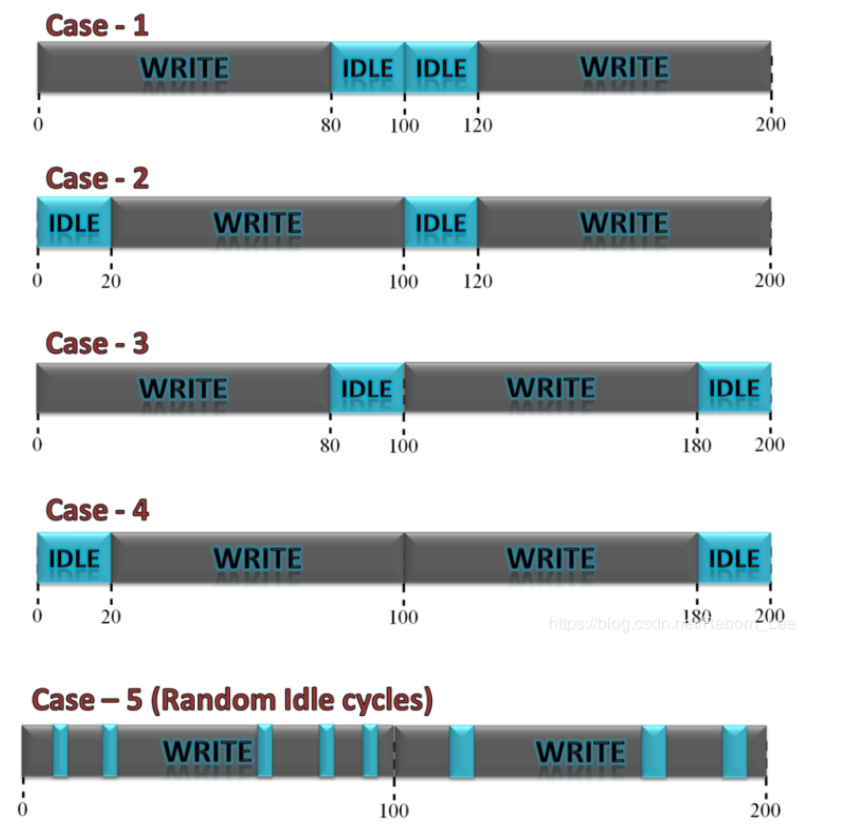

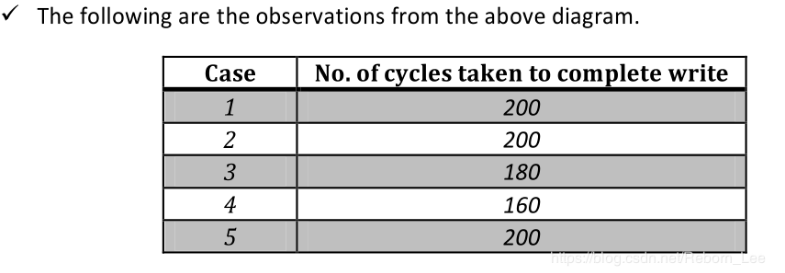

9.7 特定條件下,最壞情況分析FIFO最小深度

首先,從條件可知,寫頻率等于讀頻率;

其次,讀寫可以在如下限制下的任意時(shí)刻發(fā)生:

為了獲得更安全的FIFO深度,我們需要考慮最壞的情況,以防數(shù)據(jù)丟失;

對(duì)于最壞的情況,寫入和讀取之間的數(shù)據(jù)速率之間的差異應(yīng)該是最大的。因此,對(duì)于寫操作,應(yīng)考慮最大數(shù)據(jù)速率,對(duì)于讀操作,應(yīng)考慮最小數(shù)據(jù)速率。從上表可以看出,最快的寫數(shù)據(jù)速率應(yīng)該為第4種情況,寫操作在最小的時(shí)間內(nèi)完成;

由于突發(fā)寫長(zhǎng)度為160,所以160個(gè)時(shí)鐘寫160個(gè)數(shù)據(jù);

由于讀速度為10個(gè)時(shí)鐘讀8個(gè)數(shù)據(jù),因此一個(gè)數(shù)據(jù)需要10/8個(gè)時(shí)鐘;

所以160個(gè)時(shí)鐘讀了160*8/10 = 128個(gè)數(shù)據(jù);

所以FIFO的最小深度為160-128=32.

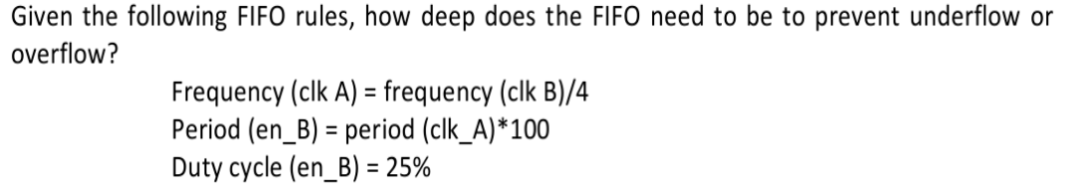

9.8 條件拐彎抹角的給出,需要自己提取關(guān)鍵信息

假如clkA = 25MHz,則CLKB = 100MHz;

TA= 40ns, TB = 10ns;

en_B = 100*40 = 4000ns;占空比為1/4;

我們認(rèn)為B為寫時(shí)鐘,寫使能時(shí)間為4000/4 = 1000ns,則突發(fā)寫長(zhǎng)度為1000/10 = 100個(gè)數(shù)據(jù);

在1000ns內(nèi)讀出數(shù)據(jù)為1000/40 = 25個(gè)數(shù)據(jù),所以FIFO最小深度為100 - 25 = 75

9.9 其它情況

輸入時(shí)鐘頻率煒250MHz,輸入數(shù)據(jù)率8Gbps,輸出的時(shí)鐘頻率200MHz,輸出的數(shù)據(jù)率為5Gbps,單位時(shí)間內(nèi)輸入的數(shù)據(jù)總量為4Gb,在保證數(shù)據(jù)不丟失的情況下,最少需要多大的緩沖空間,并給出分析步驟。

解析:解答1,不考慮兩個(gè)包之間的背靠背的情況

4Gb/8Gbps * 5Gbps = 2.5Gb,因此緩沖空間=4Gb-2.5Gb = 1.5Gb;

解答2:考慮背靠背的情況

突發(fā)長(zhǎng)度=8G, 寫應(yīng)該是0440的情況,讀用最慢的情況,2.5, 2.5,0.5, 2.5,因此FIFO= 8-3 = 5G

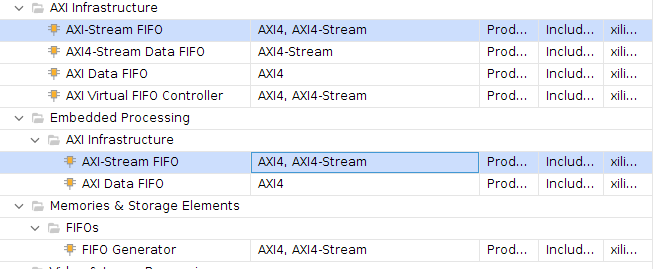

9. Vivado FIFO IP核使用

在IP Catalog中搜索FIFO,會(huì)出現(xiàn)各種各樣的FIFO,一般選擇FIFO generator。

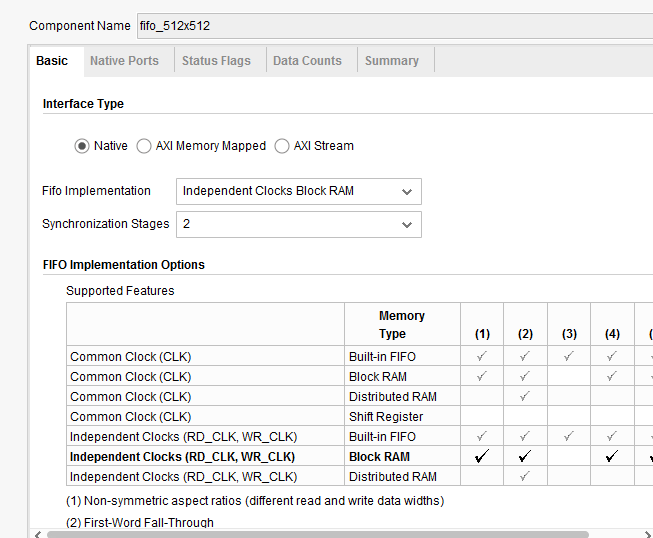

點(diǎn)擊IP之后,會(huì)出現(xiàn)FIFO配置的一些選項(xiàng),包括Basic Native ports, flag等

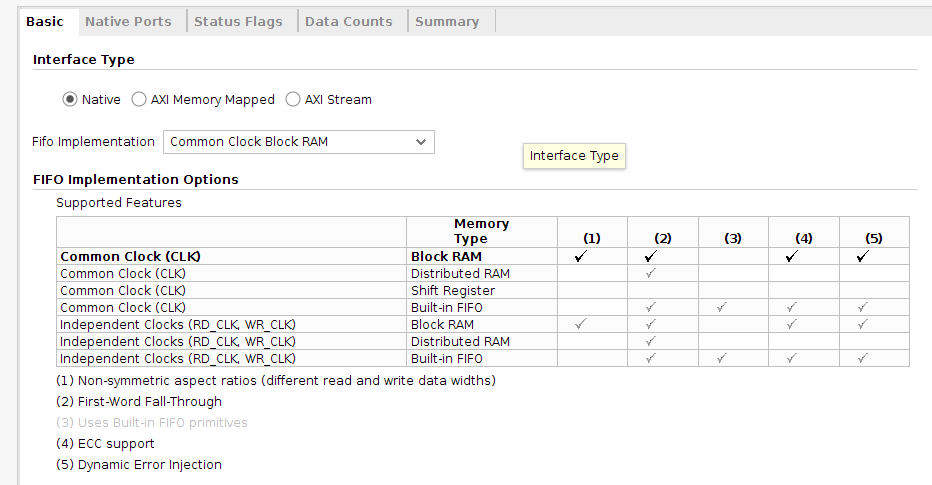

在Basic中我們可以控制FIFO的接口形式和FIFO的類型

FIFO 的接口分為兩類,一類是 Native 接口,這類接口使用比較簡(jiǎn)單,另一類是 AXI 協(xié)議接口,這類協(xié)議口線比較多,操作相對(duì)復(fù)雜。

FIFO 的類型主要區(qū)別:1.讀寫是否使用一個(gè)時(shí)鐘 2.使用何種硬件資源

其中區(qū)別1主要是通過common clk和 independent clk來確定,也就是同步FIFO和異步FIFO

區(qū)別2硬件資源:分為3種。BRAM:即塊RAM資源,這是FPGA內(nèi)嵌的一種重要的專用RAM資源,可以在讀寫兩端使用不同的數(shù)據(jù)寬度,可以使用 ECC (一種數(shù)據(jù)校驗(yàn)特性),支持 First-World Fall Through ,以及支持動(dòng)態(tài)錯(cuò)誤注入。;分布式RAM:Distributed RAM,即將FPGA中的LUT用作RAM,僅支持 First-World Fall Through 功能;專用FIFO,專用FIFO會(huì)提供很小的延遲。BRAM 是一種比較重要的資源,如果設(shè)計(jì)的 FIFO 對(duì)延時(shí)不敏感,可以使用分布式的 RAM 以節(jié)約 BRAM 資源。

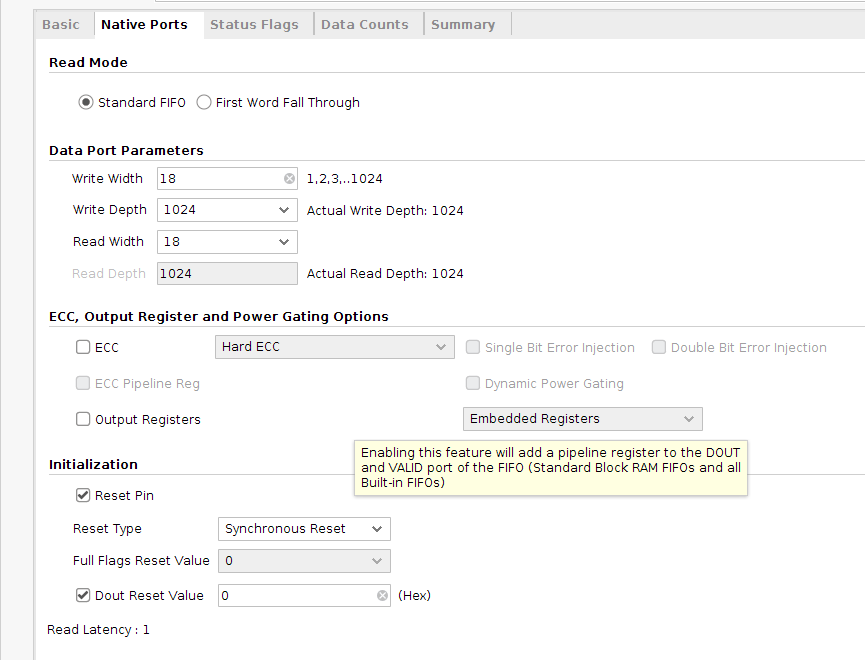

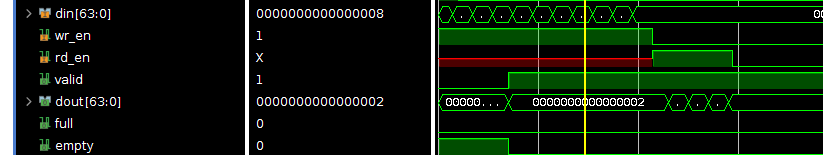

Stand FIFO 和 First Word Fall Through的區(qū)別

standard FIFO 讀取數(shù)據(jù)時(shí)會(huì)延遲一個(gè)周期,也即會(huì)在使能信號(hào)拉高后延遲一個(gè)周期才有數(shù)據(jù)輸出,而First word fall through會(huì)和使能信號(hào)同時(shí)輸出。造成這種區(qū)別的原因在于FWFT模式下,第一個(gè)寫入的數(shù)據(jù)將從RAM中提前讀出到數(shù)據(jù)線。

FIFO 的復(fù)位使用的高電平復(fù)位,如果設(shè)計(jì)中系統(tǒng)復(fù)位信號(hào)是低電平有效的,那么不要忘記要將系統(tǒng)復(fù)位電平取反后再接入 FIFO 復(fù)位電平。一般我們?cè)谕较到y(tǒng)設(shè)計(jì)中使用異步復(fù)位。

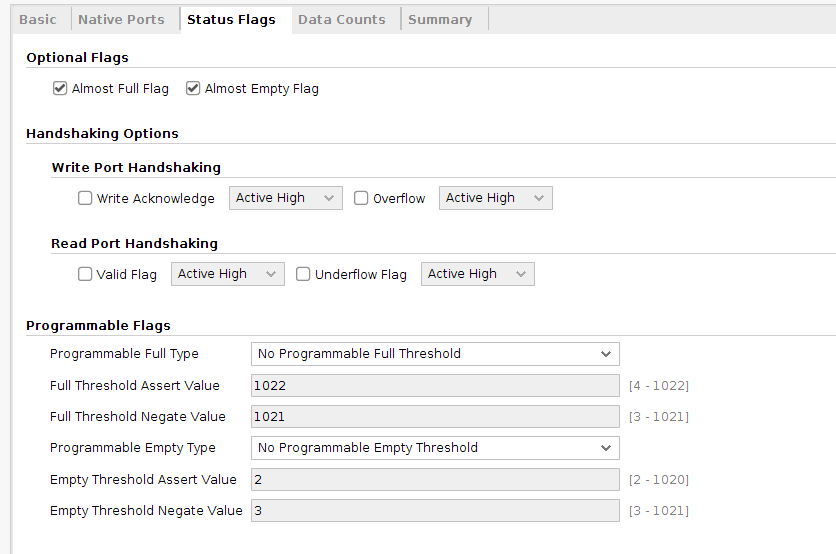

status flag

包括 almost Full/Empty 信號(hào),這兩個(gè)信號(hào),顧名思義,就是在 FIFO 幾乎要滿或者幾乎要空的情況下置起,所謂的“幾乎“就是指還差一個(gè)數(shù)據(jù)滿或者空

這個(gè)頁(yè)面上還提供握手選項(xiàng),但一般我們?cè)诔跫?jí)設(shè)計(jì)中不會(huì)需要 FIFO 具有這種“交互”特性,實(shí)質(zhì)上 AXI 協(xié)議接口也會(huì)提供握手特性。

第四個(gè)頁(yè)面 Data Count,顧名思義就是提供一個(gè)信號(hào)來表示當(dāng)前 FIFO 中的數(shù)據(jù)總數(shù)

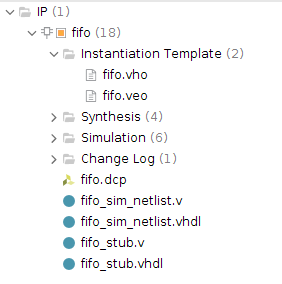

在頂層文件實(shí)例化IP

在IP Source中打開Instation Template目錄下的veo文件,里面就有實(shí)例化的例子

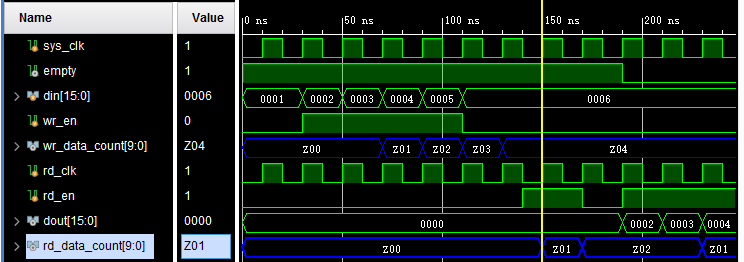

異步FIFO IP的使用

注意同步化synchronization stages

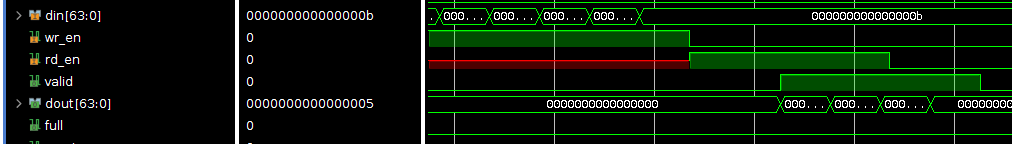

這個(gè)值用于表示FIFOempty拉低的時(shí)間長(zhǎng)度,同時(shí)要注意FIFO的讀一定要有empty控制,并且發(fā)現(xiàn)empty并不是一寫入數(shù)據(jù)就拉低的。

10. FIFO IP使用注意事項(xiàng)

如果讀寫位寬不一樣的情況,比如寫位寬8, 讀位寬32,那么當(dāng)寫入三次是, empty信號(hào)仍然為高電平,也就意味著是讀不出數(shù)據(jù)的。

FIFO的復(fù)位信號(hào)是高電平有效

standard FIFO 和FWFT的區(qū)別就是讀的時(shí)候需要延時(shí)一個(gè)周期和不需要延時(shí)

output register:嵌入式輸出寄存器可用于增加性能并向宏添加流水線寄存器,主要用于改善時(shí)序情況,但是只對(duì)Standard FIFO模式有用,添加output register, 讀延時(shí)會(huì)增加1個(gè)周期

Valid: This signal indicates that valid data is available on the output bus (dout).因此在FWFT模式下,只要FIFO有數(shù)據(jù),valid信號(hào)就會(huì)拉高;而在Standard FIFO模式下,只有在讀信號(hào)使能之后,valid信號(hào)才會(huì)拉高

審核編輯:彭菁

-

電路

+關(guān)注

關(guān)注

172文章

5958瀏覽量

172668 -

數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

9文章

1943瀏覽量

64751 -

AD

+關(guān)注

關(guān)注

27文章

868瀏覽量

150501 -

fifo

+關(guān)注

關(guān)注

3文章

389瀏覽量

43803

原文標(biāo)題:同步FIFO和異步FIFO總結(jié)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于FPGA的異步FIFO的實(shí)現(xiàn)

同步FIFO設(shè)計(jì)詳解及代碼分享

異步FIFO結(jié)構(gòu)及FPGA設(shè)計(jì)

Camera Link接口的異步FIFO設(shè)計(jì)與實(shí)現(xiàn)

異步FIFO結(jié)構(gòu)及FPGA設(shè)計(jì)

異步FIFO的設(shè)計(jì)分析及詳細(xì)代碼

基于FPGA的異步FIFO設(shè)計(jì)方法詳解

同步FIFO之Verilog實(shí)現(xiàn)

異步FIFO之Verilog代碼實(shí)現(xiàn)案例

異步fifo詳解

FIFO使用及其各條件仿真介紹

FIFO設(shè)計(jì)—同步FIFO

FIFO設(shè)計(jì)—異步FIFO

同步FIFO和異步FIFO區(qū)別介紹

同步FIFO和異步FIFO區(qū)別介紹

評(píng)論