現(xiàn)代集成電路芯片中,隨著設(shè)計(jì)規(guī)模的不斷擴(kuò)大。一個(gè)系統(tǒng)中往往含有數(shù)個(gè)時(shí)鐘。多時(shí)鐘帶來(lái)的一個(gè)問(wèn)題就是,如何設(shè)計(jì)異步時(shí)鐘之間的接口電路。異步 FIFO(First In First Out)是解決這個(gè)問(wèn)題的一種簡(jiǎn)便、快捷的解決方案。##異步FIFO的VHDL語(yǔ)言實(shí)現(xiàn)

2014-05-28 10:56:41 3405

3405 大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天我們來(lái)聊一聊基于FPGA的異步FIFO的實(shí)現(xiàn)。 一、FIFO簡(jiǎn)介 FIFO是英文First In First Out 的縮寫(xiě),是一種先進(jìn)先出的數(shù)據(jù)緩存器,它與普通

2018-06-21 11:15:25 6164

6164

異步 FIFO 讀寫(xiě)分別采用相互異步的不同時(shí)鐘。在現(xiàn)代集成電路芯片中,隨著設(shè)計(jì)規(guī)模的不斷擴(kuò)大,一個(gè)系統(tǒng)中往往含有數(shù)個(gè)時(shí)鐘,多時(shí)鐘域帶來(lái)的一個(gè)問(wèn)題就是,如何設(shè)計(jì)異步時(shí)鐘之間的接口電路。異步 FIFO

2020-07-16 17:41:46 1050

1050

FIFO (先入先出, First In First Out )存儲(chǔ)器,在 FPGA 和數(shù)字 IC 設(shè)計(jì)中非常常用。 根據(jù)接入的時(shí)鐘信號(hào),可以分為同步 FIFO 和異步 FIFO 。

2023-06-27 10:24:37 1199

1199

相鄰的格雷碼只有1bit的差異,因此格雷碼常常用于異步fifo設(shè)計(jì)中,保證afifo的讀地址(或?qū)懙刂罚┍粚?xiě)時(shí)鐘(或讀時(shí)鐘)采樣時(shí)最多只有1bit發(fā)生跳變。

2023-11-01 17:37:31 779

779

FIFO的情形。 在FPGA設(shè)計(jì)中,我們會(huì)經(jīng)常用到異步FIFO進(jìn)行跨時(shí)鐘域隔離。作為已經(jīng)非常成熟的設(shè)計(jì),AMD提供

2023-11-02 09:25:01 475

475

勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載89:FPGA片內(nèi)異步FIFO實(shí)例特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD功能概述該工程

2019-05-06 00:31:57

的,這也是它的一大特點(diǎn),通常用來(lái)做數(shù)據(jù)的緩存,或者用來(lái)解決高速異步數(shù)據(jù)的交互,即解決了跨時(shí)鐘域的問(wèn)題。此外,FIFO還有一個(gè)特點(diǎn),就是數(shù)據(jù)被讀出之后就不存在了,不像RAM和ROM一樣,數(shù)據(jù)被讀出后還存在

2023-06-16 17:50:31

異步FIFO介紹異步FIFO的設(shè)計(jì)難點(diǎn)是什么,怎么解決這些難點(diǎn)?

2021-04-08 06:08:24

始條件: 讀寫(xiě)時(shí)鐘都是100MHz,但是讀寫(xiě)時(shí)鐘不同步(存在相位差,也可能存在精度問(wèn)題),FIFO深度為16(最小的深度),在固定時(shí)刻進(jìn)行異步復(fù)位,復(fù)位條件按照Memory User Guide中

2013-12-29 10:32:13

本帖最后由 eehome 于 2013-1-5 09:48 編輯

深入講解異步FIFO的問(wèn)題

2013-01-01 22:26:57

XINLINX FPGA與CY7C68013通訊,異步slave fifo通訊方式,PKTEND信號(hào)的作用是什么,不用的話是不是應(yīng)該拉高 ,另外由于fifo adr用的都公用地址線,時(shí)序上怎么選擇,誰(shuí)能共享一下verilog HDL的例子。

2015-07-10 15:17:28

`Xilinx FPGA入門連載55:FPGA 片內(nèi)異步FIFO實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

`Xilinx FPGA入門連載56:FPGA片內(nèi)異步FIFO實(shí)例之FIFO配置特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1新建

2016-03-09 10:49:56

`Xilinx FPGA入門連載57:FPGA 片內(nèi)異步FIFO實(shí)例之功能仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1

2016-03-16 11:32:11

`Xilinx FPGA入門連載58:FPGA 片內(nèi)異步FIFO實(shí)例之chipscope在線調(diào)試特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-16 12:13:05

最近用到異步FIFO,發(fā)現(xiàn)其中的show-ahead模式很有意思。如下圖,對(duì)FIFO IP核仿真后,可以看到在寫(xiě)請(qǐng)求信號(hào)上升沿兩個(gè)時(shí)鐘周期后數(shù)據(jù)被寫(xiě)入,三個(gè)時(shí)鐘周期后FIFO輸出端就有數(shù)據(jù)輸出,而

2020-02-21 15:50:27

,fifo寫(xiě)滿置1rdreq讀使能信號(hào),高電平有效rdemptyfifo空標(biāo)志位,空時(shí)置1wrclk寫(xiě)時(shí)鐘信號(hào)rdclk讀時(shí)鐘信號(hào)二、配置過(guò)程配置方法參考【鋯石A4 FPGA試用體驗(yàn)】fifo實(shí)驗(yàn)(1

2016-11-05 16:57:51

FIFO是FPGA處理跨時(shí)鐘和數(shù)據(jù)緩存的必要IP,可以這么說(shuō),只要是任意一個(gè)成熟的FPGA涉及,一定會(huì)涉及到FIFO。但是我在使用異步FIFO的時(shí)候,碰見(jiàn)幾個(gè)大坑,這里總結(jié)如下,避免后來(lái)者入坑。

2021-02-04 06:23:41

關(guān)于異步fifo的安全問(wèn)題:1. 雖然異步fifo可以提供多個(gè)握手信號(hào),但真正影響安全性能的就兩個(gè):2. 一個(gè)是讀時(shí)鐘域的空信號(hào)rdrempty3. 另一個(gè)是寫(xiě)時(shí)鐘域的滿信號(hào)wrfull4. 這是

2018-03-05 10:40:33

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載89:FPGA片內(nèi)異步FIFO實(shí)例特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 功能概述

2018-08-28 09:39:16

我想問(wèn)一下什么情況下需要用異步FIFO,什么情況下用同步FIFO?

2014-11-03 17:19:54

FIFO芯片是什么?如何利用FIFO去實(shí)現(xiàn)DSP間雙向并行異步通訊?

2021-06-02 06:08:17

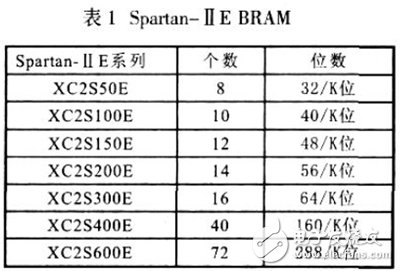

通過(guò)對(duì)FPGA芯片內(nèi)部EBRSRAM的深入研究,提出了一種利用格雷碼對(duì)地址進(jìn)行編碼的異步FIFO設(shè)計(jì)方案。

2021-04-13 06:41:03

結(jié)合高速嵌入式數(shù)據(jù)采集系統(tǒng),提出一種基于CvcloneⅢ FPGA實(shí)現(xiàn)的異步FIFO和鎖相環(huán)(PLL)結(jié)構(gòu)來(lái)實(shí)現(xiàn)高速緩存,該結(jié)構(gòu)可成倍提高數(shù)據(jù)流通速率,增加數(shù)據(jù)采集系統(tǒng)的實(shí)時(shí)性。采用FPGA設(shè)計(jì)高速緩存,能針對(duì)外部硬件系統(tǒng)的改變,通過(guò)修改片內(nèi)程序以應(yīng)用于不同的硬件環(huán)境。

2021-04-30 06:19:52

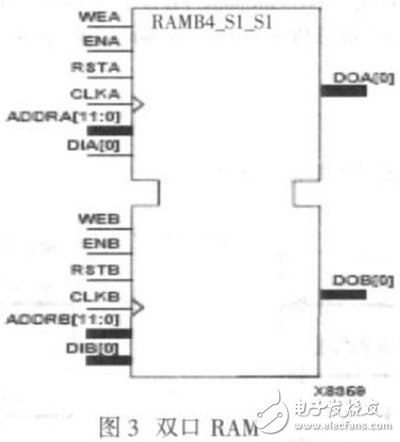

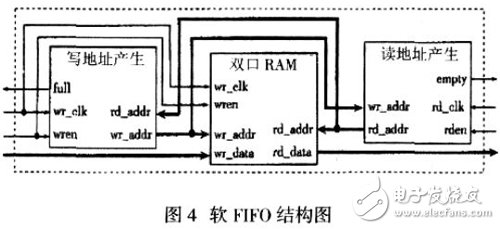

FIFO的基本結(jié)構(gòu)和工作原理異步FIFO設(shè)計(jì)中的問(wèn)題與解決辦法FPGA內(nèi)部軟異步FIFO設(shè)計(jì)

2021-04-08 07:07:45

各位大神: 異步FIFO的空 滿信號(hào)為什么都是高?描述如下:always @(posedge DFIFO_clk or negedge rst_n )beginif(!rst_n)beginWRITE_req

2015-07-01 01:51:58

/cd54hc40105.pdf現(xiàn)在fpga中的所有FIFO都需要連續(xù)時(shí)鐘和一個(gè)使能脈沖。舊的異步FIFO過(guò)去沒(méi)有時(shí)鐘和啟用,只是一個(gè)時(shí)鐘。在寫(xiě)時(shí)鐘的有效邊沿,寫(xiě)入數(shù)據(jù),在讀時(shí)鐘的有效邊沿讀出數(shù)據(jù)。這意味著時(shí)鐘不一定

2019-04-23 13:44:46

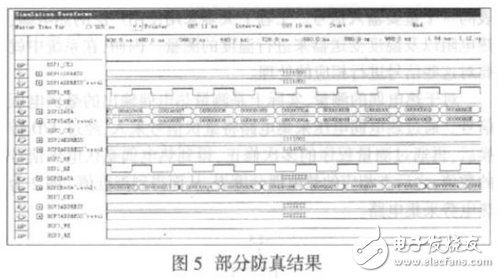

本文討論了在ASIC設(shè)計(jì)中數(shù)據(jù)在不同時(shí)鐘之間傳遞數(shù)據(jù)所產(chǎn)生的亞穩(wěn)態(tài)問(wèn)題,并提出了一種新的異步FIFO的設(shè)計(jì)方法,并用VHDL語(yǔ)言進(jìn)行描述,利用Altera公司的Cyclone系列的EP1C6進(jìn)行硬件實(shí)現(xiàn),該電路軟件仿真和硬件實(shí)現(xiàn)已經(jīng)通過(guò)驗(yàn)證,并應(yīng)用到各種電路中。

2021-04-29 06:54:00

為什么要設(shè)計(jì)一種異步FIFO?異步FIFO的設(shè)計(jì)原理是什么?怎樣去設(shè)計(jì)一種異步FIFO?

2021-06-18 09:20:29

首先介紹異步FIFO 的概念、應(yīng)用及其結(jié)構(gòu),然后分析實(shí)現(xiàn)異步FIFO的難點(diǎn)問(wèn)題及其解決辦法; 在傳統(tǒng)設(shè)計(jì)的基礎(chǔ)上提出一種新穎的電路結(jié)構(gòu)并對(duì)其進(jìn)行綜合仿真和FPGA 實(shí)現(xiàn)。

2009-04-16 09:25:29 46

46 介紹了PCI 9054 接口芯片的性能及數(shù)據(jù)傳輸特點(diǎn),提出了一種基于PCI 9054 外擴(kuò)異步FIFO(先進(jìn)先出)的FPGA(現(xiàn)場(chǎng)可編程門陣列)實(shí)現(xiàn)方法。由于PCI 9054 內(nèi)部FIFO存儲(chǔ)器主要用于數(shù)據(jù)

2010-01-06 15:20:10 44

44 本文提出了基于FPGA 正碼速調(diào)整的設(shè)計(jì)方案,采用格雷碼對(duì)地址編碼的異步FIFO設(shè)計(jì),并利用MAXPLUSⅡ進(jìn)行編譯和仿真。結(jié)果表明,設(shè)計(jì)方法切實(shí)可行。

2010-01-13 15:16:07 23

23 本文主要研究了用FPGA 芯片內(nèi)部的EBRSRAM 來(lái)實(shí)現(xiàn)異步FIFO 設(shè)計(jì)方案,重點(diǎn)闡述了異步FIFO 的標(biāo)志信號(hào)——空/滿狀態(tài)的設(shè)計(jì)思路,并且用VHDL 語(yǔ)言實(shí)現(xiàn),最后進(jìn)行了仿真驗(yàn)證。

2010-01-13 17:11:58 40

40 給出了一個(gè)利用格雷碼對(duì)地址編碼的羿步FIFO 的實(shí)現(xiàn)方法,并給出了VHDL 程序,以解決異步讀寫(xiě)時(shí)鐘引起的問(wèn)題。

2010-07-16 15:15:42 26

26 介紹了異步FIFO在Camera Link接口中的應(yīng)用,將Camera Link接口中的幀有效信號(hào)FVAL和行有效信號(hào)LVAL引入到異步FIFO的設(shè)計(jì)中。分析了FPGA中設(shè)計(jì)異步FIFO的難點(diǎn),解決了異步FIFO設(shè)計(jì)中存在的兩

2010-07-28 16:08:06 32

32 設(shè)計(jì)工程師通常在FPGA上實(shí)現(xiàn)FIFO(先進(jìn)先出寄存器)的時(shí)候,都會(huì)使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其針對(duì)性變差,某些情況下會(huì)變得不方便或者將增加硬

2010-10-27 15:40:30 38

38 摘要:使用FIFO同步源自不同時(shí)鐘域的數(shù)據(jù)是在數(shù)字IC設(shè)計(jì)中經(jīng)常使用的方法,設(shè)計(jì)功能正確的FUFO會(huì)遇到很多問(wèn)題,探討了兩種不同的異步FIFO的設(shè)計(jì)思路。兩種思路

2006-03-24 12:58:33 680

680

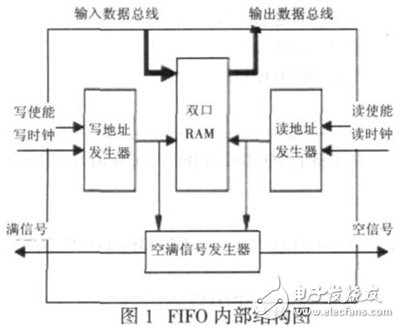

摘要:首先介紹異步FIFO的概念、應(yīng)用及其結(jié)構(gòu),然后分析實(shí)現(xiàn)異步FIFO的難點(diǎn)問(wèn)題及其解決辦法;在傳統(tǒng)設(shè)計(jì)的基礎(chǔ)上提出一種新穎的電路結(jié)構(gòu)并對(duì)其進(jìn)行

2009-06-20 12:46:50 3667

3667

基于FPGA的FIFO設(shè)計(jì)和應(yīng)用

引 言

在利用DSP實(shí)現(xiàn)視頻實(shí)時(shí)跟蹤時(shí),需要進(jìn)行大量高速的圖像采集。而DSP本身自帶的FIFO并不足以支持系統(tǒng)中大量數(shù)據(jù)的暫時(shí)存儲(chǔ)

2009-11-20 11:25:45 2127

2127

高速異步FIFO的設(shè)計(jì)與實(shí)現(xiàn)

引言

現(xiàn)代集成電路芯片中,隨著設(shè)計(jì)規(guī)模的不斷擴(kuò)大.一個(gè)系統(tǒng)中往往含有數(shù)個(gè)時(shí)鐘。多時(shí)鐘帶來(lái)的一個(gè)問(wèn)題就是,如何設(shè)

2010-04-12 15:13:08 2790

2790

FPGA設(shè)計(jì)的高速FIFO電路技術(shù)

本文主要介紹高速FIFO電路在數(shù)據(jù)采集系統(tǒng)中的應(yīng)用,相關(guān)電路主要有高速A/D轉(zhuǎn)換器、FPGA、SDRAM存儲(chǔ)器等。圖1為本方案的結(jié)構(gòu)框圖。在大容量

2010-05-27 09:58:59 2226

2226

為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設(shè)定不當(dāng)帶來(lái)的數(shù)據(jù)不連續(xù)問(wèn)題,結(jié)合LabVIEWFPGA的編程特點(diǎn)和DMA FIFO的工作原理,提出了一種設(shè)定 FIFO 深度的方法。對(duì)FIFO不同深度的實(shí)驗(yàn)表明,采

2011-09-26 13:45:17 6923

6923

文中給出了異步FIFO的實(shí)現(xiàn)代碼和FPGA與DSP的硬件連接電路。經(jīng)驗(yàn)證,利用異步FIFO的方法,在FPGA與DSP通信中的應(yīng)用,具有傳輸速度快、穩(wěn)定可靠、實(shí)現(xiàn)方便的優(yōu)點(diǎn)。

2011-12-12 14:28:22 51

51 為實(shí)現(xiàn)目標(biāo)識(shí)別與跟蹤的應(yīng)用目的 ,在基于 TMS320DM642 的 FIFO 基礎(chǔ)上擴(kuò)展存儲(chǔ)空間 ,提出一種基于

FPGA實(shí)現(xiàn) SDRAM 控制器的方法。分析所用 SDRAM 的特點(diǎn)和工作原理

2015-10-29 14:05:57 2

2 異步FIFO結(jié)構(gòu)及FPGA設(shè)計(jì),解決亞穩(wěn)態(tài)的問(wèn)題

2015-11-10 15:21:37 4

4 異步FIFO在FPGA與DSP通信中的運(yùn)用

2016-05-19 11:17:11 0

0 基于異步FIFO在FPGA與DSP通信中的運(yùn)用

2017-10-19 10:30:56 10

10 介紹了利用CYPRESS公司的FIFO芯片CY7C419實(shí)現(xiàn)DSP間雙向并行異步通訊的方法,該方法簡(jiǎn)單實(shí)用,速度快,特別適用于小數(shù)據(jù)量的數(shù)據(jù)相互傳送。文中給出了CY7C419的引腳功能以及用FIFO

2017-10-25 11:35:25 0

0 代碼和FPGA與DSP的硬件連接電路。經(jīng)驗(yàn)證,利用異步FIFO的方法,在FPGA與DSP通信中的應(yīng)用,具有傳輸速度快、穩(wěn)定可靠、實(shí)現(xiàn)方便的優(yōu)點(diǎn)。 關(guān)鍵詞 異步FIFO;FPGA與DSP數(shù)據(jù)通信;EMIFA

2017-10-30 11:48:44 1

1 傳輸時(shí)發(fā)生數(shù)據(jù)丟失問(wèn)題得目的,提出采用異步FIFO來(lái)緩存大量導(dǎo)航電文數(shù)據(jù)還有同步器來(lái)同步所傳輸?shù)妮d波控制字和偽碼控制字的方法。通過(guò)采用Altera公司的FIFO內(nèi)核來(lái)進(jìn)行外圍接口信號(hào)和控制邏輯設(shè)計(jì)以及兩級(jí)觸發(fā)器級(jí)聯(lián)來(lái)實(shí)現(xiàn)同步器的試驗(yàn)設(shè)計(jì)方法,得到所設(shè)計(jì)的緩存

2017-11-06 16:35:27 10

10 本文首先對(duì)異步 FIFO 設(shè)計(jì)的重點(diǎn)難點(diǎn)進(jìn)行分析,最后給出詳細(xì)代碼。 一、FIFO簡(jiǎn)單講解 FIFO的本質(zhì)是RAM, 先進(jìn)先出 重要參數(shù):fifo深度(簡(jiǎn)單來(lái)說(shuō)就是需要存多少個(gè)數(shù)據(jù)) fifo

2017-11-15 12:52:41 7993

7993

在現(xiàn)代的集成電路芯片中,隨著設(shè)計(jì)規(guī)模的不斷擴(kuò)大,一個(gè)系統(tǒng)中往往含有數(shù)個(gè)時(shí)鐘。多時(shí)鐘域帶來(lái)的一個(gè)問(wèn)題就是,如何設(shè)計(jì)異步時(shí)鐘之間的接口電路。異步FIFO(Firstln F irsto ut)是解決這個(gè)

2018-02-07 14:22:54 0

0 異步FIFO(Fist-In-First-Out)是一種先入先出的數(shù)據(jù)緩沖器[1]。由于可以很好地解決跨時(shí)鐘域問(wèn)題和不同模塊之間的速度匹配問(wèn)題,而被廣泛應(yīng)用于全局異步局部同步[2](Globally

2018-06-19 15:34:00 2870

2870

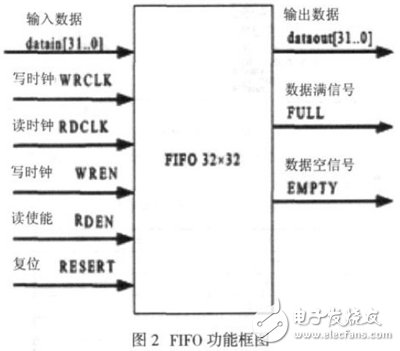

異步FIFO廣泛應(yīng)用于計(jì)算機(jī)網(wǎng)絡(luò)工業(yè)中進(jìn)行異步數(shù)據(jù)傳送,這里的異步是指發(fā)送用一種速率而接收用另一速率,因此異步FIFO有兩個(gè)不同的時(shí)鐘,一個(gè)為讀同步時(shí)鐘,一個(gè)為寫(xiě)同步時(shí)鐘。

2019-06-11 08:00:00 2788

2788

設(shè)計(jì)工程師通常在FPGA上實(shí)現(xiàn)FIFO(先進(jìn)先出寄存器)的時(shí)候,都會(huì)使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其針對(duì)性變差,某些情況下會(huì)變得不方便或者將增加硬件成本。此時(shí),需要進(jìn)行自行

2018-11-28 08:10:00 6709

6709

一般而言,處理跨時(shí)鐘域的方法有這么幾種(大家在網(wǎng)上也都能找到資料,這些資料大都來(lái)自幾篇經(jīng)典的論文,中文方面的資料大都是翻譯過(guò)著理解這幾篇論文而來(lái)):少量的數(shù)據(jù)用邊沿檢測(cè)電路,或者脈沖檢測(cè)電路,或者電平檢測(cè)電路,或者兩級(jí)觸發(fā)器;比較多的數(shù)據(jù)時(shí)用異步FIFO。

2018-09-10 10:06:00 12125

12125

為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設(shè)定不當(dāng)帶來(lái)的數(shù)據(jù)不連續(xù)問(wèn)題,結(jié)合LabVIEWFPGA的編程特點(diǎn)和DMA FIFO的工作原理,提出了一種設(shè)定FIFO深度的方法。對(duì)FIFO

2019-01-04 14:25:07 4225

4225

根據(jù)FIFO工作的時(shí)鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時(shí)鐘和寫(xiě)時(shí)鐘為同一個(gè)時(shí)鐘。在時(shí)鐘沿來(lái)臨時(shí)同時(shí)發(fā)生讀寫(xiě)操作。異步FIFO是指讀寫(xiě)時(shí)鐘不一致,讀寫(xiě)時(shí)鐘是互相獨(dú)立的。

2019-11-29 07:08:00 1609

1609 異步FIFO存儲(chǔ)器是一種在數(shù)據(jù)交互系統(tǒng)中得到廣泛應(yīng)用的先進(jìn)先出邏輯器件,具有容納異步信號(hào)的頻率(或相位差異)的特點(diǎn)。使用異步FIFO可以在兩個(gè)不同時(shí)鐘系統(tǒng)之間快速而方便地傳輸實(shí)時(shí)數(shù)據(jù)。因此,異步FIFO被廣泛應(yīng)用于實(shí)時(shí)數(shù)據(jù)傳輸、網(wǎng)絡(luò)接口、圖像處理等方面。

2020-01-29 16:54:00 718

718

FPGA電路FIFO設(shè)計(jì)的源代碼

2020-07-08 17:34:37 15

15 問(wèn)題的有效方法。異步FIFO是一種在電子系統(tǒng)中得到廣泛應(yīng)用的器件,多數(shù)情況下它都是以一個(gè)獨(dú)立芯片的方式在系統(tǒng)中應(yīng)用。本文介紹一種充分利用FPGA內(nèi)部的RAM資源,在FPGA內(nèi)部實(shí)現(xiàn)異步FIFO模塊的設(shè)計(jì)方法。這種異步FIFO比外部 FIFO 芯片更能提高系統(tǒng)的穩(wěn)定性。

2020-07-21 17:09:36 1326

1326

。本文提出了一種用Xilinx公司的FPGA芯片實(shí)現(xiàn)異步HFO的設(shè)計(jì)方案,重點(diǎn)強(qiáng)調(diào)了設(shè)計(jì)有效、可靠的握手信號(hào)EMPTY與FULL的方法,并給出了其VERILOG語(yǔ)言實(shí)現(xiàn)的仿真圖。

2021-01-15 15:27:00 9

9 提出了一種節(jié)能并可升級(jí)的異步FIFO的FPGA實(shí)現(xiàn)。此系統(tǒng)結(jié)構(gòu)利用FPGA內(nèi)自身的資源控制時(shí)鐘的暫停與恢復(fù),實(shí)現(xiàn)了高能效、高工作頻率的數(shù)據(jù)傳輸。該系統(tǒng)在Xilinx的VC4VSX55芯片中實(shí)現(xiàn),實(shí)際

2021-02-02 15:15:00 16

16 FIFO是FPGA處理跨時(shí)鐘和數(shù)據(jù)緩存的必要IP,可以這么說(shuō),只要是任意一個(gè)成熟的FPGA涉及,一定會(huì)涉及到FIFO。但是我在使用異步FIFO的時(shí)候,碰見(jiàn)幾個(gè)大坑,這里總結(jié)如下,避免后來(lái)者入坑。

2021-03-12 06:01:34 12

12 一:fifo是什么 FIFO的完整英文拼寫(xiě)為FirstIn First Out,即先進(jìn)先出。FPGA或者ASIC中使用到的FIFO一般指的是對(duì)數(shù)據(jù)的存儲(chǔ)具有先進(jìn)先出特性的一個(gè)存儲(chǔ)器,常被用于數(shù)據(jù)

2021-03-12 16:30:48 2796

2796

1.定義 FIFO是英文First In First Out 的縮寫(xiě),是一種先進(jìn)先出的數(shù)據(jù)緩存器,他與普通存儲(chǔ)器的區(qū)別是沒(méi)有外部讀寫(xiě)地址線,這樣使用起來(lái)非常簡(jiǎn)單,但缺點(diǎn)就是只能順序?qū)懭霐?shù)據(jù),順序

2021-04-09 17:31:42 4697

4697

異步FIFO通過(guò)比較讀寫(xiě)地址進(jìn)行滿空判斷,但是讀寫(xiě)地址屬于不同的時(shí)鐘域,所以在比較之前需要先將讀寫(xiě)地址進(jìn)行同步處理,將寫(xiě)地址同步到讀時(shí)鐘域再和讀地址比較進(jìn)行FIFO空狀態(tài)判斷(同步后的寫(xiě)地址一定

2021-08-04 14:05:21 3794

3794 FIFO是在FPGA設(shè)計(jì)中使用的非常頻繁,也是影響FPGA設(shè)計(jì)代碼穩(wěn)定性以及效率等得關(guān)鍵因素。在數(shù)據(jù)連續(xù)讀取時(shí),為了能不間斷的讀出數(shù)據(jù)而又不導(dǎo)致FIFO為空后還錯(cuò)誤的讀出數(shù)據(jù)。可以將FIFO

2021-09-09 11:15:00 6293

6293 一、概述 在大規(guī)模ASIC或FPGA設(shè)計(jì)中,多時(shí)鐘系統(tǒng)往往是不可避免的,這樣就產(chǎn)生了不同時(shí)鐘域數(shù)據(jù)傳輸?shù)膯?wèn)題,其中一個(gè)比較好的解決方案就是使用異步FIFO來(lái)作不同時(shí)鐘域數(shù)據(jù)傳輸?shù)木彌_區(qū),這樣既可以

2021-09-30 09:57:40 1533

1533

跨時(shí)鐘域處理 & 亞穩(wěn)態(tài)處理&異步FIFO1.FIFO概述FIFO: 一、先入先出隊(duì)列(First Input First Output,FIFO)這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)

2021-12-17 18:29:31 10

10 FIFO是FPGA項(xiàng)目中使用最多的IP核,一個(gè)項(xiàng)目使用幾個(gè),甚至是幾十個(gè)FIFO都是很正常的。通常情況下,每個(gè)FIFO的參數(shù),特別是位寬和深度,是不同的。

2022-03-08 11:06:12 4520

4520

在大規(guī)模ASIC或FPGA設(shè)計(jì)中,多時(shí)鐘系統(tǒng)往往是不可避免的,這樣就產(chǎn)生了不同時(shí)鐘域數(shù)據(jù)傳輸?shù)膯?wèn)題,其中一個(gè)比較好的解決方案就是使用異步FIFO來(lái)作不同時(shí)鐘域數(shù)據(jù)傳輸?shù)木彌_區(qū),這樣既可以使相異時(shí)鐘域數(shù)據(jù)傳輸?shù)臅r(shí)序要求變得寬松,也提高了它們之間的傳輸效率。此文內(nèi)容就是闡述異步FIFO的設(shè)計(jì)。

2022-03-09 16:29:18 2309

2309 在FPGA中對(duì)圖像的一行數(shù)據(jù)進(jìn)行緩存時(shí),可以采用FIFO這一結(jié)構(gòu),如上圖所示,新一行圖像數(shù)據(jù)流入到FIFO1中,FIFO1中會(huì)對(duì)圖像數(shù)據(jù)進(jìn)行緩存,當(dāng)FIFO1中緩存有一行圖像數(shù)據(jù)時(shí),在下一行圖像數(shù)據(jù)來(lái)臨的時(shí)候,將FIFO1中緩存的圖像數(shù)據(jù)讀出,并傳遞給下一個(gè)FIFO

2022-05-10 09:59:29 3056

3056 FIFO的分類根均FIFO工作的時(shí)鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時(shí)鐘和寫(xiě)時(shí)鐘為同一個(gè)時(shí)鐘。在時(shí)鐘沿來(lái)臨時(shí)同時(shí)發(fā)生讀寫(xiě)操作。異步FIFO是指讀寫(xiě)時(shí)鐘不一致,讀寫(xiě)時(shí)鐘是互相獨(dú)立的。

2022-11-01 09:57:08 1315

1315 同步FIFO的意思是說(shuō)FIFO的讀寫(xiě)時(shí)鐘是同一個(gè)時(shí)鐘,不同于異步FIFO,異步FIFO的讀寫(xiě)時(shí)鐘是完全異步的。同步FIFO的對(duì)外接口包括時(shí)鐘,清零,讀請(qǐng)求,寫(xiě)請(qǐng)求,數(shù)據(jù)輸入總線,數(shù)據(jù)輸出總線,空以及滿信號(hào)。

2022-11-01 09:58:16 1189

1189 FIFO 是我們?cè)O(shè)計(jì)中常用的工具,因?yàn)樗鼈兪刮覀兡軌蛟谶M(jìn)行信號(hào)和圖像處理時(shí)緩沖數(shù)據(jù)。我們還使用異步FIFO來(lái)處理數(shù)據(jù)總線的時(shí)鐘域交叉問(wèn)題。

2022-11-04 09:14:11 3214

3214 位寬變換:對(duì)于不同寬度的數(shù)據(jù)接口也可以用FIFO,例如單片機(jī)位8位數(shù)據(jù)輸出,而DSP可能是16位數(shù)據(jù)輸入,在單片機(jī)與DSP連接時(shí)就可以使用FIFO來(lái)達(dá)到數(shù)據(jù)匹配的目的。

2022-11-09 20:00:03 1253

1253 異步fifo詳解 一. 什么是異步FIFO FIFO即First in First out的英文簡(jiǎn)稱,是一種先進(jìn)先出的數(shù)據(jù)緩存器,與普通存儲(chǔ)器的區(qū)別在于沒(méi)有外部讀寫(xiě)的地址線,缺點(diǎn)是只能順序的讀取

2022-12-12 14:17:41 2790

2790 FIFO用于為匹配讀寫(xiě)速度而設(shè)置的數(shù)據(jù)緩沖buffer,當(dāng)讀寫(xiě)時(shí)鐘異步時(shí),就是異步FIFO。多bit的數(shù)據(jù)信號(hào),并不是直接從寫(xiě)時(shí)鐘域同步到讀時(shí)鐘域的。

2023-01-01 16:48:00 941

941 FIFO是異步數(shù)據(jù)傳輸時(shí)常用的存儲(chǔ)器,多bit數(shù)據(jù)異步傳輸時(shí),無(wú)論是從快時(shí)鐘域到慢時(shí)鐘域,還是從慢時(shí)鐘域到快時(shí)鐘域,都可以使用FIFO處理。

2023-05-26 16:12:49 978

978

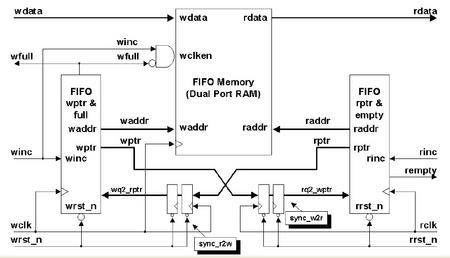

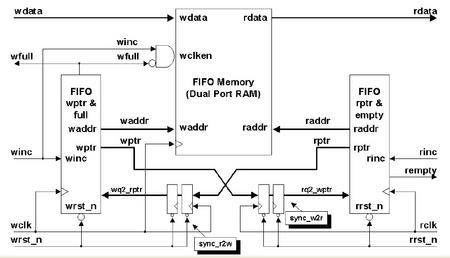

異步FIFO主要由五部分組成:寫(xiě)控制端、讀控制端、FIFO Memory和兩個(gè)時(shí)鐘同步端

2023-05-26 16:17:20 911

911

在ASIC設(shè)計(jì)或者FPGA設(shè)計(jì)中,我們常常使用異步fifo(first in first out)(下文簡(jiǎn)稱為afifo)進(jìn)行數(shù)據(jù)流的跨時(shí)鐘,可以說(shuō)沒(méi)使用過(guò)afifo的Designer,其設(shè)計(jì)經(jīng)歷是不完整的。廢話不多說(shuō),直接上接口信號(hào)說(shuō)明。

2023-07-31 11:10:19 1220

1220

很多人在面試時(shí)被問(wèn)到為什么異步FIFO中需要用到格雷碼,可能大部分的答案是格雷碼可以消除亞穩(wěn)態(tài)。這種回答比較模糊,今天我們就針對(duì)這個(gè)來(lái)深入探討一下。

2023-08-26 14:20:25 575

575

異步FIFO包含"讀"和"寫(xiě)“兩個(gè)部分,寫(xiě)操作和讀操作在不同的時(shí)鐘域中執(zhí)行,這意味著Write_Clk和Read_Clk的頻率和相位可以完全獨(dú)立。異步FIFO

2023-09-14 11:21:45 545

545

同步FIFO和異步FIFO的區(qū)別 同步FIFO和異步FIFO各在什么情況下應(yīng)用? 1. 同步FIFO和異步FIFO的區(qū)別 同步FIFO和異步FIFO在處理時(shí)序有明顯的區(qū)別。同步FIFO相對(duì)來(lái)說(shuō)是較為

2023-10-18 15:23:58 790

790 請(qǐng)問(wèn)異步FIFO的溢出操作時(shí)怎么樣判斷的? 異步FIFO是數(shù)據(jù)傳輸?shù)囊环N常用方式,在一些儲(chǔ)存器和計(jì)算機(jī)系統(tǒng)中,常常會(huì)用到異步FIFO。作為一種FIFO,異步FIFO經(jīng)常面臨兩種情況:溢出

2023-10-18 15:28:41 299

299 ? 點(diǎn)擊上方 藍(lán)字 關(guān)注我們 ? 第一節(jié):fifo基礎(chǔ) ? ? 內(nèi)容: 1. 掌握FPGA設(shè)計(jì)中關(guān)于數(shù)據(jù)緩存的使用 2. 掌握FIFO工作原理

2023-11-17 14:00:02 179

179 電子發(fā)燒友網(wǎng)站提供《異步FIFO結(jié)構(gòu)設(shè)計(jì).pdf》資料免費(fèi)下載

2024-02-06 09:06:27 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論