SDIO總線介紹

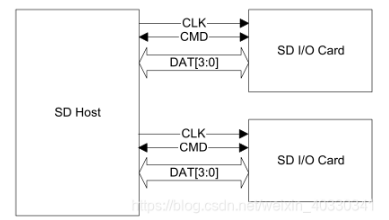

SDIO(Secure Digital lnput and Output),即安全數(shù)字輸入輸出接口。SDIO總線協(xié)議是由SD協(xié)議演化而來,它主要是對SD協(xié)議進行了一些擴展。

SDIO總線主要是為SDIO卡提供一個高速的I/O能力,并伴隨著較低的功耗。SDIO總線不但支持SDIO卡,而且還兼容SD內(nèi)存卡。支持SDIO的設備比如手機和相機不僅能支持SD卡,TF卡,隨著SDIO硬件設備的擴充SDIO總線的外圍能夠支持更多的SDIO設備比如Bluetooth,WIFI,GPS,Camera sensor等,它們的識別過程跟SD卡類似,主要差別是在SD協(xié)議的基礎上做了些擴展。

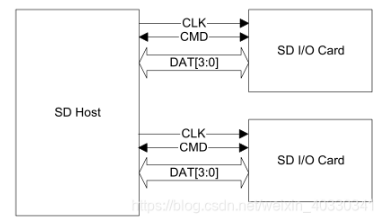

圖1SDIO總線通信原理

國產(chǎn)ARM + FPGA架構(gòu)介紹與優(yōu)勢

近年來,隨著中國新基建、中國制造2025規(guī)劃的持續(xù)推進,單ARM處理器越來越難勝任工業(yè)現(xiàn)場的功能要求,特別是如今能源電力、工業(yè)控制、智慧醫(yī)療等行業(yè),往往更需要ARM + FPGA架構(gòu)的處理器平臺來實現(xiàn)例如多路/高速AD采集、多路網(wǎng)口、多路串口、多路/高速并行DI/DO、高速數(shù)據(jù)并行處理等特定功能,因此ARM + FPGA架構(gòu)處理器平臺愈發(fā)受市場歡迎。

因此,創(chuàng)龍科技一年前正式推出了基于全志T3 +紫光同創(chuàng)Logos處理器設計的ARM + FPGA全國產(chǎn)工業(yè)核心板,國產(chǎn)化率達100%。

全志T3為準車規(guī)級芯片,四核ARM Cortex-A7架構(gòu),主頻高達1.2GHz,支持雙路網(wǎng)口、八路UART、SATA大容量存儲接口,同時支持4路顯示、GPU以及1080P H.264視頻硬件編解碼。另外,創(chuàng)龍科技已在T3平臺適配國產(chǎn)嵌入式系統(tǒng)翼輝SylixOS,真正實現(xiàn)軟硬件國產(chǎn)化。

紫光同創(chuàng)Logos PGL25G/PGL50G FPGA在工業(yè)領域應用廣泛,邏輯資源分別為27072/51360,與國外友商產(chǎn)品pin to pin兼容,主要用于多通道/高速AD采集或接口拓展。因其價格低、質(zhì)量穩(wěn)定、開發(fā)環(huán)境易用等優(yōu)點,受到工業(yè)用戶的廣泛好評。尤其是開發(fā)環(huán)境,最快3天可完成從國外友商產(chǎn)品到紫光同創(chuàng)產(chǎn)品的切換。

國產(chǎn)ARM + FPGA的SDIO通信案例介紹

本章節(jié)主要介紹全志科技T3與紫光同創(chuàng)Logos基于SDIO的ARM + FPGA通信方案,使用的硬件平臺為:創(chuàng)龍科技TLT3F-EVM工業(yè)評估板。最終實測寫速率為5.678MB/s,讀速率為5.744MB/s,誤碼率為0。

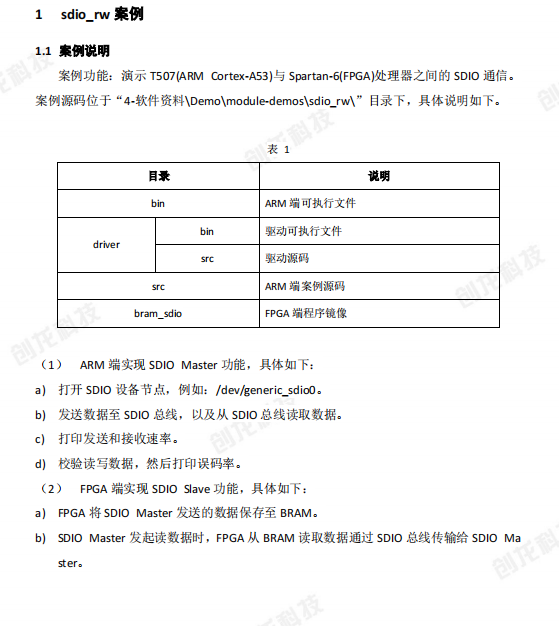

案例功能

該案例實現(xiàn)T3(ARM Cortex-A7)與FPGA的SDIO通信功能。

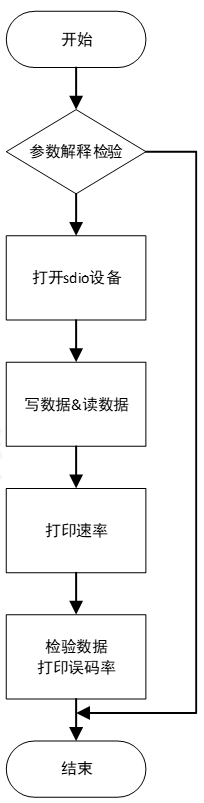

ARM端sdio_test案例實現(xiàn)SDIO Master功能,具體如下:

(1)打開SDIO設備節(jié)點,如:/dev/generic_sdio0;

(2)發(fā)送數(shù)據(jù)至SDIO總線,以及從SDIO總線讀取數(shù)據(jù);

(3)校驗數(shù)據(jù),然后打印讀寫速率、誤碼率。

FPGA端dram_sdio案例實現(xiàn)SDIO Slave功能,具體如下:

(1)FPGA將SDIO Master發(fā)送的數(shù)據(jù)保存至DRAM;

(2)SDIO Master發(fā)起讀數(shù)據(jù)時,F(xiàn)PGA從DRAM讀取數(shù)據(jù),并通過SDIO總線傳輸至SDIO Master。

圖3ARM端程序流程圖

案例演示

評估板上電后,請先固化FPGA案例dram_sdio_xxx.sfc可執(zhí)行程序至FPGA端,F(xiàn)PGA需在ARM驅(qū)動加載前完成初始化。再將ARM端可執(zhí)行文件sdio_test、"driveringeneric_sdio.ko"驅(qū)動拷貝至評估板文件系統(tǒng)任意目錄下。

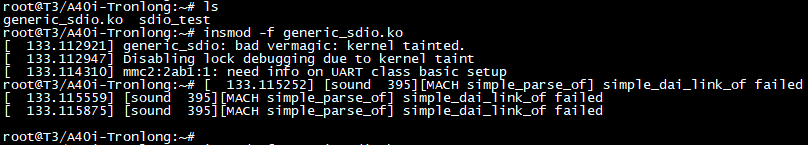

評估板上電啟動,在generic_sdio.ko驅(qū)動所在路徑下,執(zhí)行如下命令加載驅(qū)動。

Target#insmod -f generic_sdio.ko

圖4

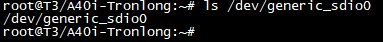

執(zhí)行如下命令,可查看設備節(jié)點。

Target#ls /dev/generic_sdio0

圖5

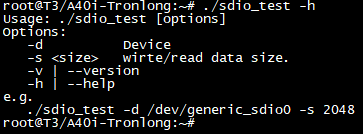

執(zhí)行如下命令,可查詢程序命令參數(shù)。

Target#./sdio_test -h

圖6

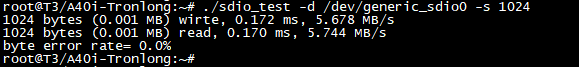

執(zhí)行如下命令,ARM通過SDIO總線寫入隨機數(shù)據(jù)至FPGA DRAM,然后讀出數(shù)據(jù)、進行數(shù)據(jù)校驗,同時打印SDIO總線讀寫速率和誤碼率,如下圖所示。

Target#./sdio_test -d /dev/generic_sdio0 -s 1024

參數(shù)解析:

-d:設備節(jié)點路徑;

-s:設置傳輸數(shù)據(jù)大小,單位為Byte。

圖7

本次測試SDIO總線通信時鐘頻率為最高50MHz,則理論通信速率為:(50 x 4 / 8)MB/s = 25MB/s。從上圖可知,則可以清晰看到實測速率結(jié)果。

備注:實測速率相比理論速率偏低,與ARM端驅(qū)動和FPGA端邏輯實現(xiàn)、IP核配置有關。

-

處理器

+關注

關注

68文章

19549瀏覽量

231881 -

FPGA

+關注

關注

1637文章

21842瀏覽量

608541 -

DRAM

+關注

關注

40文章

2337瀏覽量

184304 -

SD卡

+關注

關注

2文章

568瀏覽量

64384 -

UART接口

+關注

關注

0文章

124瀏覽量

15444

原文標題:技術分享!國產(chǎn)ARM + FPGA的SDIO通信開發(fā)介紹!

文章出處:【微信號:Tronlong創(chuàng)龍科技,微信公眾號:Tronlong創(chuàng)龍科技】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

【國產(chǎn)FPGA+OMAPL138開發(fā)板體驗】(原創(chuàng))3.手把手玩轉(zhuǎn)ARM與FPGA通信

【國產(chǎn)FPGA+OMAPL138開發(fā)板體驗】(原創(chuàng))4.FPGA的GPMC通信(ARM)EDMA

使用國產(chǎn)的FPGA開發(fā),需要哪些準備

國產(chǎn)RK3568J基于FSPI的ARM+FPGA通信方案分享

實測52.4MB/s!全國產(chǎn)ARM+FPGA的CSI通信案例分享!

3568F-ARM+FPGA通信案例開發(fā)手冊

國產(chǎn)ARM+FPGA架構(gòu)在“能源電力”中的典型應用詳解

【新品體驗】國產(chǎn)FPGA+OMAPL138開發(fā)板免費試用

ESP32 SDIO 使用教程

基于國產(chǎn)ARM與低成本FPGA高速通信的3種方案

一文告訴你全國產(chǎn)的ARM+FPGA核心板憑什么那么強!

技術分享!國產(chǎn)ARM + FPGA的SDIO通信開發(fā)介紹!

技術分享!國產(chǎn)ARM + FPGA的SDIO通信開發(fā)介紹!

國產(chǎn)ARM + FPGA的SDIO通信開發(fā)介紹!

國產(chǎn)ARM + FPGA的SDIO通信開發(fā)介紹!

評論