臺積電推出更先進封裝平臺,晶體管可增加到1萬億個。

在ISSCC 2024上,臺積電正式公布了其新的先進封裝平臺,該技術有望將晶體管數量從目前的1000億提升到1萬億。

臺積電業務開發資深副總裁張曉強(Kevin Zhang)在國際固態電路大會ISSCC 2024 介紹公司最新技術,并分享未來技術演進、對于先進制程展望,以及各領域中所需要的最新半導體技術。

Kevin Zhang指出,隨著ChatGPT、Wi-Fi 7 出現,已經需要大量半導體,我們也進入半導體高速成長期。在車用部分,汽車產業正經歷一場革命,許多人說新的汽車將是定義軟件,但他覺得是“硅定義汽車(silicon-defined automotive)”,因為軟件需要在硅上運作,推動未來的自動駕駛能力。

本文整理了Kevin Zhang的演講內容。

從高性能計算、AI機器學習到通信,從交通到醫療保健,凡是目之所及都與半導體相關。Kevin Zhang最開始從商業的角度談了半導體。

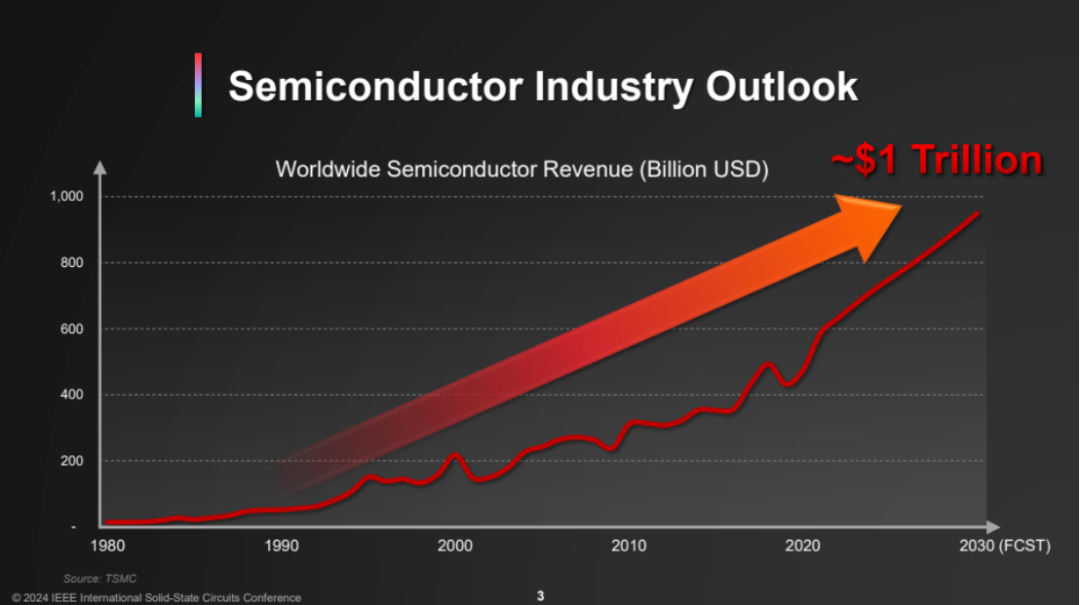

正如我們今天所見,全球半導體收入大約在五千億美元。業內都認為,到了本十年末,這個數字將翻一番。但Kevin Zhang在這里加上一個限定詞:隨著人工智能的激增。一萬億數字并不能反映出Open AI的Sam Altman計劃投資半導體的數萬億。這個不算最新的預測。AMD的Lisa SU認為,到2028年,僅人工智能市場就能夠達到4000億美元。

Kevin Zhang說到:“沒有人能夠確切的知道人工智能將如何塑造這條增長曲線。只有一件事能夠確定,我們正在進入半導體的加速增長期。”

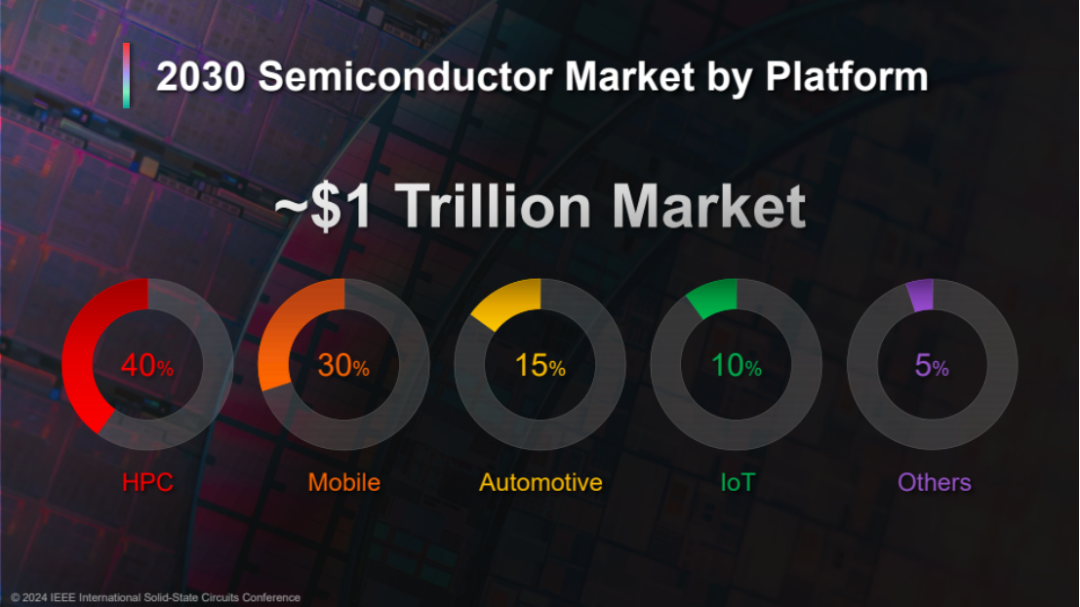

如果更深入的了解這個潛在的萬億市場的高點,高性能計算將占據40%的份額,超過移動設備成為第一大領域。在幾年前,如果說到與物聯網結合,那是不可想象的。因為傳統觀點始終認為,邊緣設備是用戶消費數據的地方,但是到了現在有了AI。

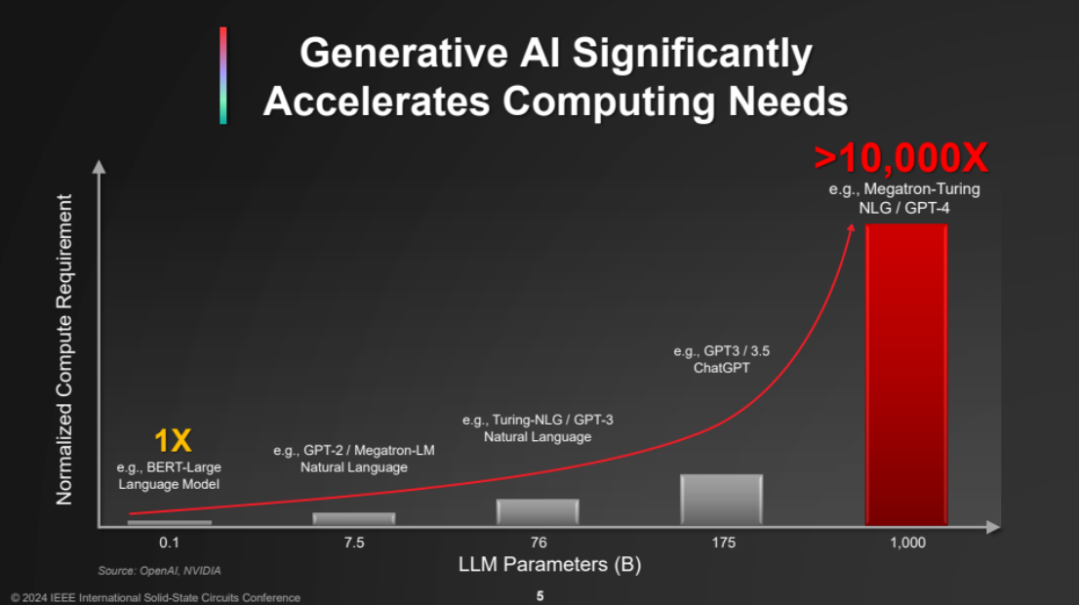

當談到AI,那不可避免的需要談到Chat GPT。自從一年半以前Chat GPT推出以來,我們已經看到半導體行業的格局正在發生變化。

看圖上陡峭的曲線,這背后其實是對算力的永不滿足。因此,英偉達首席執行官黃仁勛曾說到:“Chat GPT是人工智能的iphone 時刻。”我們可以使用不同的方式描述AI,但確定的是,AI需要大量先進的半導體,這個需求數超越人們的想象。

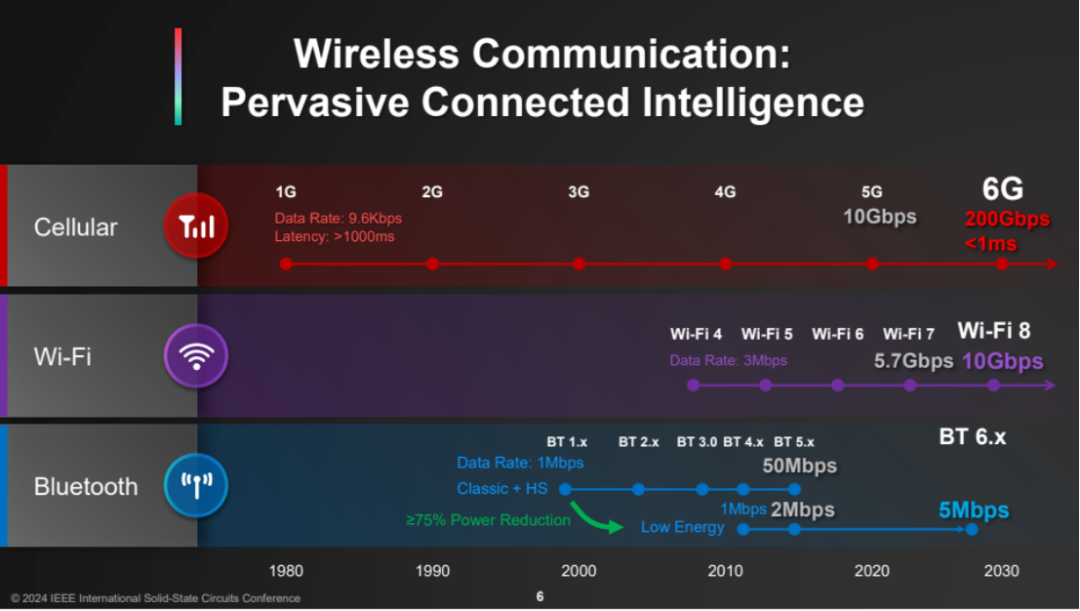

之后,Kevin Zhang也談到了無線通信。通信在生活中非常的重要,上圖展示了三種通信技術:蜂窩、WI-FI、藍牙。正如所見,所有高級標準都需要更高的數據速率,更先進的信號處理,這將繼續推動加速采用先進的技術,例如Wi-Fi 7。臺積電今年也正在著手生產Wi-Fi 7的產品。從一開始,Wi-Fi 7的產品就必須采用7nm技術才能夠達到功耗性能目標。

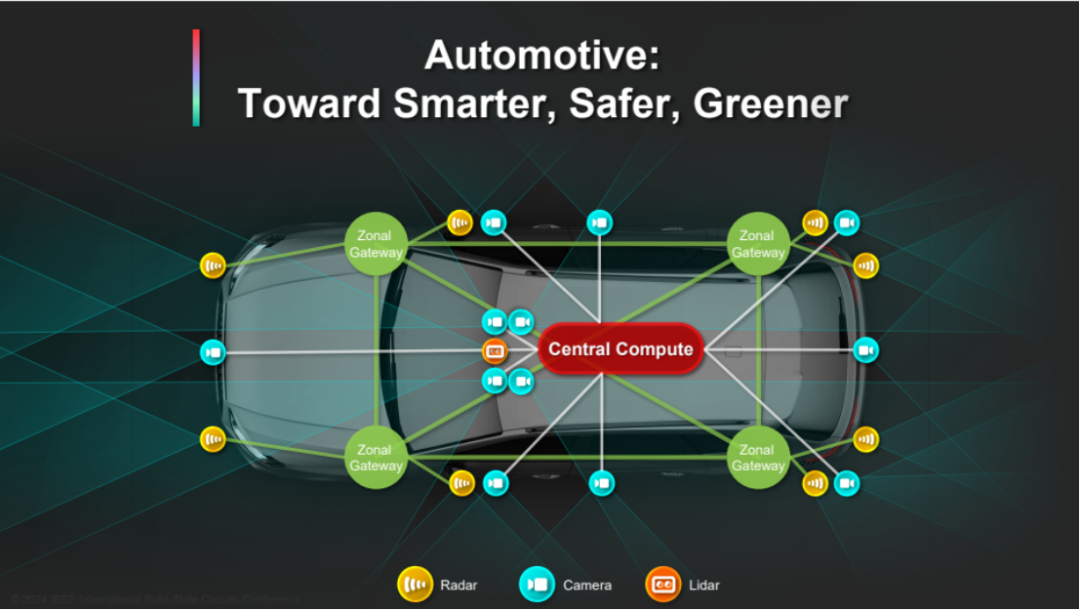

在汽車領域,汽車正在經歷一場根本性的革命。很多人認為新汽車將是軟件定義汽車,但Kevin Zhang認為更好的術語是:“硅定義汽車(silicon-defined automotive)”。因為所有的軟件都必須在硅上運行。無論是傳感器、通信、網絡都在推動最先進的半導體自主的向前發展技術。

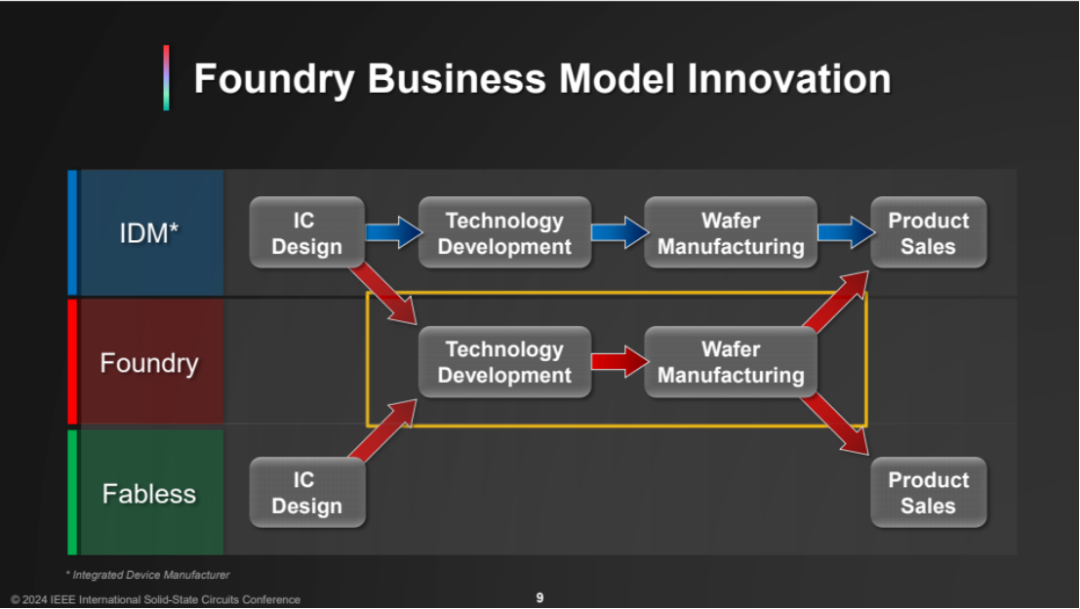

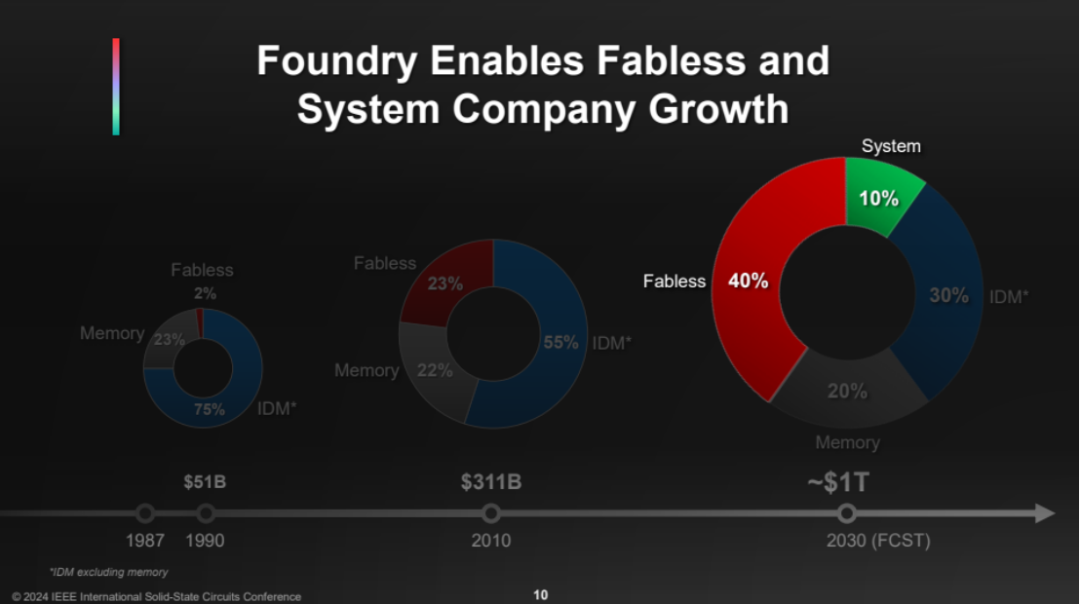

在談技術前,Kevin Zhang還花費了時間談到了半導體行業業務的創新——純代工業務的出現,這項創新從根本上改變了半導體行業的格局。通過從傳統的IDM模式中剔除非常復雜、成本高昂的晶圓制造,讓無晶圓企業能夠專注產品開發和創新。與代工廠的合作,共同極大的加速了行業的創新。

由于代工廠的引入,出現了很多新玩家。快進到2030年,如上圖所見,超過50%的半導體收入由優秀的無晶圓公司、系統公司或云公司貢獻。這些都是因為業務創新、代工廠的出現。

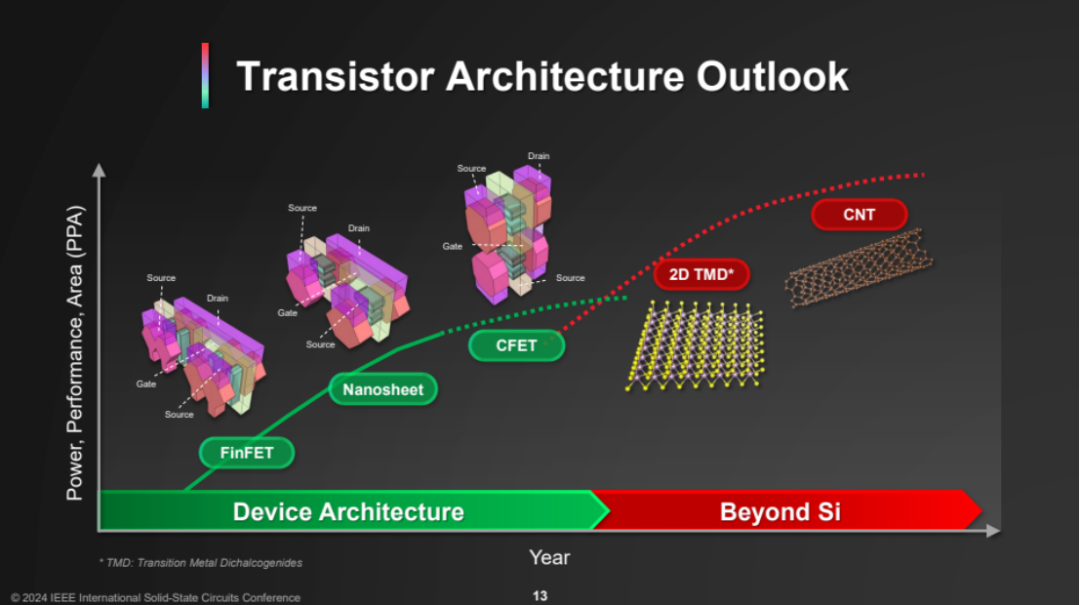

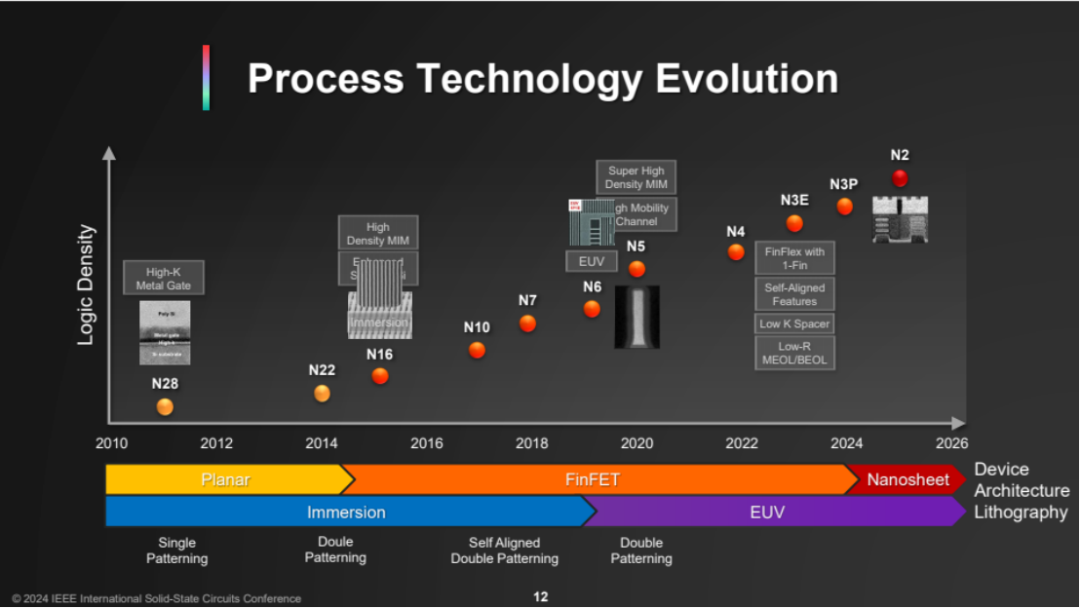

之后,Kevin Zhang開始談到了本次演講的重點:先進技術。Kevin Zhang認為,晶體管仍然是創新的核心,即硅創新(silicon innovation)。幾十年來,晶體管經歷了多次重大的演變。如上圖可見,早期的晶體管創新主要集中在圍繞幾何減少,但現在情況不再如此。最近一代,一切都集中在晶體管架構的創新以及新材料的使用上。

比如說,16nm將從平面晶體管轉向FinFET晶體管。今天,臺積電在2nm層面即將推出一種全新的晶體管:Nanosheet。可以極大的改善設備的漏電,提高傳導能力,并且在更低的電壓下更好的工作。這對于高性能計算來說非常重要。

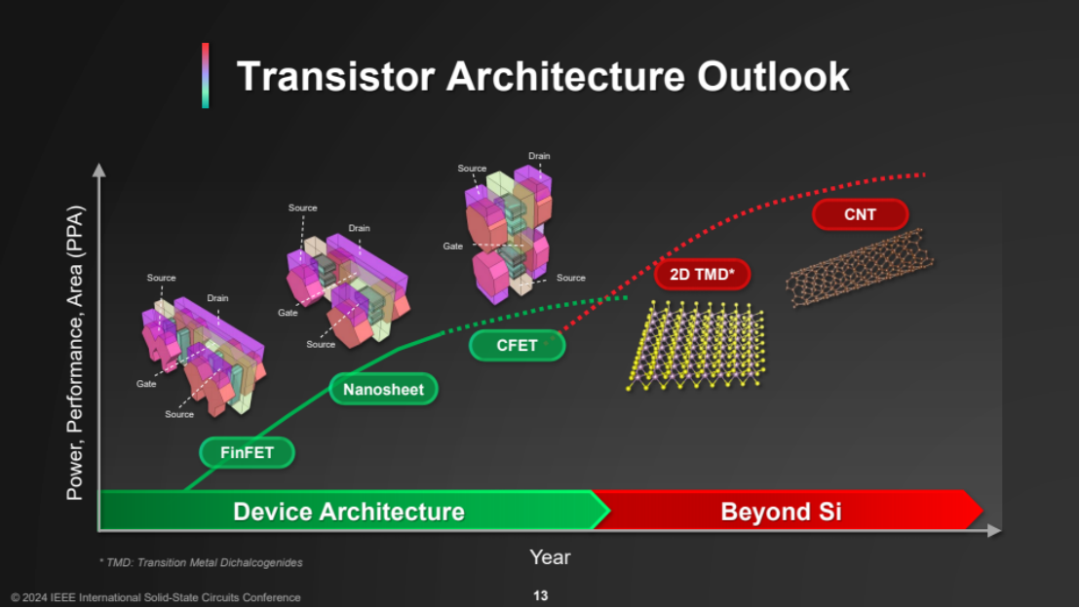

圖案化技術方面,7納米中,EUV的引入為我們鋪平了道路,推動幾何縮放向前發展。很多人會問:下一步是什么?Kevin Zhang表示,下一步需要利用Nanosheet,經過幾代人的努力獲得最佳值,即這個新晶體管的極限。與此同時,臺積電也在忙于制造全新的晶體管架構:CFET。本質上,是通過將N-transistor、NMOS和PMOS堆疊在一起,可以將密度大大提高近兩倍。

在材料方面,臺積電也致力于新材料,例如一種低維材料,通過使用這種新材料,我們可以實現更加節能的目標,遠超當今的器件或者晶體管。

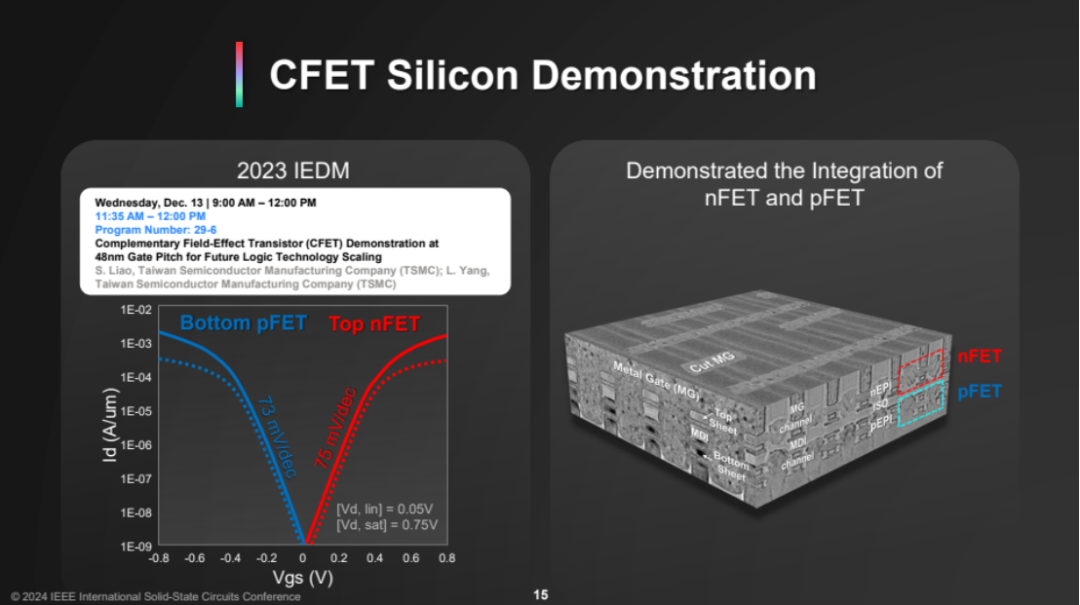

進一步了解CFET可以帶來的好處,如上圖可見,CFET(互補式場效晶體管CFET)是將nMOS和pMOS 垂直堆疊,可大幅改善零組件電流,使晶體管密度提升1.5~2 倍。

這項技術將硅(Si)和鍺(Ge)等不同材料從上下方堆疊,使p型和n型的場效晶體管更靠近。通過這種疊加方式,CFET 消除n to p 分開的瓶頸,將運作單元活動區域(cell active area)面積減少2 倍。

Kevin Zhang展示了一張圖片,指出這并不是僅僅在PPT上的想法。從上圖可以看到,這是臺積電實驗室制造的真正集成設備,還有晶體管IV優美的曲線。就推動創新而言,這是晶體管架構的一個重要里程碑。

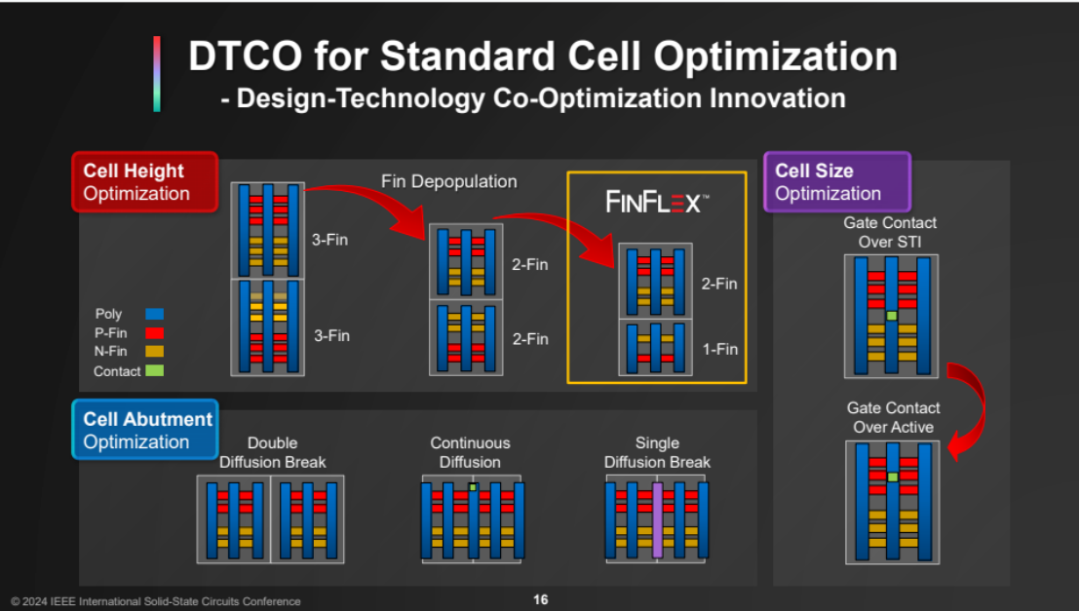

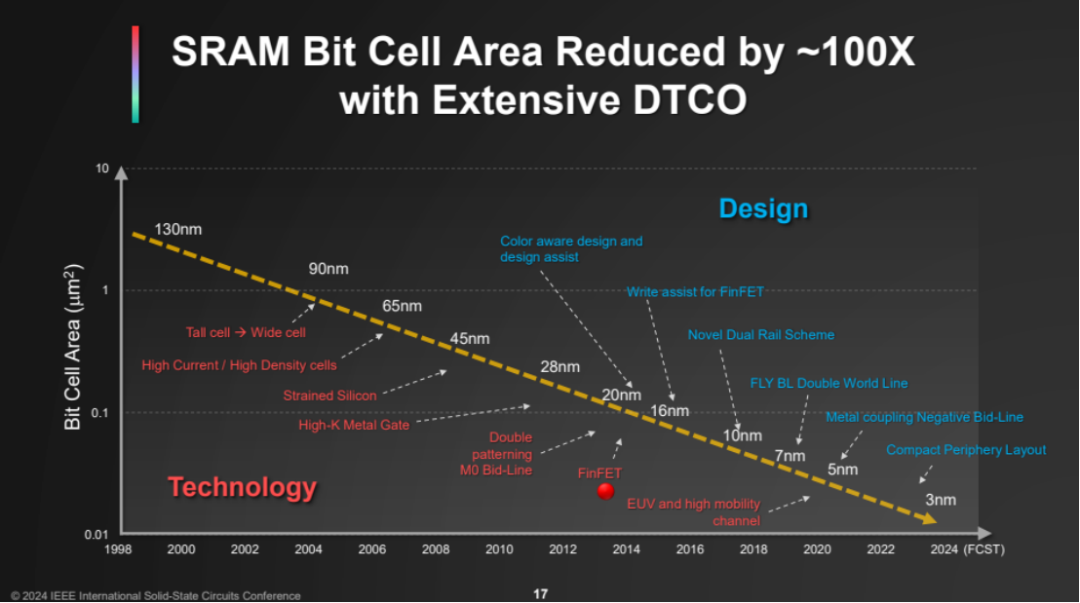

隨著晶體管尺寸的縮小,繼續縮小晶體管的幾何形狀變得越來越困難,成本也越來越高。設計師和工程師必須共同努力才能夠實現產品層面效益的最佳縮放。因此,臺積電經常將其成為設計技術聯合組織,或DTCO。

上圖展示了一個基于FinFET技術的數學圖書館設計示例。通過使用D-POP技術,減少每個部分的鰭片數量,可以在減小幾何尺寸的同時降低功耗。但是當每個設備達到兩個鰭片式,設計人員會面臨困境。

通過DTCO,臺積電的設計和技術團隊共同努力,創新的提出了FinFlex的新想法。本質上,允許設計人員混合和匹配單鰭器件、雙鰭器件或者雙鰭器件和三鰭器件,因此我們可以同時實現最佳的性能、密度和功耗。

另一個很好的例子是SRAM位單元。上圖展示了SRAM從130nm一直到今天的3nm,實現了超過100倍的密度提升,這種規模化實際上是流程創新和協作結合的成果,采用更先進的設計技術。

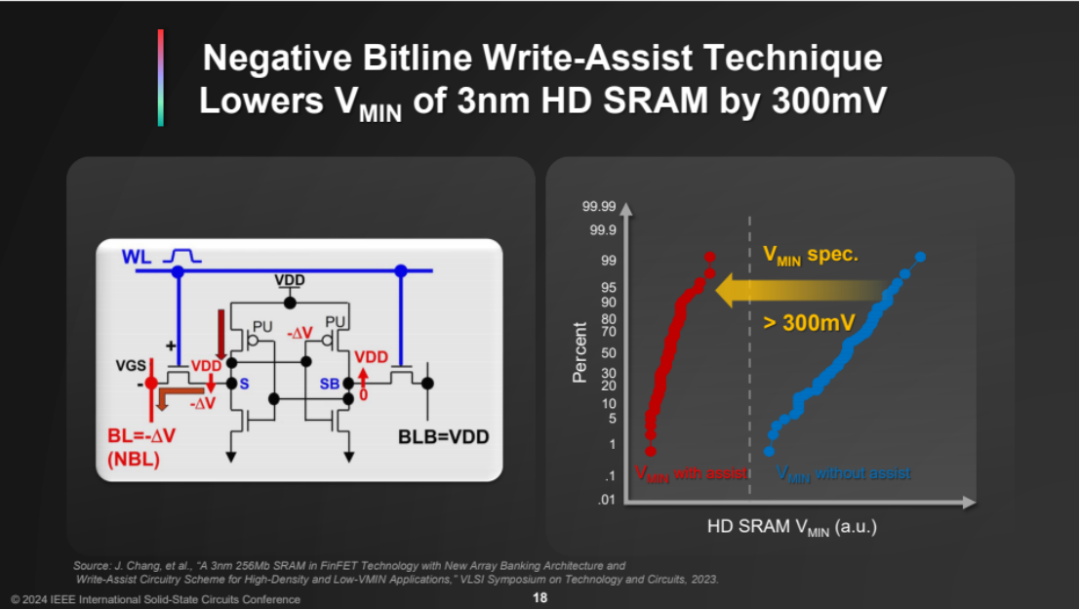

說到SRAM,就不得不談到最低工作電壓,或者說Vmin。在過去很長時間,為了降低電壓,必須采用更大的存儲單元。通過應用創新的設計技術,我們可以實現超過300毫伏的Vmin改善,這對于低功耗運行非常重要。

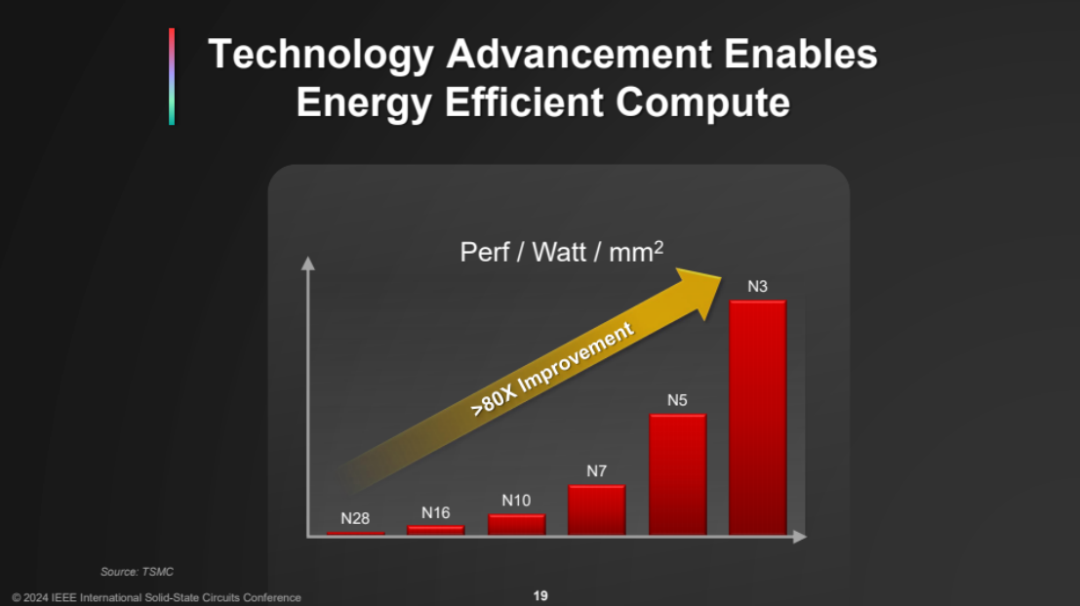

技術擴展的本質是為了節能計算。整個半導體行業走了很長一段路。上圖展示十年多的規模,臺積電實現了超過80倍的能源效率。

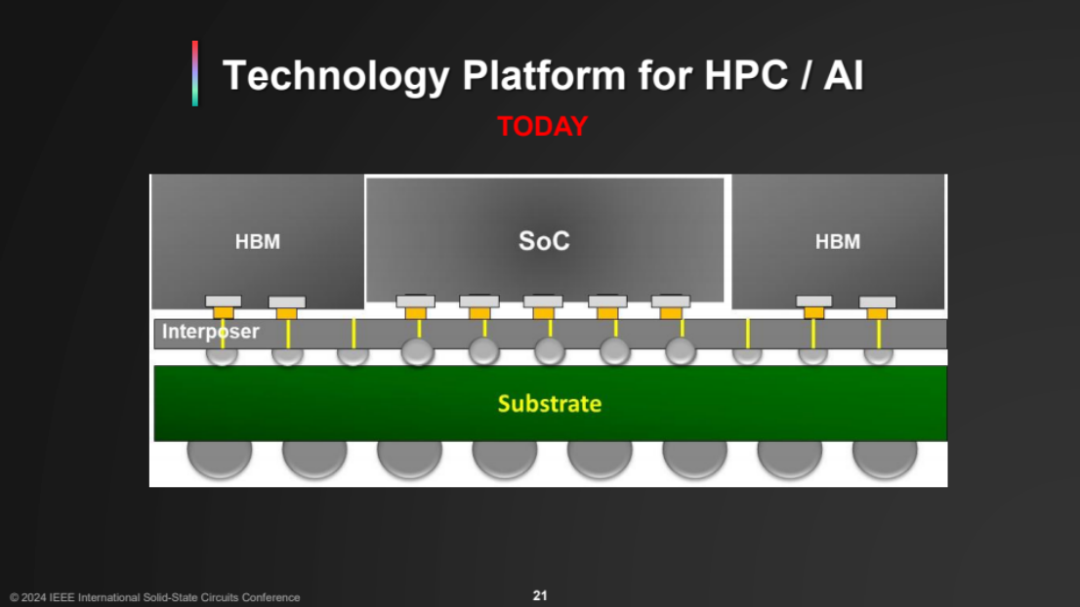

關于HPC和AI方面,如果看看今天所有的人工智能加速器,無論是GPU還是TPU或者是定制的ASIC,這些本質上是具有某種特定的集成方案。基本上,使用CowoS技術帶來的先進芯片。如今主要是5nm技術和HBM在一起,Kevin Zhang認為這還遠遠不夠。

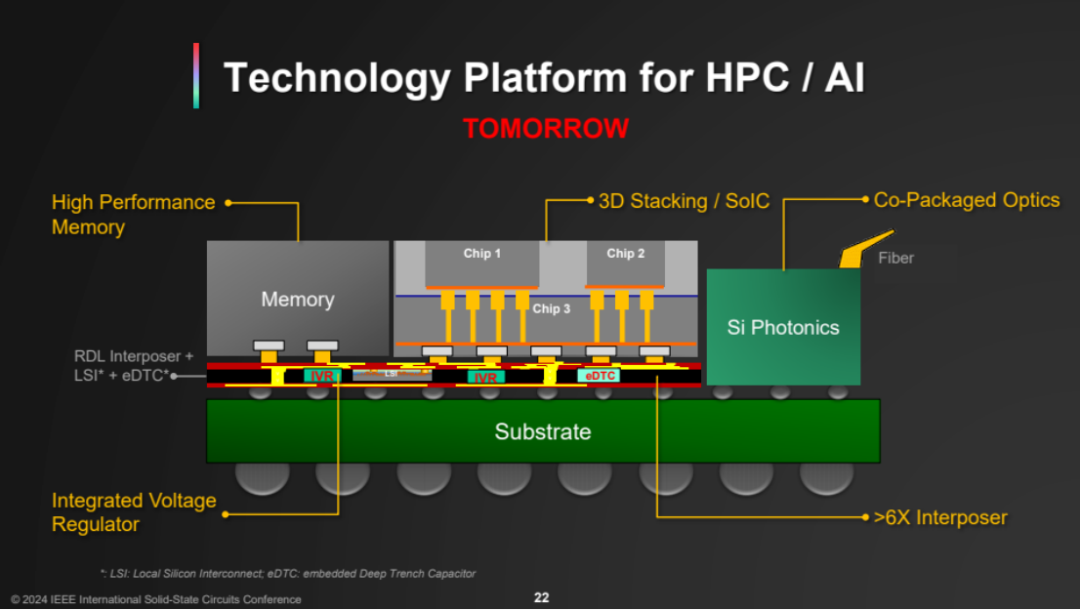

展望未來,這個平臺需要大幅提升以滿足高性能計算的需求。因此,這種配置的核心實際上是更高密度、低能耗的計算。需要去棧才能達到計算密度,需要多個最先進的芯片垂直堆疊在一起,以提供所需的計算密度。并且還需要大量的內存,因此需要加入更多的HBM。這就是為什么,硅中介層和CoWoS必須進一步擴展。

這仍然不夠,電力傳輸是一個問題,因此需要集成穩壓器才能解決電力輸送的挑戰。I/O和帶寬互聯密度也是一個問題,因此需要將硅光子學引入封裝中,這就是未來的發展方向。

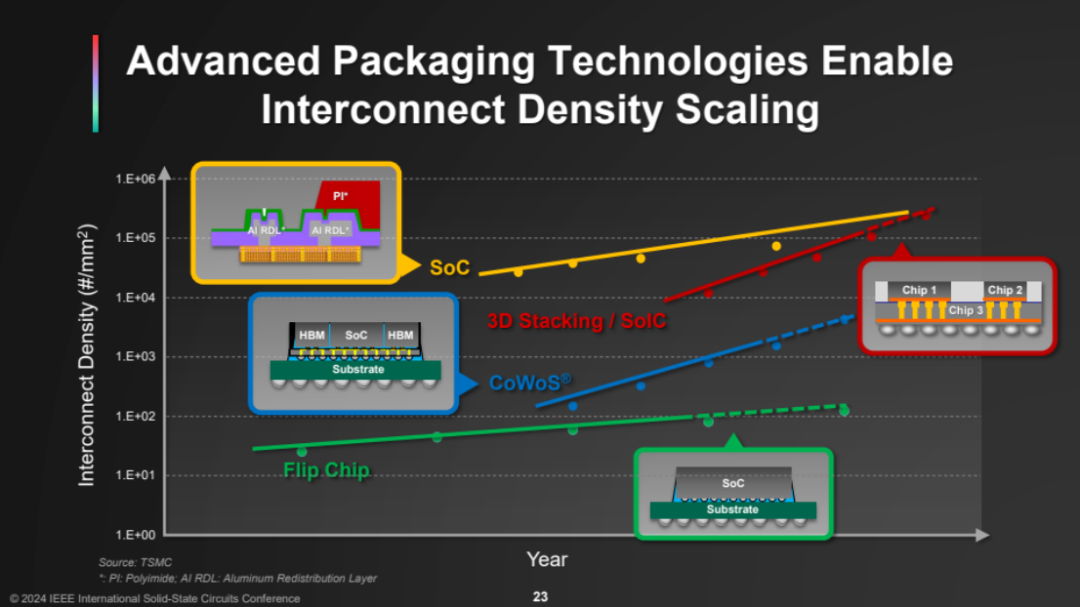

談一談3D堆疊,上圖展示了互連密度。我們進行堆疊的原因是為了實現芯片到芯片之間的高密度互連。圖中的曲線頂部曲線是SoC,本質上是單片互連。底部曲線是常規封裝能夠達到的密度。中間部分是CoWoS封裝。

談到3D 堆疊,Kevin Zhang展示一張圖,并表示為達到更高的互連密度(Interconnect Density),即Chip To Chip 連結,透過3D 堆疊可以使接合的Pitch 一路縮小到幾微米,實現單晶(Monolithic)的互連密度,“所以3D堆疊才是未來”。

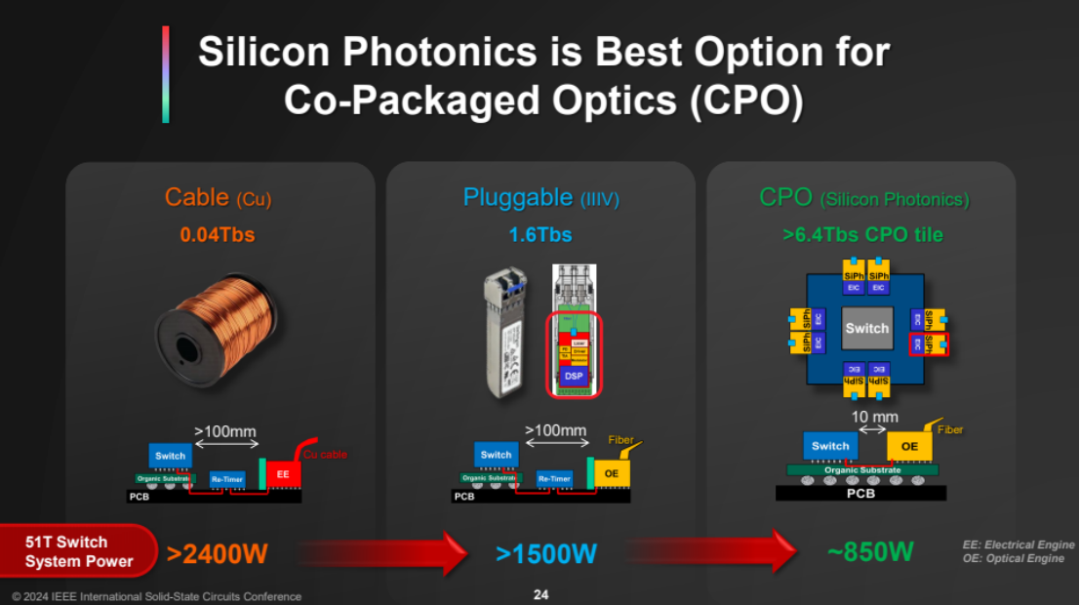

談到硅光子/共封裝光學(CPO)方面,Kevin Zhang指出,電子擅長運算,但光子在信號或通信時比較好。他以50T交換機舉例,如果全都用電子并采用銅線材質的系統,會燒掉2,400 W。

目前解決方案是采用插拔式模組(Pluggable),可省下40% 功耗(> 1500W),但隨著未來需要更高速信號、更大頻寬,這遠遠不夠,因此需要把硅光子技術把光子能力帶進來。使用共封裝光學的先進封裝技術來正確實現光子功能。

在圖示中,需要用先進堆疊技術,把光子芯片和電子芯片堆疊,可使功耗可再降低50%,約5 皮焦耳(picojoules per bit),使功耗約在850W。

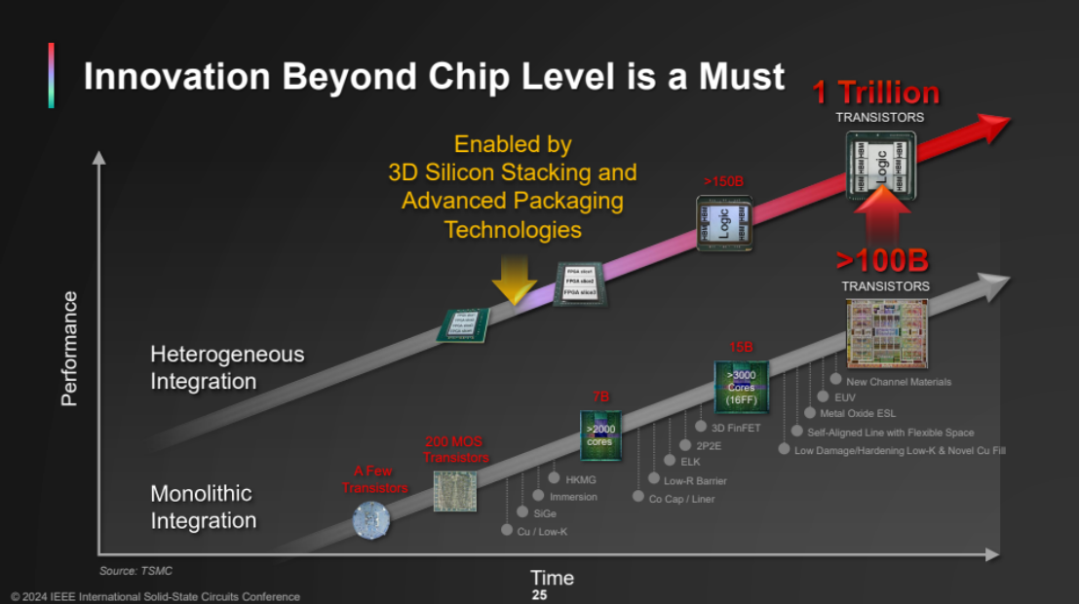

如今,使用最先進的晶體管技術,我們可以將大約1000億個晶體管封裝在同一個芯片中,但這還不足以解決未來的AI機器學習應用。必須利用先進的3D封裝技術,才能夠將晶體管的數量真正增加到一萬億個,以滿足計算需求。

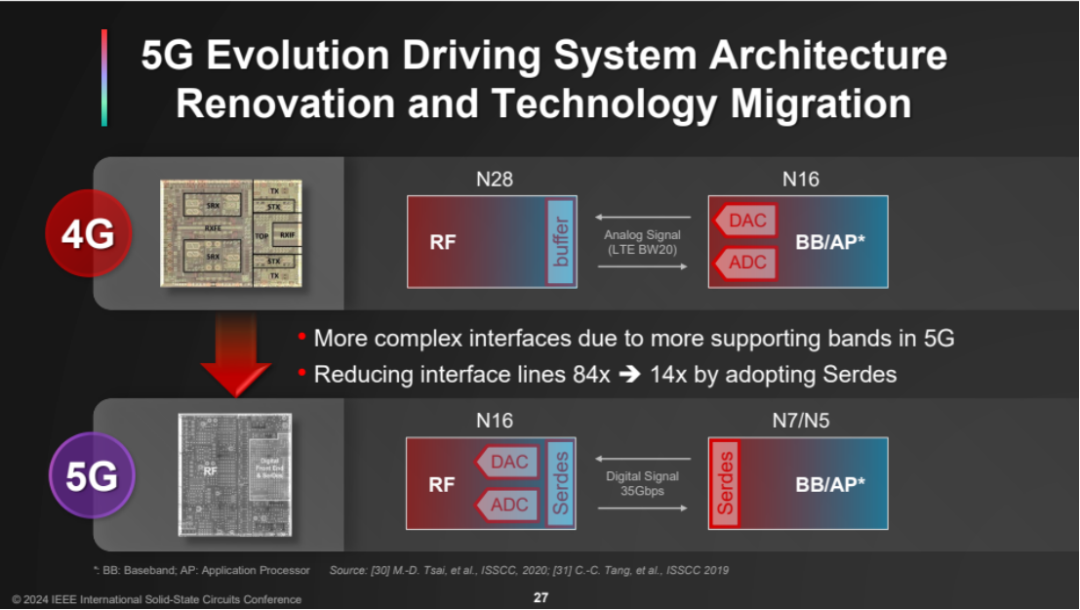

談到蜂窩射頻方面,他提到,當從4G向5G過渡時,為了將數據速率提高十倍,需要結合更多的數字電路,比如先進的ADC、先進的信號處理能力。在這樣做時,射頻設計、射頻收發器設計都可從28nm發展到16nm中收益。

如果展望未來,比如6G,就需要覆蓋更廣泛的頻率范圍,與FR3一樣需要提高數據速率。這就需要更先進的半導體,因此未來收發器的設計,如果使用7nm、5nm不必感到太過驚訝。

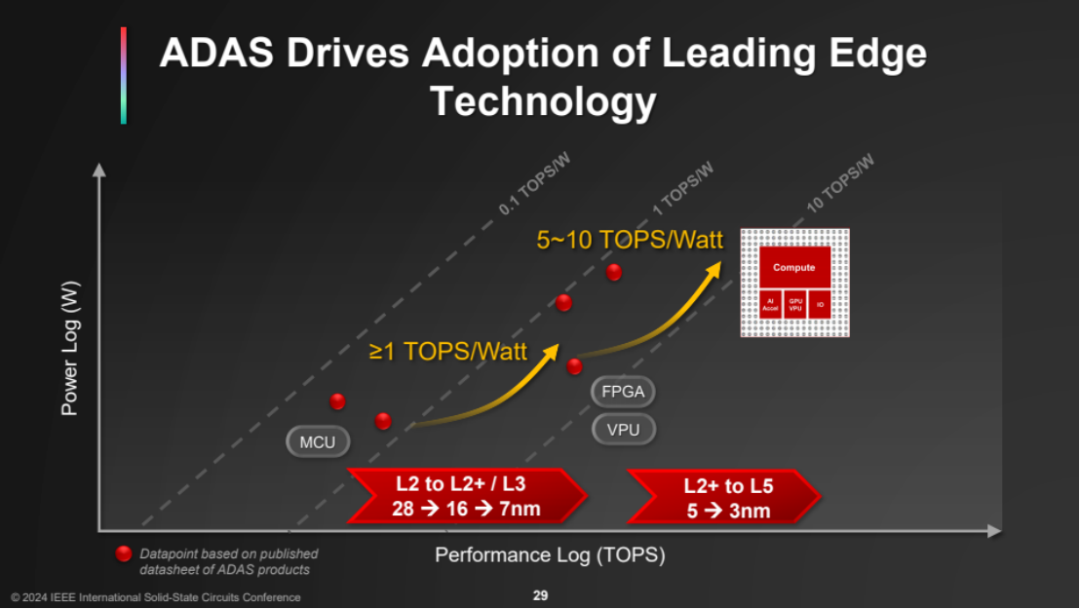

談到汽車方面,從根本上看,最新的汽車技術需要大量運算能力,但功耗正成為問題,尤其是由電池供電的汽車。

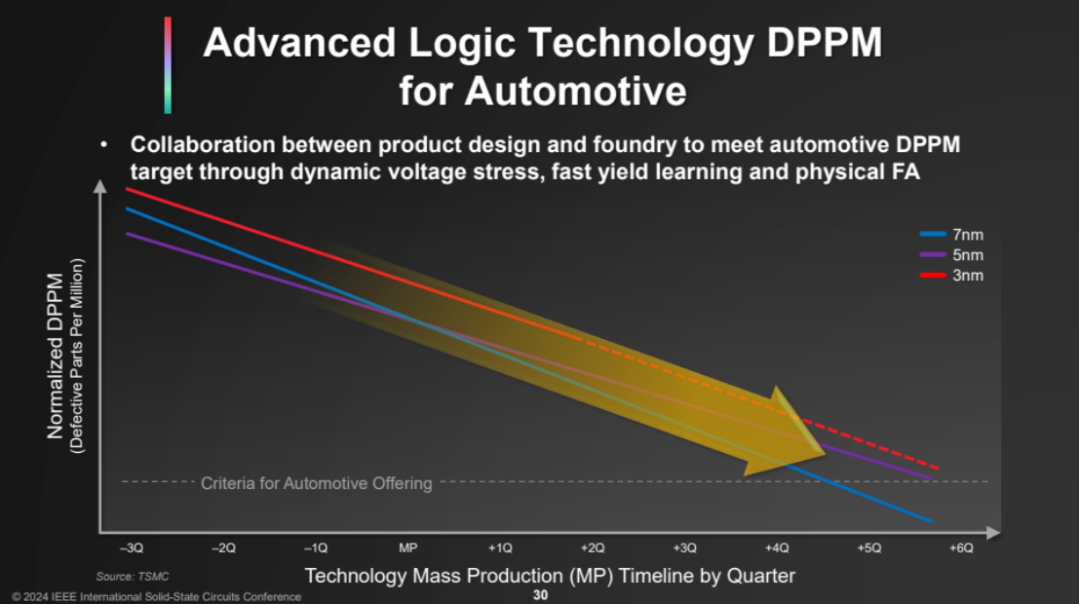

Kevin Zhang認為,車用半導體技術在導入上一直落后消費性或HPC 幾個世代,是因為非常需要嚴格的安全性要求,汽車應用的DPPM(缺陷率)必須接近零,也因此晶圓廠、半導體制造和汽車設計人員必須更密切地合作,以加快這個速度。

臺積電正在預先應用自動設計規則降低缺陷密度,Kevin Zhang承諾到:“在不久之后,你們會看到3nm導入汽車。”

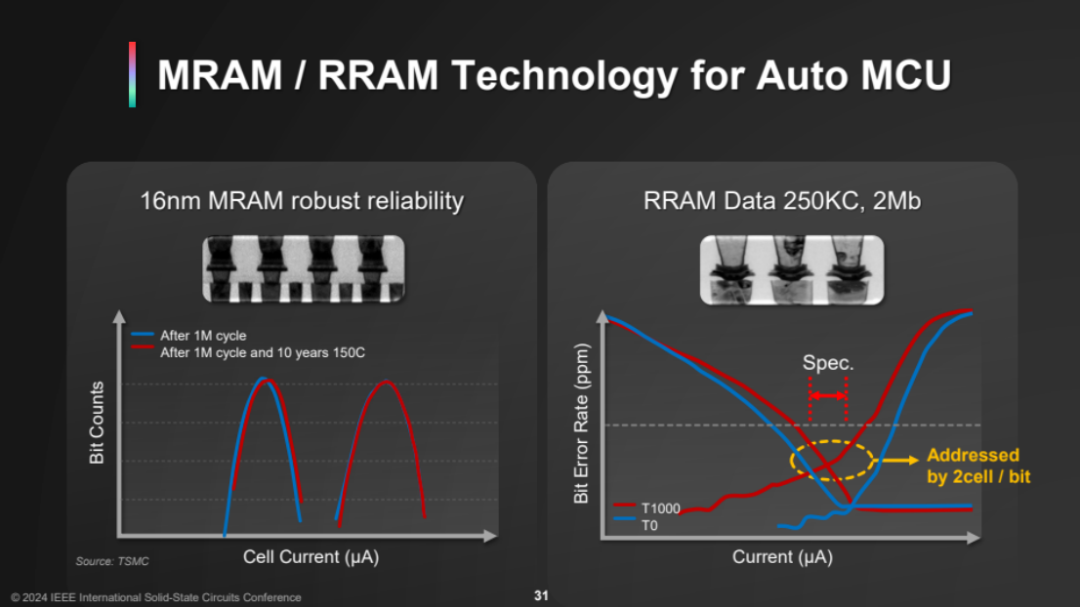

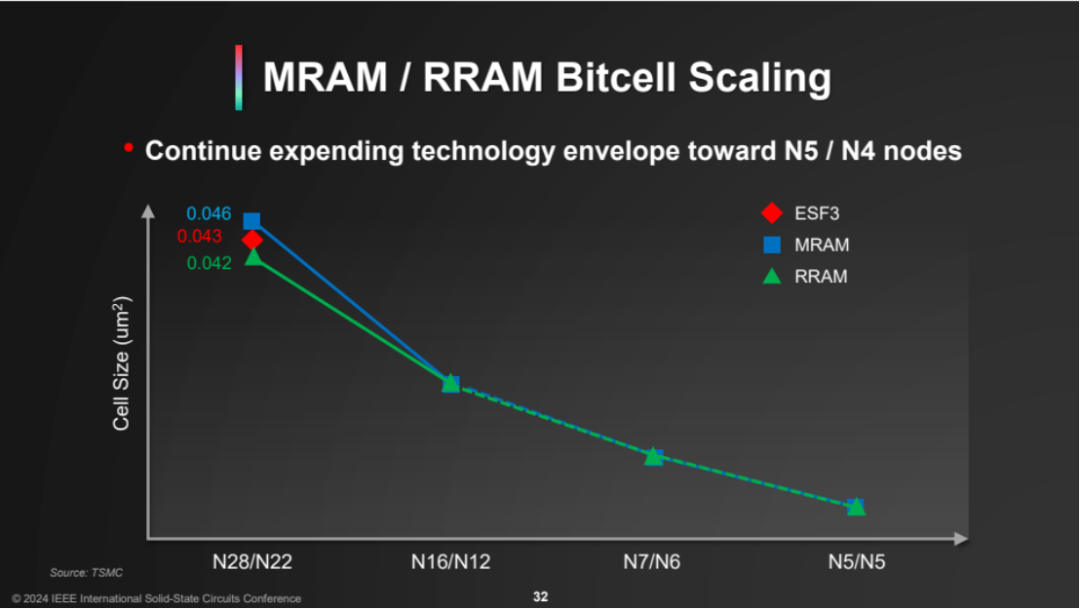

談到MCU方面,MCU在汽車轉型為區域架構后變更重要,也需要先進半導體技術給MCU 提供運算能力。傳統MCU 大都采用浮動閘極(floating gate)為基礎的技術,但浮動閘極技術在28 nm以下就卡關,所幸業界已經投資新內存技術,包括新的非揮發性存儲器如磁性隨機存取存儲器(MRAM)或電阻式存儲器(RRAM)。

也因此,從MCU 轉移到MRAM、RRAM為基礎的技術,有助于推動技術持續微縮,從28 nm縮小到16 nm、甚至是7 nm。

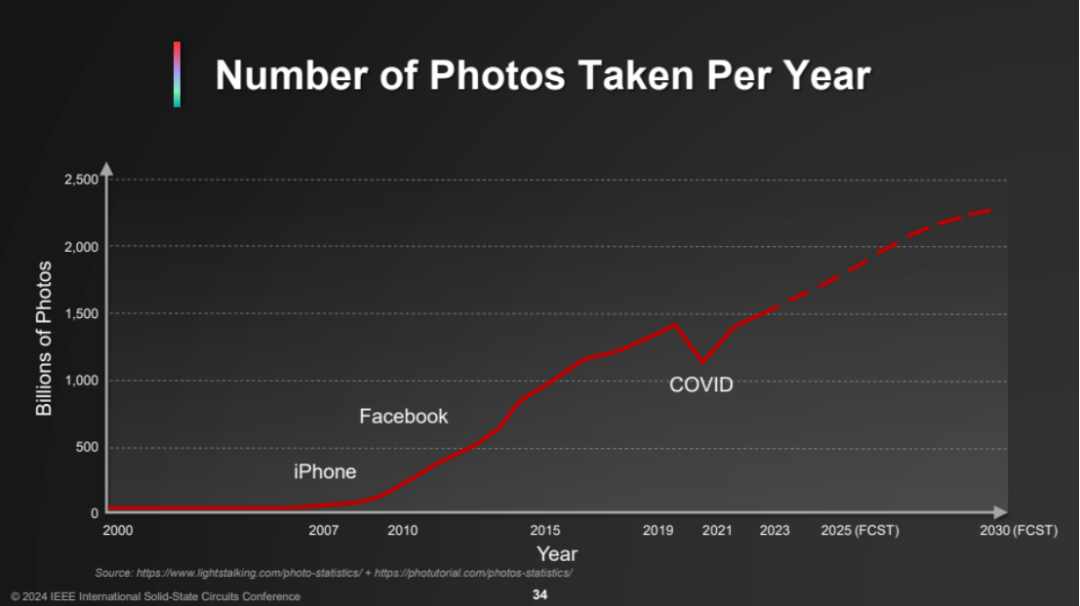

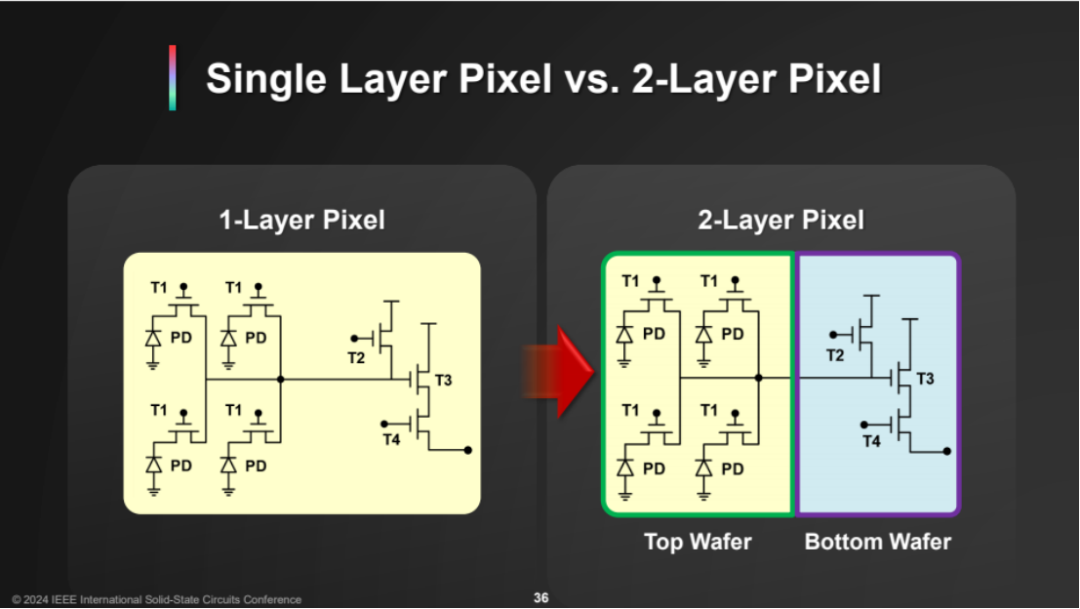

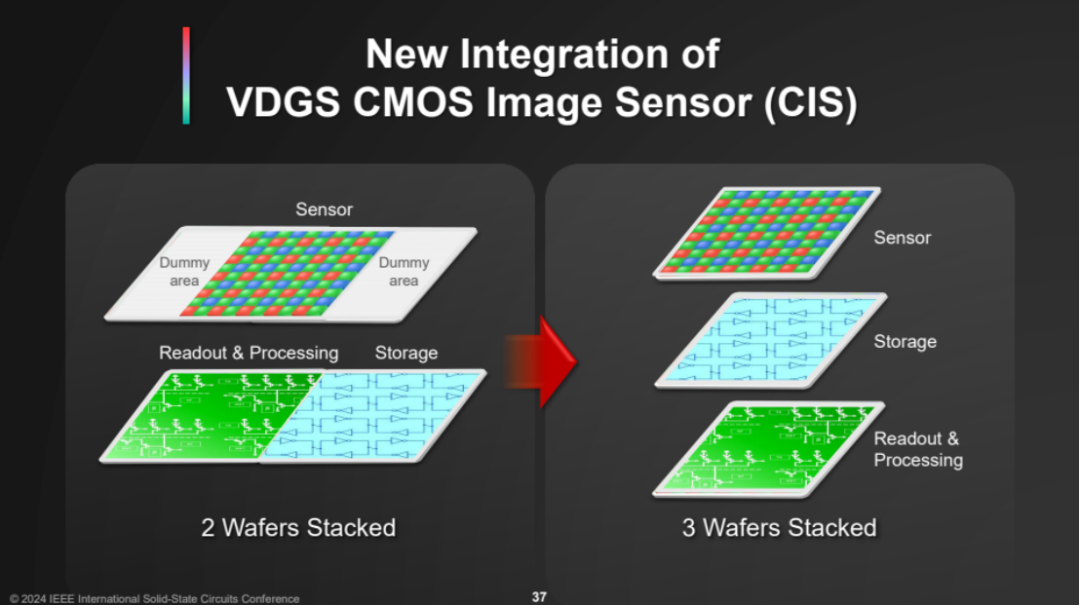

傳感器和顯示器方面,傳感器技術從最簡單的2D 設計、單層設計,到現在3D 晶圓堆疊的智能系統,基本上將信號處理層疊在傳感層上。Kevin Zhang也表示:“我們技術已經開始投資、研究多層設計的技術。”

??

??

進行三層或多層設計能追求畫素最佳化,繼續推動畫素尺寸縮小同時兼顧解析度需求,也能同時達到最佳傳感能力;另一個例子是AR、VR,透過將不同層的存儲器分開,再堆疊到其他邏輯芯片,可有效縮小尺寸,同時維持高效能需求。

最后Kevin Zhang分享自己的故事,他表示7 年前離開當時最大的半導體公司,去了中國臺灣。他離開的時候心想,他的半導體黃金時代已經過去了,去亞洲是要迎接職涯的日落時刻,但時間快轉7 年后,他表示:“我沒看到日落,而是明亮的日出。隨著AI 出現,半導體將驅動許多新應用,觸及人類生活每一個面向,并改變人類歷史的軌跡,所以我看到明亮、黃金的全新時刻,我們最好的日子還在前頭,讓我們一起努力使其成真。”

審核編輯:劉清

-

臺積電

+關注

關注

44文章

5651瀏覽量

166659 -

晶體管

+關注

關注

77文章

9704瀏覽量

138450 -

機器學習

+關注

關注

66文章

8424瀏覽量

132761 -

ChatGPT

+關注

關注

29文章

1564瀏覽量

7800

原文標題:最新!ISSCC 2024臺積電談萬億晶體管,3nm將導入汽車

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ISSCC 2024臺積電談萬億晶體管,3nm將導入汽車

ISSCC 2024臺積電談萬億晶體管,3nm將導入汽車

評論