CMOS(Complementary Metal-Oxide-Semiconductor)電路是一種常見的電子邏輯門電路技術,由一個PMOS(P型金屬氧化物半導體)和一個NMOS(N型金屬氧化物半導體)管道組成。在CMOS電路中,輸入信號的高和低電平取決于輸入信號的電壓和電路中的配置。

對于CMOS門電路來說,判斷輸出電平的關鍵是輸入電壓。在理想的情況下,當輸入電壓為高電平時,輸出為低電平;當輸入電壓為低電平時,輸出電平為高電平。這是因為CMOS電路的輸入管道是一個開關,當輸入電壓為高電平時,考慮到電平的傳輸,輸出電壓為低電平;當輸入電壓為低電平時,輸出電壓為高電平。

然而,在實際的CMOS電路中,存在微小的漏電流。當輸入電壓為高電平時,漏電流逐漸增加,使得輸出電壓變大。相反,當輸入電壓為低電平時,漏電流逐漸減小,導致輸出電壓變小。因此,判斷輸出電平時應該考慮輸入電壓和漏電流之間的關系。

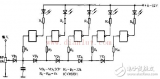

為了更好地理解CMOS門電路的輸入和輸出電平關系,我們可以具體分析不同類型的CMOS門電路,如與門(AND)、或門(OR)和非門(NOT)。在這里,我們將以與門為例進行討論。

與門是一種基本的布爾邏輯門電路,有兩個輸入和一個輸出。當且僅當所有輸入都為高電平時,輸出為高電平。對于CMOS與門電路,輸入電壓為低電平(0V)表示邏輯“0”,輸入電壓為高電平(VDD)表示邏輯“1”。當兩個輸入都為高電平時,輸出為高電平;否則,輸出為低電平。

具體地說,當一個輸入為高電平時,該輸入管道將打開,流經漏電流,導致輸出電壓稍微上升,但仍然為低電平。當兩個輸入都為高電平時,兩個輸入管道都打開,漏電流增加,使得輸出電壓顯著上升,接近高電平。因此,輸出電平為高電平,表示所有輸入都為高電平。

當任何一個輸入為低電平時(邏輯“0”),相應的輸入管道關閉,不會存在漏電流,輸出電壓保持為低電平。只有當兩個輸入都為高電平時,輸出電平才為高電平。

需要注意的是,CMOS門電路的輸出電平受到供電電壓的影響。通常情況下,供電電壓VDD為高電平,對于大多數應用而言,VDD為正常操作電壓的一半。更高的供電電壓意味著更高的輸出電平。

綜上所述,CMOS門電路的輸入和輸出電平關系由輸入信號的電壓和漏電流之間的相互作用確定。當輸入電壓為高電平時,輸出電平通常是低電平,但存在微小的漏電流增加輸出電平。當輸入電壓為低電平時,輸出電平通常是高電平,但漏電流較小導致輸出電平略微降低。根據不同類型的CMOS門電路,如與門、或門和非門,我們可以確定輸出電平取決于輸入電平的組合方式。當輸入組合滿足門電路的邏輯關系時,輸出電平為高電平;否則,輸出電平為低電平。

-

門電路

+關注

關注

7文章

199瀏覽量

40219 -

CMOS電路

+關注

關注

0文章

49瀏覽量

11577 -

漏電流

+關注

關注

0文章

266瀏覽量

17068 -

高電平

+關注

關注

6文章

153瀏覽量

21478

發布評論請先 登錄

相關推薦

轉載-------TTL和CMOS門電路的區別

CMOS電平轉換電路詳解

CMOS電路什么輸入為高電平 cmos門電路輸出電平判斷

CMOS電路什么輸入為高電平 cmos門電路輸出電平判斷

評論