CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)是一種廣泛使用的集成電路技術(shù),它利用了兩種類型的晶體管:N型和P型。CMOS門電路是數(shù)字邏輯電路的基本構(gòu)建塊,包括CMOS與門、或門、非門、異或門等。要判斷CMOS門電路的輸出狀態(tài),我們需要了解以下幾個(gè)關(guān)鍵方面:

- CMOS晶體管的工作原理:

- N型晶體管(NMOS):在柵極電壓高于源極電壓時(shí)導(dǎo)通,低于源極電壓時(shí)截止。

- P型晶體管(PMOS):在柵極電壓低于源極電壓時(shí)導(dǎo)通,高于源極電壓時(shí)截止。

- CMOS門電路的基本結(jié)構(gòu):

- CMOS與門:由一對(duì)NMOS和PMOS晶體管組成,只有當(dāng)所有輸入都為高電平時(shí),輸出才為高電平。

- CMOS或門:由一對(duì)NMOS和PMOS晶體管組成,只要有一個(gè)輸入為高電平,輸出就為高電平。

- CMOS非門:由一對(duì)NMOS和PMOS晶體管組成,輸出與輸入相反。

- CMOS異或門:由多個(gè)CMOS與門、或門和非門組成,實(shí)現(xiàn)輸入的異或邏輯。

- CMOS門電路的靜態(tài)特性:

- CMOS門電路的動(dòng)態(tài)特性:

- CMOS門電路的輸出狀態(tài)判斷方法:

- 邏輯表:列出所有可能的輸入組合及其對(duì)應(yīng)的輸出狀態(tài)。

- 真值表:列出所有可能的輸入組合及其對(duì)應(yīng)的真值輸出(0或1)。

- 波形圖:顯示輸入信號(hào)和輸出信號(hào)隨時(shí)間變化的圖形。

- CMOS門電路的設(shè)計(jì)考慮:

- 電源電壓:CMOS門電路的電源電壓通常為3.3V或5V。

- 負(fù)載電容:設(shè)計(jì)時(shí)需要考慮輸出端的負(fù)載電容,以確保傳播延遲在可接受范圍內(nèi)。

- 噪聲容限:CMOS門電路具有一定的噪聲容限,可以容忍一定程度的電壓波動(dòng)。

- CMOS門電路的故障診斷:

- 短路測試:檢查晶體管是否短路。

- 開路測試:檢查晶體管是否開路。

- 靜態(tài)電流測試:檢查CMOS門電路的靜態(tài)電流是否在正常范圍內(nèi)。

- CMOS門電路的應(yīng)用:

- 數(shù)字邏輯設(shè)計(jì):CMOS門電路是數(shù)字邏輯設(shè)計(jì)的基本構(gòu)建塊。

- 微處理器:CMOS技術(shù)被廣泛應(yīng)用于微處理器的設(shè)計(jì)。

- 存儲(chǔ)器:CMOS技術(shù)也被用于存儲(chǔ)器的設(shè)計(jì),如SRAM和DRAM。

- CMOS門電路的發(fā)展趨勢:

- 工藝縮放:隨著工藝技術(shù)的發(fā)展,CMOS門電路的尺寸不斷縮小,性能不斷提高。

- 低功耗設(shè)計(jì):為了降低功耗,CMOS門電路的設(shè)計(jì)越來越注重低功耗技術(shù)。

- 新型邏輯門:研究人員正在探索新型的CMOS邏輯門,以實(shí)現(xiàn)更高的性能和更低的功耗。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

晶體管

+關(guān)注

關(guān)注

77文章

9744瀏覽量

138822 -

CMOS門電路

+關(guān)注

關(guān)注

0文章

6瀏覽量

4921 -

集成電路技術(shù)

+關(guān)注

關(guān)注

0文章

5瀏覽量

1759

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

個(gè)互補(bǔ)輸出結(jié)構(gòu)的CMOS門電路

如題 能否將兩個(gè)互補(bǔ)輸出結(jié)構(gòu)的CMOS門電路輸出端并聯(lián),接成線與……??我知道TTL的不能但這個(gè)不確定……

發(fā)表于 10-12 23:09

轉(zhuǎn)載-------TTL和CMOS門電路的區(qū)別

本帖最后由 hxing 于 2014-3-23 14:48 編輯

TTL和CMOS門電路的區(qū)別:1. TTL和帶緩沖的TTL信號(hào) 輸出高電平>2.4V,輸出低電平=2.0V,輸入

發(fā)表于 03-23 14:27

CMOS和TTL集成門電路多余輸入端如何處理?

使用CMOS門電路時(shí)輸入端特別注意不能懸空。在使用時(shí)應(yīng)采用以下方法: 1、與門和與非門電路:由于與門電路的邏輯功能是輸入信號(hào)只要有低電平,輸出

發(fā)表于 08-30 11:18

CMOS和TTL集成門電路多余輸入端如何處理?

使用CMOS門電路時(shí)輸入端特別注意不能懸空。在使用時(shí)應(yīng)采用以下方法: 1、與門和與非門電路:由于與門電路的邏輯功能是輸入信號(hào)只要有低電平,輸出

發(fā)表于 12-03 10:49

CMOS邏輯門電路

CMOS邏輯門電路

CMOS邏輯門電路是在TTL電路問世之后 ,所開發(fā)出的第二種廣泛應(yīng)用的數(shù)字集成器件,從發(fā)展趨勢來看,由于制造工藝的

發(fā)表于 04-06 23:25

?2.2w次閱讀

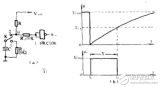

CMOS集成門電路延時(shí)器的設(shè)計(jì)

本文主要介紹了CMOS電路的構(gòu)成機(jī)器集成門電路的構(gòu)成與延時(shí)器的設(shè)計(jì)等。

發(fā)表于 11-04 11:06

?15次下載

如何判斷邏輯門電路的好壞?有哪些方法?

門電路(數(shù)字電路)與模擬電路(也叫線性電路)工作時(shí)最大的區(qū)別就是:門電路的輸入輸出信號(hào)一般只有兩

TTL門電路和CMOS有什么特點(diǎn)

TTL門電路和CMOS有什么特點(diǎn)? TTL門電路和CMOS是數(shù)字電路常用的兩種門電路,具有不同的

CMOS電路什么輸入為高電平 cmos門電路輸出電平判斷

半導(dǎo)體)管道組成。在CMOS電路中,輸入信號(hào)的高和低電平取決于輸入信號(hào)的電壓和電路中的配置。 對(duì)于CMOS門電路來說,

cmos或非門電路與ttl或非門電路的邏輯功能

本文就CMOS或非門電路和TTL或非門電路的邏輯功能進(jìn)行了詳細(xì)講解。首先介紹了CMOS和TTL兩種電路的基本原理和實(shí)現(xiàn)方式。然后分別從輸入特

如何判斷TTL門電路的輸出狀態(tài)?

TTL(晶體管-晶體管邏輯)門電路是數(shù)字電子學(xué)中常用的構(gòu)建模塊,它們基于晶體管實(shí)現(xiàn)基本的邏輯功能。

三態(tài)門電路的輸出有哪三種狀態(tài)

三態(tài)門電路是一種特殊的數(shù)字邏輯電路,其輸出可以有三種狀態(tài):高電平、低電平和高阻抗狀態(tài)。這種電路在

非門電路的輸入端電阻模式怎么設(shè)置電平狀態(tài)

非門電路的輸入端電阻模式設(shè)置電平狀態(tài)的方法主要取決于非門電路的類型(如TTL、CMOS等)以及具體的設(shè)計(jì)需求。以下是一些一般性的指導(dǎo)原則:

怎么判斷cmos門電路的輸出狀態(tài)

怎么判斷cmos門電路的輸出狀態(tài)

評(píng)論