采用UltraScale/UltraScale+芯片進行DFX設計時,建議從以下角度對設計進行檢查。

動態區是否包含全局時鐘緩沖器或MMCM/PLL?

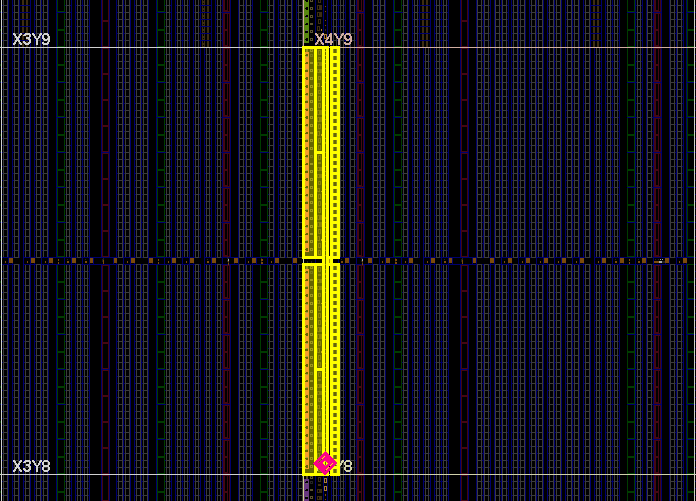

當這些時鐘物理單元出現在動態區,那么相關的物理單元都要以PU(Programmable Unit)的一部分出現在動態區。如下圖所示,圖中紅色標記為MMCM,黃色標記為相關的PU,包括以整個Clock Region為高度的I/O Bank,與之緊鄰共享布線資源的CLB。

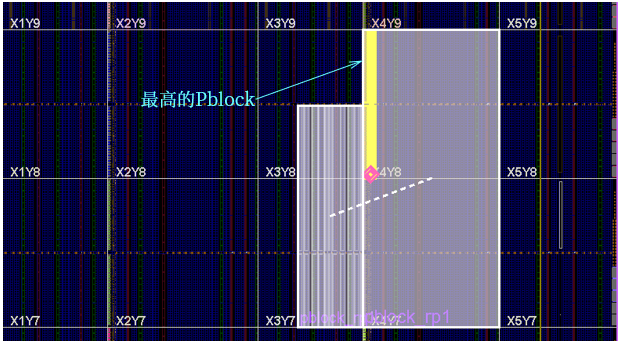

這就意味著在畫Pblock時,Pblock的高度要Clock Region對齊,同時Pblock的形狀最好為矩形。一旦為其他形狀,最高的矩形部分必須與Clock Region對齊且包含I/O Bank和相應的全局時鐘緩沖器或MMCM/PLL,如下圖所示。圖中右側高亮矩形為最高的矩形,其邊界與Clock Region對齊,且包含上圖所示的黃色區域。

是否使用了下列邏輯單元: BSCAN/DCIRESET/FRAME_ECC/ICAP/STARTUP/USR_ACCESS?

這些模塊必須放置在靜態區。

是否設置了Pblock的邊界?

對于UltraScale/UltraScale+芯片,DFX設計時Pblock的X軸邊界(水平方向)可以是PU如CLB、BRAM、DSP等,Y軸(豎直方向)邊界可以時鐘區域(CR)或IO Bank為邊界,如果動態區包含了時鐘緩沖器,那么整個CR都要在動態區。

如果是SSI芯片,動態區是否跨die?

如果目標芯片為SSI芯片,建議將動態區放置在一個SLR內。如果不可避免動態區要跨die,那么就要保證足夠的跨die資源(LAGUNA寄存器)可用。這時最好將die邊界的時鐘區域放置在動態區,例如,目標芯片為xcvu5p,有兩個die。動態區如果在die1,那么還要包括die0的邊界CR,即die1+CR(die0邊界)。

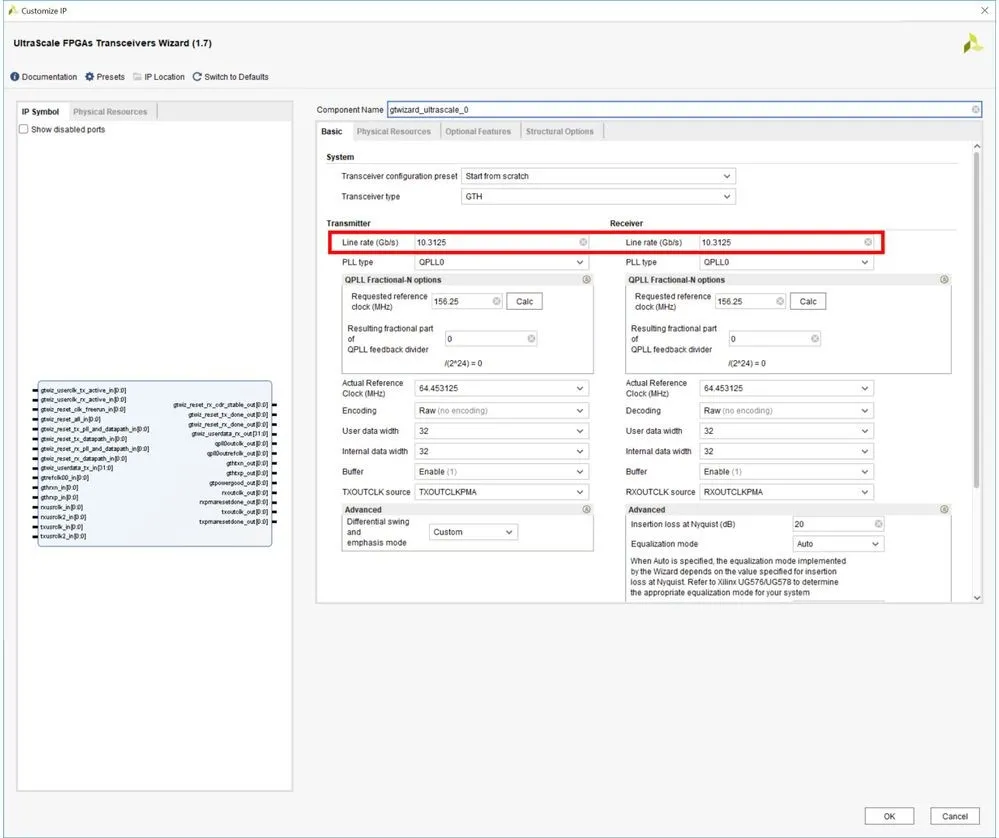

高速收發器是否在動態區?

UltraScale/UltraScale+的GT是支持動態可重配置的,如果GT出現在動態區,那么GT所在的整個Quad包括GT_CHANNEL、GT_COMMON和BUFG_GT都必須包含在對應的動態區。

輸入/輸出管腳是否出現在動態區?

如果輸入/輸出管腳出現在動態區,那么I/O管腳所在的Bank包括I/O邏輯(XiPhy)和時鐘資源也要在動態區。同時同一個RP下的不同RM的I/O電平標準和方向必須保持一致,且要遵循DCI級聯規則。

同一個RP下的邏輯是否要封裝在一起?

DFX的直觀體現是同一個RP下有不同的RM,所以要動態可重配置的邏輯單元必須封裝在一個RM內。

關鍵路徑是否在RM內?

RP的邊界會限制一些優化,因此,建議將關鍵路徑放置在RM內。方法是將RM的輸入/輸出管腳都用流水寄存器打一拍,即給RM的信號在RM內先打一拍再使用,RM輸出的信號先打一拍再給出去。

Pblock是否合理?

Pblock的高度應與CR高度一致,以CR為邊界。若存在多個RP,避免RP共享同一個CR。Pblock的寬度以PU為準進行劃分。Pblock的形狀為標準矩形,避免階梯或回子形等特殊形狀。

在RM輸出端口是否設置了解耦邏輯?

在加載RP的部分bit文件時,RM輸出端口呈現不確定狀態,這時要添加解耦邏輯,以防止加載過程干擾動態區正常工作。

是否對configuration進行了驗證?

要使用命令pr_verify對所有的configuration進行驗證,保證匹配。

對綜合后的設計是否執行了DRC檢查?

對于DFX設計,綜合后的DRC檢查尤為重要,這可在設計早期發現潛在的問題。

是否要對RM側進行調試?

如果需要,具體方法可參考這篇文章。 如何對DFX設計進行調試?

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

51123瀏覽量

426097 -

時鐘

+關注

關注

11文章

1746瀏覽量

131669 -

UltraScale

+關注

關注

0文章

118瀏覽量

31498 -

dfx設計

+關注

關注

0文章

6瀏覽量

109

原文標題:UltraScale/UltraScale+ DFX設計檢查清單

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

針對UltraScale/UltraScale+芯片DFX應考慮的因素有哪些(2)

賽靈思推出全球最大容量的FPGA – Virtex UltraScale+ VU19P

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

全新 Virtex UltraScale+ FPGA 評估套件加速高帶寬應用

Zynq UltraScale+ MPSoC的發售消息

UltraScale/UltraScale+ GTH/GTY 收發器線速率設置的方法

UltraScale/UltraScale+的時鐘資源

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設計

UltraScale和UltraScale+ FPGA封裝和管腳用戶指南

采用Zynq UltraScale+ MPSoC滿足汽車ESD和SEED要求

AMD推出全新Spartan UltraScale+ FPGA系列

采用UltraScale/UltraScale+芯片的DFX設計注意事項

采用UltraScale/UltraScale+芯片的DFX設計注意事項

評論