歡迎了解

張浩亮方杰徐凝華

(株洲中車時代半導體有限公司新型功率半導體器件國家重點實驗室)

摘要:

主要研究了應用于IGBT模塊封裝中的銀燒結工藝和銅引線鍵合工藝,依據系列質量表征和評價方法,分別驗證并優化了銀燒結和銅引線鍵合的工藝參數,分析了襯板鍍層對燒結層和銅線鍵合界面強度的影響,最后對試制的模塊進行浪涌能力和功率循環壽命測試。結果顯示,與普通模塊相比,搭載銀燒結和銅線鍵合技術的模塊浪涌能力和功率循環壽命均有大幅的提升,并且銀燒結和銅線鍵合界面未見明顯的退化。

0?引言

在汽車和新能源器件等領域,功率器件模塊的工作溫度和功率密度的提高,對模塊封裝互連可靠性要求也更高。隨著芯片能力的提升,硅器件的工作結溫可能達到175℃。傳統的芯片連接工藝為焊料焊接,常用的SnAgCu系和SnSb系焊料難以在更高的工作溫度下保證模塊的可靠性;其次,芯片正面的鋁線鍵合點也一直是模塊長期可靠性的短板,模塊在承受周期性的應力時,鋁線鍵合點會出現疲勞退化。無鉛焊料的熔點較低(210~240℃),無法使用常規的PI膠涂覆進行鍵合點強化。因此,既要保證模塊能夠在高溫下穩定運行,又需要能夠在循環的“熱-機械”應力下保證高可靠性,需要開發能夠替代傳統焊接和鋁線鍵合點的互連工藝。

銀燒結材料具有更高的熱導率、電導率、機械強度和接近純銀的熔點,銀燒結工藝迅速成為最具應用前景的互連技術之一。銅引線鍵合點是一種替代鋁線鍵合點的很好的解決方案,除提供更高的鍵合強度外,相比鋁線,銅線還具有更強的通流能力。但其在工藝實現方面還存在相當的難度,因為銅線材質較硬,芯片正面必須做很厚的銅金屬才能兼容銅線鍵合,這又導致了金屬化后薄片晶圓的翹曲,帶來了新的工藝難題。

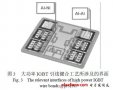

本文討論了一種結合銀燒結和銅引線鍵合技術的高可靠性互連技術,被稱為DTS(Die Top System)技術。文獻研究表明,該互連技術可以顯著提升模塊的功率循環能力。

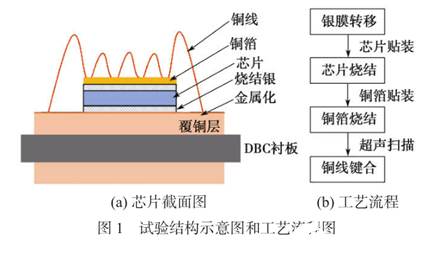

1?試驗結構與工藝流程

試驗結構如圖1(a)所示,在芯片與襯板之間使用銀燒結工藝實現互連,在芯片正面燒結一片銅箔作為緩沖層,并在銅箔上進行銅線鍵合。因為芯片需要進行雙面燒結,因此正面也需要進行金屬化處理。基本的工藝流程如圖1(b)所示,首先將銀膜轉移至芯片背面,然后進行“芯片-襯板”燒結,最后在銅箔上實現銅線鍵合。

2?試驗與分析

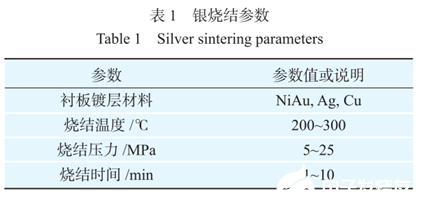

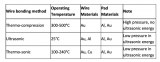

對大面積硅基芯片的燒結工藝進行研究,芯片尺寸為12.2 mm×12.2 mm,金屬化條件為雙面鍍Ni/Au。將芯片燒結到覆銅陶瓷基板(Direct Bonding Copper,DBC)襯板上,襯板的表面金屬化條件分別為鍍化學鎳金(Electroless Nickel/Immersion Gold,ENIG), Ag, Cu。根據銀燒結的工藝特點,通常可以分為有壓燒結和無壓燒結;根據所使用燒結材料的粒徑,也會將銀膏分為微米銀、納米銀、微納米混合材料和其他添加成分銀膏。本文中采用納米銀有壓燒結工藝,燒結工藝驗證的項點主要包括燒結溫度、壓力和時間,參數如表1所示。

為了觀察燒結界面的結合情況,使用超聲波掃描對燒結界面進行分析,然后觀察界面的微觀形貌,并分析燒結層孔隙。將樣品切割,并使用環氧鑲樣后研磨拋光,使用光學顯微鏡和掃描電鏡(SEM)觀察試樣橫截面的微觀組織,利用能譜儀(EDS)分析界面擴散層的成分組成,最后處理圖像并分析燒結層的孔隙分布。

使用直徑為0.375 mm的銅線進行鍵合工藝的研究,包括鍵合壓力、超聲能量和鍵合時間等主要工藝參數的研究。銅線鍵合工藝參數曲線主要包括3個階段,分別為初始接觸、參數上升和水平保持階段。對不同階段的銅線鍵合工藝參數進行了分析,推力測試作為評估指標之一,用于表征鍵合點的剪切強度,然后制備樣品,并使用SEM觀察鍵合界面,評估結合情況;最后在ΔT=100℃的條件下進行了模塊級的功率循環測試,同時常規封裝模塊作為對比對象同步進行了試驗;在模塊失效之后,對其測試壽命進行對比,并分析銀燒結和銅線鍵合界面相比試驗前的退化情況。

2.1?銀燒結工藝驗證和優化

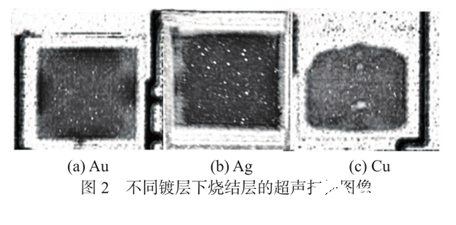

在相同的燒結條件下,不同鍍層襯板上的燒結層的超聲掃描圖像如圖2所示。從圖2可以看出,在鍍Au和鍍Ag的界面上,超聲掃描結果相似,燒結界面沒有出現分層和空洞,但在燒結過程中,裸銅襯板邊緣銅層在高溫下會發生氧化,氧化層阻礙了燒結銀顆粒與覆銅層之間的擴散,界面出現分層,圖像中顯示芯片邊緣的燒結不良。

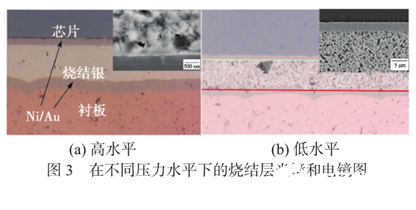

在襯板鍍NiAu和鍍Ag金屬化的條件下,銀燒結工藝對氣氛條件的要求更低。在不同的壓力水平下,從金相截面的光鏡和SEM圖像中可以看到,芯片的孔隙率會明顯不同(如圖3所示)。在更高的壓力水平下,燒結層內部的孔隙有效下降,從光鏡圖像中無法觀察到明顯的孔隙,在合適的工藝參數下,可以看到燒結銀與襯板鍍層原子互相擴散后,邊界已難以觀察到。

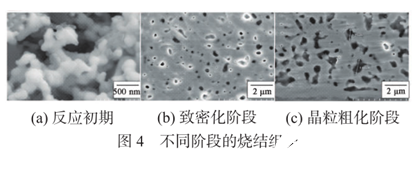

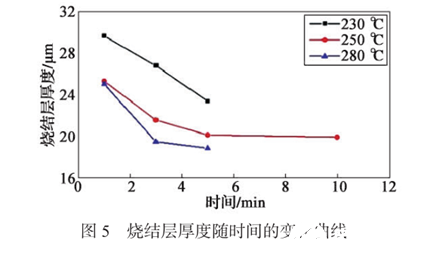

在燒結過程中,燒結溫度和燒結壓力是最重要的反應驅動力,燒結時間則是保證反應發生完全。燒結反應發生的主要驅動力為總表面能的降低,實現這一結果主要有2個反應方向,分別為致密化和晶粒粗化。在燒結反應的前期,原子擴散和晶界擴散是主要的反應機制,此刻表現為銀顆粒的合并、燒結頸的出現和生長,如圖4(a)所示。在反應中期和后期,體擴散和晶粒粗化成為反應的主導機制,此時主要表現為晶粒的持續生長與合并,燒結孔隙的數量逐漸減少。如圖4(b)所示,在致密化主導的組織中,孔隙較多,尺寸較小;當晶粒粗化主導反應時,轉變為圖4(c)所示的形貌,孔隙尺寸較大,晶粒合并生長。在相同的壓力條件下,不同的時間和溫度下燒結層厚度隨時間變化的趨勢如圖5所示。從圖5可以看出,隨著燒結溫度的升高,燒結層的致密化速率增加,在250℃的條件下,5 min的燒結時間之后,燒結層致密化速度快速下降。

2.2?銅線鍵合工藝

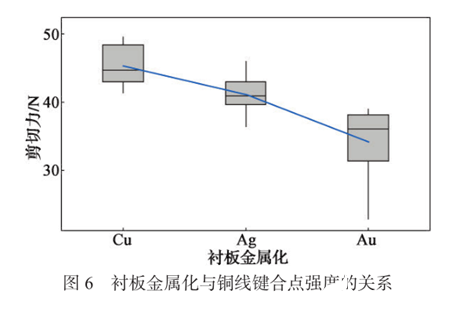

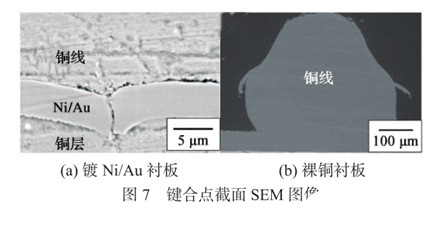

相比鋁線鍵合,銅線的硬度更高,鍵合工藝需要更大的壓力和能量,對鍍層和基材也都有一定的要求。盡管芯片正面已燒結緩沖銅層,但“銅層+燒結層”的總厚度相比銅線的直徑依然較薄,因此過高的鍵合參數依然會使芯片遭到損壞而失效。在相同的工藝參數下使用不同鍍層的襯板進行銅線鍵合對比,使用剪切強度作為表征指標,如圖6所示。鍍銀襯板的銅線鍵合強度略低于裸銅襯板,因為鍍銀層的厚度較薄,銅線可以破壞鍍層與基材的覆銅,直接形成連接,但此過程依然會消耗部分超聲能量,而在鍍NiAu襯板上的鍵合點推力強度收斂性較差,強度為20~40 N,相比裸銅襯板鍵合下降較多,這主要是由于在銅線鍵合工藝下Cu與Ni原子難以形成固溶強化,界面結合情況較差。如圖7所示,在Ni/Au鍍層界面,并沒有形成良好的擴散連接,而且連續鍍層在鍵合過程中發生了斷裂,界面連接的不穩定性導致鍵合強度大幅波動;在裸銅表面鍵合的銅線屬于同質金屬結合,界面擴散良好,沒有發現分層和裂紋的存在。

2.3?對芯片極限能力的提升

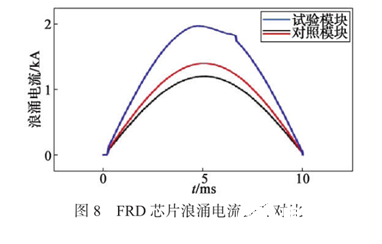

FRD芯片的浪涌能力對比如圖8所示。芯片正面燒結銅片和鍵合銅線后,FRD的浪涌能力獲得顯著的改善,相比于常規“焊接+鋁線”鍵合模塊,試制模塊芯片浪涌能力獲得大幅提升。由于芯片正面增加了燒結層和緩沖墊片,電流被有效均化,當芯片電流達到浪涌極限時,正面燒結層和銅線鍵合點均未出現破壞。與常規模塊相比,試制模塊浪涌失效的主要破壞模式從常見的芯片發射極炸毀轉變為場環終止區失效。

2.4?對模塊的功率循環壽命能力的提升

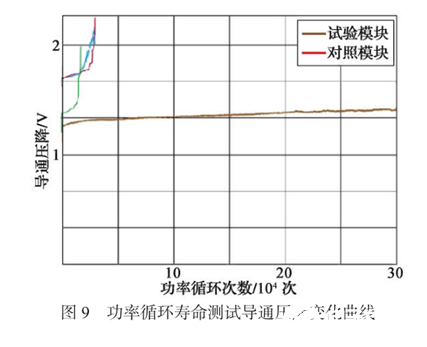

功率循環壽命測試導通壓降變化曲線如圖9所示,功率循環壽命測試的條件為ΔT=100℃。從圖9可以看出,試驗樣品循環壽命獲得了數倍的提高。常規模塊的失效模式為芯片正面鋁線鍵合點脫附,從而導致模塊互連失效,而試驗模塊在長時間的功率循環測試后,芯片并未出現電性能失效。

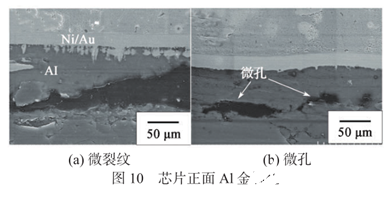

對失效模塊進行分析,盡管銅線鍵合點的強度出現了一定的退化,但仍在允許的范圍內,而位于芯片邊緣的鋁金屬化由于承受較大的循環應力,呈現退化跡象。在互連界面中,芯片正面的鋁金屬化層內出現了微裂紋萌生的跡象,內部出現韌窩和微孔,如圖10所示。從圖10可以看出,燒結界面結合良好,并無明顯的裂紋和分層出現。因此,在承受循環應力時,芯片本身正面的金屬化層可能成為潛在的失效風險點,可能逐漸發展成貫穿裂紋,導致器件的最終失效。

3?結語

在燒結工藝中,隨著燒結時間的增加,在不同的溫度下,燒結層厚度逐漸降低,隨溫度升高,燒結組織收縮的速度逐漸加快,同時增加壓力可以有效地降低燒結組織空隙率。在銀燒結工藝中,襯板鍍Au和鍍Ag界面的燒結效果相似,均優于裸銅襯板。襯板的基材和鍍層條件對銅線鍵合工藝均有一定影響。裸銅襯板由于和銅線屬于同質金屬結合,因此強度更高,相比之下,Ni/Au鍍層的鍵合界面存在裂紋,強度穩定性較差。

綜合來講,與常規封裝模塊相比,芯片雙面銀燒結和銅線鍵合技術可以明顯提高模塊的疲勞壽命,但該技術較高的材料成本和額外的工藝過程也導致其應用存在一定的限制,預計在碳化硅系列的寬禁帶功率器件中將具有較好的應用前景。

審核編輯 黃宇

-

芯片

+關注

關注

459文章

51773瀏覽量

431497 -

模塊

+關注

關注

7文章

2763瀏覽量

48594 -

IGBT

+關注

關注

1272文章

3896瀏覽量

252007

發布評論請先 登錄

相關推薦

IGBT模塊銀燒結工藝大揭秘,成本降低與性能提升雙贏策略

有償求助本科畢業設計指導|引線鍵合|封裝工藝

集成電路封裝中的引線鍵合技術

引線鍵合工藝參數對封裝質量的影響因素分析

LED引線鍵合的檢測內容與工藝評價

LED引線鍵合工藝評價

引線鍵合工藝流程講解

什么是引線鍵合?引線鍵合的演變

評論