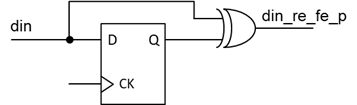

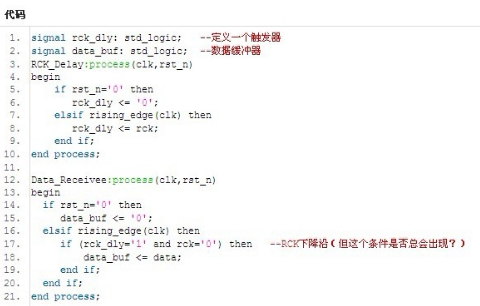

如何知道一個信號上升沿或下降沿是否到來?下面是一個簡單的邊沿檢測電路。

這個電路的原理很簡單。當din上升沿或下降沿到來時,din_re_fe_p產生一個脈沖。后續電路看到這個脈沖,就知道din上升沿或下降沿發生了。

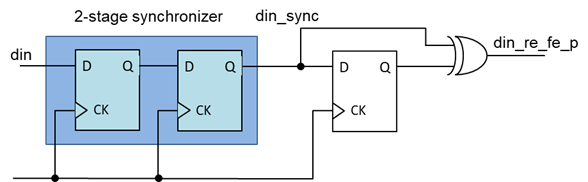

如果din是異步輸入,前面要加一個兩級同步器(其實就是兩級DFF)。

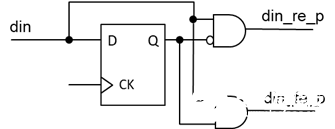

邊沿檢測可以演化出只檢測上升沿,只檢測下降沿。

邊沿檢測電路非常有用。

例1:作為跨時鐘域同步握手信號

有一組信號data_bus,需要從clk_a同步到clk_b。如果每一個信號都經過兩級同步器,那就太浪費資源了。而且有時一組信號要保證所有位傳到clk_b時同時更新,就更不能用兩級同步器了。兩級同步器的latency在1到3個周期之間,有隨機性,無法保證兩個信號各自通過同步器后同時更新。

這個場景可以加一個簡單的握手信號data_toggle。當clk_a這邊信號變化時,data_toggle也改變狀態(0->1或1->0)。data_toggle送到clk_b,經過兩級同步+邊沿檢測產生data_toggle_re_fe_p,clk_b這邊的邏輯看到data_toggle_re_fe_p脈沖后,就可以放心大膽地鎖存data_bus。

喜歡low power的朋友可以把data_toggle_re_fe_p作為ICG的EN信號。RTL寫得干凈,工具也能自動infer ICG。

邊沿檢測輸出作為ICG EN其實是非常有用的low power技巧之一。

當然,這個例子是很簡單地握手方式。復雜一些的可以用request,acknowledge之類的雙向握手。

clk_a送一個req=1到clk_b,告訴clk_b數據ready。

clk_b同步req并做上升沿檢測。檢測到req上升沿后鎖存數據。

clk_b發一個ack=1給clk_a,告訴clk_a數據已經鎖存。

clk_a同步ack并做上升沿檢測。檢測到ack上升沿后清除req=0,準備下一次傳數據。

clk_b這邊檢測到req下降沿,清除ack=0,準備接受下一次數據。

審核編輯:黃飛

-

電路圖

+關注

關注

10370文章

10726瀏覽量

535691 -

檢測電路

+關注

關注

13文章

309瀏覽量

58425 -

同步器

+關注

關注

1文章

98瀏覽量

14807

發布評論請先 登錄

相關推薦

數字前端電路:簡單的邊沿檢測電路分析

數字前端電路:簡單的邊沿檢測電路分析

評論