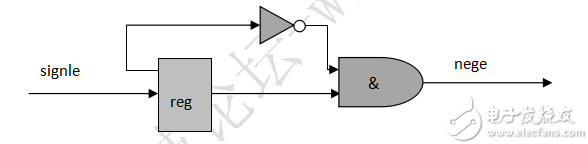

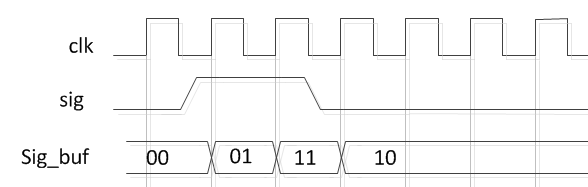

邊沿檢測電路(edge detection circuit)是個常用的基本電路。所謂邊沿檢測就是對前一個clock狀態(tài)和目前clock狀態(tài)的比較,如果是由0變?yōu)?,能夠檢測到上升沿,則稱為上升沿檢測電路(posedge edge detection circuit),若是由1變?yōu)?,能夠檢測到下降沿,則被稱為下降沿檢測電路(negedge edge dttection circuit),能夠同時(shí)檢測上升沿與下降沿的電路稱為雙沿檢測電路(double edge detection)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

檢測電路

+關(guān)注

關(guān)注

13文章

308瀏覽量

58177 -

邊沿檢測

+關(guān)注

關(guān)注

0文章

5瀏覽量

7834

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA設(shè)計(jì)中的邊沿檢測問題

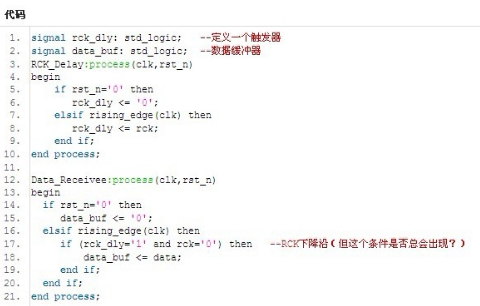

在同步電路設(shè)計(jì)中,邊沿檢測是必不可少的!后一種方法所耗的資源要比前一種方法多(一個觸發(fā)器),但是就可以大大提高可靠性,這絕對是物有所值!!

發(fā)表于 02-01 10:53

?980次閱讀

fpga應(yīng)用篇(二):邊沿檢測

`fpga應(yīng)用篇(二):邊沿檢測上一篇介紹了阻塞賦值與非阻塞賦值,這次我們利用非阻塞賦值產(chǎn)生一個簡單的應(yīng)用即邊沿檢測,邊沿

發(fā)表于 04-06 21:28

關(guān)于FPGA進(jìn)行外部邊沿檢測,檢測不準(zhǔn)確問題?

程序邊沿檢測下降沿并統(tǒng)計(jì)數(shù)量(數(shù)量到達(dá)2后重新計(jì)數(shù),并發(fā)送動作信號),但是最終發(fā)現(xiàn)檢測結(jié)果不準(zhǔn)確,有時(shí)候能檢測到,有時(shí)候檢測不到。萬分感謝您

發(fā)表于 08-21 12:58

用移位寄存器實(shí)現(xiàn)邊沿檢測的技巧

本文記錄一下關(guān)于用移位寄存器實(shí)現(xiàn)邊沿檢測的技巧。要學(xué)會硬件思維式的“模塊式”讀寫代碼,那么請多看別人的代碼,并用ISE或者VIVADO綜合出來看看。 邊沿檢測

發(fā)表于 04-15 10:26

?3296次閱讀

FPGA學(xué)習(xí)系列:12. 邊沿檢測設(shè)計(jì)

設(shè)計(jì)背景: 在我們工程設(shè)計(jì)中,有時(shí)會需要到上升沿和下降沿這么一個說法,通過上升沿和下降沿來驅(qū)動一個電路,那么學(xué)習(xí)邊沿檢測就非常的重要了。 設(shè)計(jì)原理 : 在學(xué)習(xí)邊沿

Verilog系統(tǒng)函數(shù)和邊沿檢測

“ 本文主要分享了在Verilog設(shè)計(jì)過程中一些經(jīng)驗(yàn)與知識點(diǎn),主要包括Verilog仿真時(shí)常用的系統(tǒng)任務(wù)、雙向端口的使用(inout)、邊沿檢測”

Verilog實(shí)現(xiàn)邊沿檢測的原理

邊沿檢測大致分為:上升沿檢測,下降沿檢測和,雙沿檢測。原理都是通過比輸入信號快很多的時(shí)鐘去采集信號,當(dāng)出現(xiàn)兩個連續(xù)的采集值不等的時(shí)候就是

邊沿檢測的目的及電路原理分析

邊沿檢測的目的及電路原理分析

評論