前幾天回了一位網(wǎng)友的貼子。這位網(wǎng)友的問題很經(jīng)典。整理一下,也許對其他朋友有點幫助。

Q1:

目前有這樣一個設計需求,該IC總體有數(shù)字部分和模擬部分組成,現(xiàn)在要求對數(shù)字部分插scan chain,實際芯片中數(shù)字部分很多輸入/輸出信號是直接連接到模擬電路,而不是連接到芯片的IO上,因為scan chain要求數(shù)字電路輸入可控和輸出可觀察,面對這種情況,實際在插scan chain時數(shù)字部分的輸入輸出一般是怎么處理,歡迎各位大佬指點,小弟不勝感激

Answer:

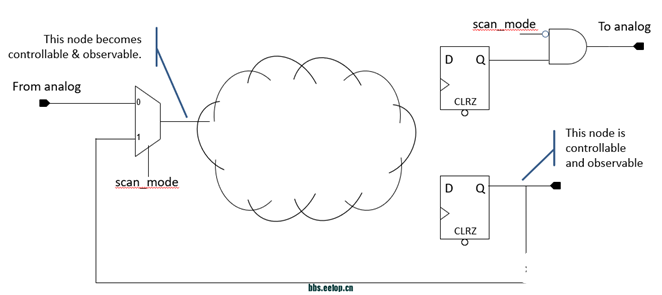

輸入:模擬到數(shù)字的信號不可控,需要和數(shù)字registered outputs mux一下提高test coverage。關鍵詞是registered output! 這個技巧俗稱scan loopback。

輸出: scan的時候不希望模擬控制信號頻繁上下跳動,要求把數(shù)字到模擬的輸出置為static low or high。注意:有的模擬模塊在scan的時候要求一直enable,對應的enable控制信號在scan時必須mux到static high。例如,部分數(shù)字是LDO供電,這部分數(shù)字在scan chain里,跑scan的時候LDO自然不能關掉。這個場景在低功耗設計中很常見。

示意圖如下。左邊是scan loopback mux,右邊是 scan tieoff。

Q2:

關于輸入信號處理時參與MUX的“registered outputs ” 怎么選取的呢,這里選擇哪一個register有什么講究嗎

Answer:

有講究,首選選離得近的,不然place & route會浪費太多routing resource,還會影響 timing。 參考一下top level layout 給 digital 的 pin location

如果是PLL之類,有些 timing critical 的 output 盡量不要拿來做 scan loopback,選一些不太重要的

Q3:

有幾個問題想再追問下:1.按照上述處理,是不是在真實的ATE測試時只需要控制芯片pin上的幾個scan信號就能完成scan測試?那是不是可以進一步理解成任何數(shù)字電路都可以按照上述思路處理,然后最后只通過pin上的幾個scan信號(不用任何PI/PO)完成ATPG測試?

2.上述處理后能保證覆蓋率嗎,在tmax產(chǎn)生ATPG時需要注意些什么?

3.在設計中有一個負沿的D觸發(fā)器,在插入DFT是設置了mix_edges,最后這個負沿的D觸發(fā)器串在了chain的最前面,這時會出現(xiàn)一個“1 Trailing edge port captured data affected by new capture violation”的違例,這種情況需要處理嗎?然后又怎么處理?

Answer:

1. 是的。通常 scan 信號可以復用 SPI, I2C,需要小心。減少整個片子 pin 數(shù)量,降低 package 成本,整個片子才會有競爭力。大廠的數(shù)模混合芯片沒有scan專用的pin就是這個道理。

2. 覆蓋率 95% 還是可以做到的,雖然加入的 scan mux 上損失一些覆蓋率,但是加入后提高了整個設計的覆蓋率。

3. 如果沒有 timing 問題, 不需要處理。 如果 setup 不能滿足,可以降低 scan 頻率。

Q4:

產(chǎn)生ATPG的still文件中依然會有對“form analog”和“to analog”這些信號有賦值等操作,感覺此時的still文件中不是應該就只有對scan的幾個信號有賦值或其他操作嗎?

Answer:

假設數(shù)字頂層是 digtop,有一堆 from_analog*, to_analog* 之類的 IO。這個 digtop 是不能直接給 ATPG tool 用的,要在外面加一個 wrapper,姑且稱為 digtop_tmax 吧。 這個 digtop_tmax 的 IO 應該只包括 scan pattern 能控制的 digtop input, 以及 scan pattern 能觀察到的 digtop output。 from_analog*, to_analog* 都不在 digtop_tmax 的 IO list 里。這樣最后的 stil 里就不會出現(xiàn) from_analog*, to_analog*

Q5:

那這個wrapper是在插scan chain完成后手動修改網(wǎng)表去形成,還是通過設置工具的某些命令去形成?

Answer:

這個 digtop_tmax 實際上相當于 chip_top 去掉其中的模擬部分。

如果 Cadence 里已經(jīng)有 chip_top 的 symbol view,生成一個 Verilog view, 再手動例化 digtop。

嫌麻煩就完全手動

Q6:

1.這樣操作是不是又要重新生成新的spf文件? 設計中from annlog 和 to analog的pin巨多,手動是不是太麻煩了 。

2.我看了下DFTMAX的ug,在第12章節(jié)講了wrapper cores ,我在想是不是我這種類型的設計能不能在RTL階段不做任何代碼處理,在DFT時直接走wrapper cores的流程,這樣具有可行性嗎?

Answer:

RTL 階段插入 scan mux, scan loopback。

跑 TetraMAX 的時候?qū)懸粋€ digtop_tmax 或 chip_top,僅僅用于跑 generate spf。

這里有個省時的小竅門。 scan 相關的 port 一般就 5/6 個信號。digtop_tmax 里接上這幾個信號就可以了。 其他的像 from_analog*, to_analog*, ATE 根本看不到,也不需要看到。例化 digtop 的時候這些信號可以不出現(xiàn)在 port mapping 里,大大簡化 digtop_tmax 的工作量。工具會自動把這些 from_analog*, to_analog* 當成 X 處理,這也正是我們希望的

Q7:

我們的設計數(shù)字電路大概有1500個D觸發(fā)器,從測試成本和測試時間來考慮(scan 的pin可以適當多些),一般插幾條chain比較合適?這里chain的條數(shù)的定義一般是怎么評估的呢

Answer:

1. 片子的 package 最多能有幾個 digital I/O。 數(shù)模混合片子大部分 I/O 都是模擬,數(shù)字很少,scan pin 數(shù)量的上限就在那里,也就限制了 scain chain 的條數(shù)。如果允許,當然時多幾條 scan chain 更好,減少 test time。 但是 package 也是成本的很大部分,不能隨心所欲增加 digital I/O 增加 scan chain 數(shù)量。有時 package 是用戶使用場景決定的,無法選大的。例如8 pin package, 內(nèi)部模擬數(shù)字一大堆,也蠻常見的。

2. 為了減少 test time, 可以考慮 scan 跑得快一些。 很多時候 scan mode 時鐘比 functional mode 時鐘快很多倍就是這個道理

Q8:

1.之前幾天僅僅是把DFT流程跑通,沒有關注測試模式下timing的問題,我想問下在測試模式下,scan的時鐘和scan的信號怎么約束,和function 模式結合起來約束又該如何考量(是不是要用set_case_analysis之類的命令)? 實際跑function的頻率就幾十M,這種測試模式下需要有at-speed的考慮嗎?

Answer:

1. Timing 分析可以用 MMMC (multi-mode multi-corner)。Mode 分成兩個,func_mode, scan_mode,寫兩個 SDC。

func_mode SDC 第一句: set_case_analysis 0 [get_port scan_mode*]

scan_mode SDC 第一句: set_case_analysis 1 [get_port scan_mode*]

scan_mode SDC 里 create_clock -name scan_clock 可以跑得快一點。如果 scan_clock 可以超過 functional clock,at-speed test 就不重要了。

很重要的一點,一定要跑 sdf 反標后仿,把所有 vector 跑一遍,確認無誤。 很多時候跑 sdf 反標后仿可以發(fā)現(xiàn)問題。

審核編輯:黃飛

-

信號處理

+關注

關注

48文章

1041瀏覽量

103370 -

模擬信號

+關注

關注

8文章

1142瀏覽量

52585 -

數(shù)字信號

+關注

關注

2文章

982瀏覽量

47628 -

控制信號

+關注

關注

0文章

168瀏覽量

12020

發(fā)布評論請先 登錄

相關推薦

如何通過仿真有效提高數(shù)模混合設計性

數(shù)模混合電路設計的難點

我的數(shù)模混合設計難點經(jīng)驗

數(shù)模混合SOC芯片的可測性方案的實現(xiàn)

請教Chipscope和boundary chain問題

幫你理解DFT中的scan technology

數(shù)模混合電路設計的難點

射頻與數(shù)模混合類高速PCB設計

數(shù)模混合仿真在以太網(wǎng)芯片設計中的應用

DS26522 JTAG Scan Chain Mappin

一文讀懂DC/AC SCAN測試技術

知存科技數(shù)模混合存算一體AI芯片專利解析

MCU芯片設計了mbist、scan chain之后,功能仿真失敗?

是否需要補插scan chain的isolation cell?怎么插呢?

芯片設計測試中scan和bist的區(qū)別

數(shù)模混合芯片scan chain問題解析

數(shù)模混合芯片scan chain問題解析

評論