(1)DUT模型的建立

?① 164245模型:在Modelsim工具下用Verilog HDL語言[5],建立164245模型。164245是一個(gè)雙8位雙向電平轉(zhuǎn)換器,有4個(gè)輸入控制端:1DIR,1OE,2DIR,2OE;4組8位雙向端口:1A,1B,2A,2B。端口列表如下:

input DIR_1,DIR_2,OE_1,OE_2;inout [0:7] a_1,a_2,b_1,b_2;reg [0:7]

bfa1,bfb1,bfa2,bfb2;//緩沖區(qū)

?② 緩沖器模型:建立一個(gè)8位緩沖器模型,用來做Test bench 與164245 之間的數(shù)據(jù)緩沖``

(2)Test bench的建立

依據(jù)器件功能,建立Test bench平臺(tái),用來輸入仿真向量。 Test bench中變量定義:

reg dir1,dir2,oe1,oe2; //輸入控制端

reg[0:7] a1,a2,b1,b2; //數(shù)據(jù)端

reg[0:7] A1_out[0:7]; //存儲(chǔ)器,用來存儲(chǔ)數(shù)據(jù)

reg[0:7] A2_out[0:7];reg[0:7] B1_out[0:7];reg[0:7] B2_out[0:7];

通過Test 圖6 Test bench驗(yàn)證平臺(tái)框圖

圖6 Test bench驗(yàn)證平臺(tái)框圖

(3)仿真和驗(yàn)證

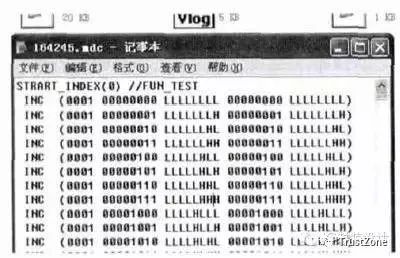

通過Test bench 給予相應(yīng)的測(cè)試激勵(lì)進(jìn)行仿真,得到預(yù)期的結(jié)果,實(shí)現(xiàn)了器件功能仿真,并獲得了測(cè)試圖形。圖7和圖8為部分仿真結(jié)果。

圖7 仿真數(shù)據(jù)結(jié)果

圖7 仿真數(shù)據(jù)結(jié)果

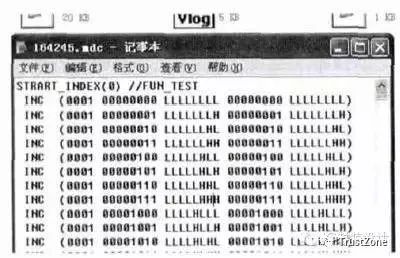

在JC-3165的*.MDC圖形文件中,對(duì)輸入引腳,用“1”和“0”表示高低電平;對(duì)輸出引腳,用“H”和“L”表示高低電平;“X”則表示不關(guān)心狀態(tài)。

由于在仿真時(shí),輸出也是“0”和“1”,因此在驗(yàn)證結(jié)果正確后,對(duì)輸出結(jié)果進(jìn)行了處理,分別將“0”和“1”轉(zhuǎn)換為“L”和“H”,然后放到存儲(chǔ)其中,最后生成*.MDC圖形文件。

圖8 生成的*.MDC文件

圖8 生成的*.MDC文件

-

測(cè)試

+關(guān)注

關(guān)注

8文章

5367瀏覽量

126921 -

IC

+關(guān)注

關(guān)注

36文章

5976瀏覽量

175976 -

模型

+關(guān)注

關(guān)注

1文章

3294瀏覽量

49037 -

DUT

+關(guān)注

關(guān)注

0文章

189瀏覽量

12458

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【轉(zhuǎn)】基于ISE的仿真

一種新的建立自動(dòng)測(cè)試系統(tǒng)的方法

新型雷達(dá)數(shù)字電路便攜式自動(dòng)測(cè)試系統(tǒng)設(shè)計(jì)

一種變頻器測(cè)試平臺(tái)及變頻器測(cè)試平臺(tái)的調(diào)試方法

FPGA實(shí)戰(zhàn)開發(fā)技巧(4)

基于MapXtreme的虛擬漫游2D導(dǎo)航地圖建立方法研究_朱振和

基于雷達(dá)的雜波速度譜圖的建立方法

一種云平臺(tái)可信性分析模型建立方法

ISE環(huán)境下基于Verilog代碼的仿真測(cè)試pdf下載

基于ISE的仿真

基于計(jì)算機(jī)模擬技術(shù)的太陽能光伏發(fā)電系統(tǒng)數(shù)學(xué)模型的建立方法

華為推送會(huì)話的建立方法的優(yōu)點(diǎn)

測(cè)試平臺(tái)的建立方法

測(cè)試平臺(tái)的建立方法

評(píng)論