隨著市場更高的需求,現在的設計者不得不考慮提高時鐘頻率,縮短信號的上升邊沿。

對于市面上大多數電子產品而言,普遍認為當時鐘頻率超過100 mhz或上升邊沿小于1ns時,信號質量因素就必須考慮。

在模擬電路中,設計者主要考慮物理源引發的噪聲,物理源通常包括熱噪聲、短噪聲等。

一方面,這些噪聲源決定了所能放大信號的最小下限;另一方面也決定了所能放大信號的最大上限。

在數字電路中,噪聲不是來自于基本的物理源,而是來自于運行著的電路本身,尤其是其他信號頻繁翻轉所產生的噪聲。

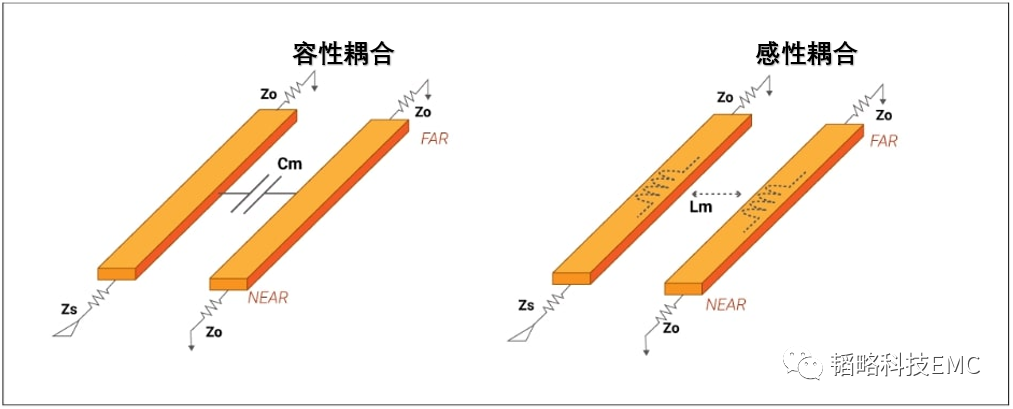

高度化的互連密度導致了每個網絡與其余網絡相隔更近,從而引起了相鄰網絡的容性耦合。

從而接上文接著講信號質量邊沿、振蕩、串擾及時序處理的相關技術處理及解決。

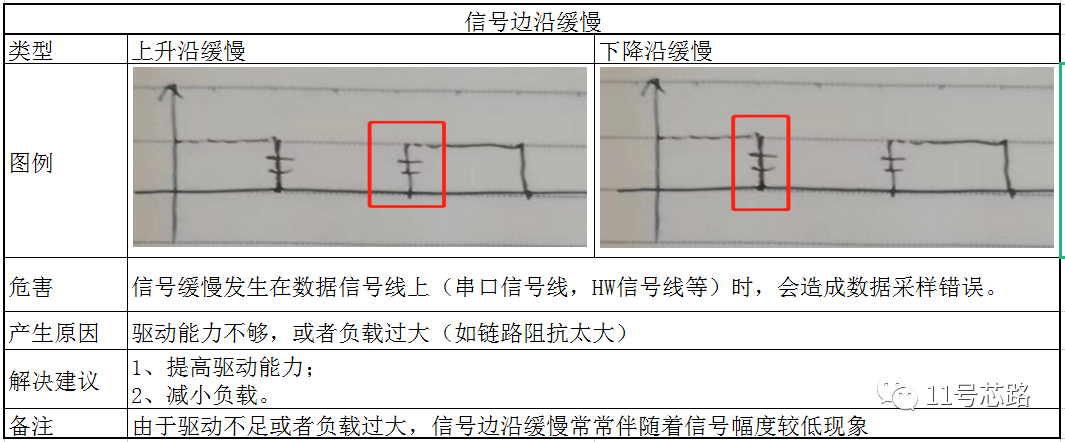

1、信號邊沿緩慢

2、信號振蕩

3、信號的建立和保持時間

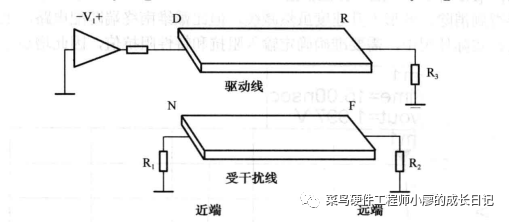

4、信號串擾

閱讀 21

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

處理器

+關注

關注

68文章

19404瀏覽量

230804 -

模擬電路

+關注

關注

125文章

1573瀏覽量

102857 -

振蕩器

+關注

關注

28文章

3847瀏覽量

139277 -

數字電路

+關注

關注

193文章

1629瀏覽量

80755 -

熱噪聲

+關注

關注

0文章

46瀏覽量

8183

發布評論請先 登錄

相關推薦

高速互連信號串擾的分析及優化

高速數字設計領域里,信號完整性已經成了一個關鍵的問題,給設計工程師帶來越來越嚴峻的考驗。信號完整性問題主要為反射、串擾、延遲、振鈴和同步開關噪聲等。本文基于高速電路設計的

發表于 05-13 09:10

pcb上的高速信號需要仿真串擾嗎

pcb上的高速信號需要仿真串擾嗎? 在數字電子產品中,高速信號被廣泛應用于芯片內部和芯片間的數據傳輸。這些信號通常具有高帶寬,并且需要在特定

信號質量邊沿、振蕩、串擾及時序處理剖析

信號質量邊沿、振蕩、串擾及時序處理剖析

評論