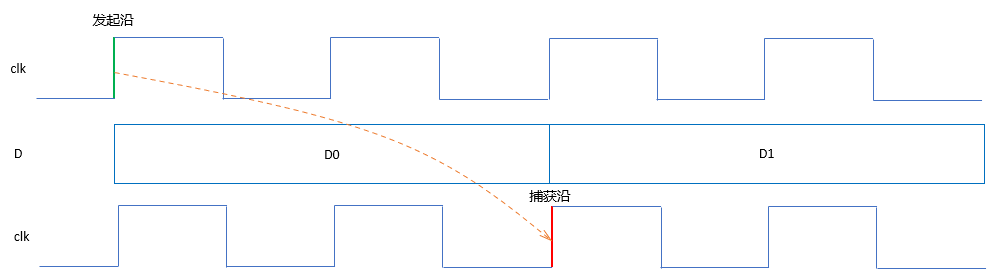

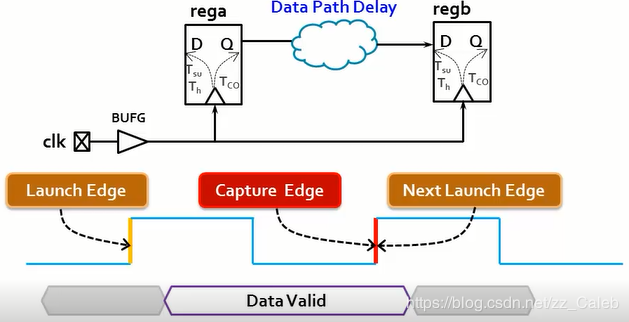

命令set_multicycle_path常用來約束放松路徑的約束。通常情況下,這種路徑具有一個典型的特征:數據多個周期翻轉一次,如下圖所示。因此,我們把這種路徑稱為多周期路徑(FPGA設計中更多的是單周期路徑,每個周期數據均翻轉)。

一般情況下,多周期路徑約束的對象都是FPGA內部路徑,路徑所包含的邏輯單元也都是FPGA內部單元如觸發器、BRAM或DSP等。但有時在片間接口使用set_input_delay和set_output_delay約束時,也會用到set_multicycle_path。這里我們就來討論這種情形。

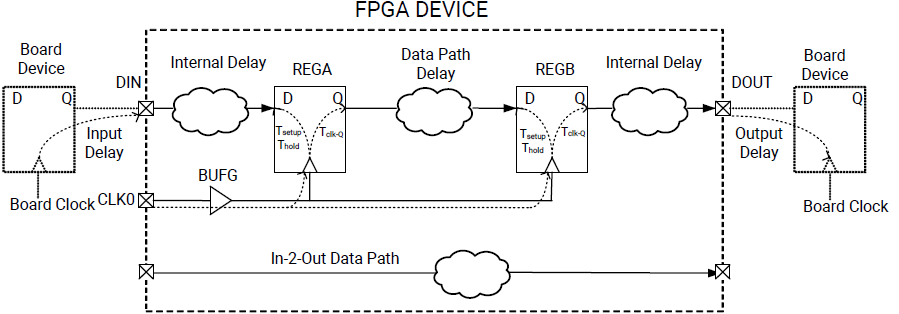

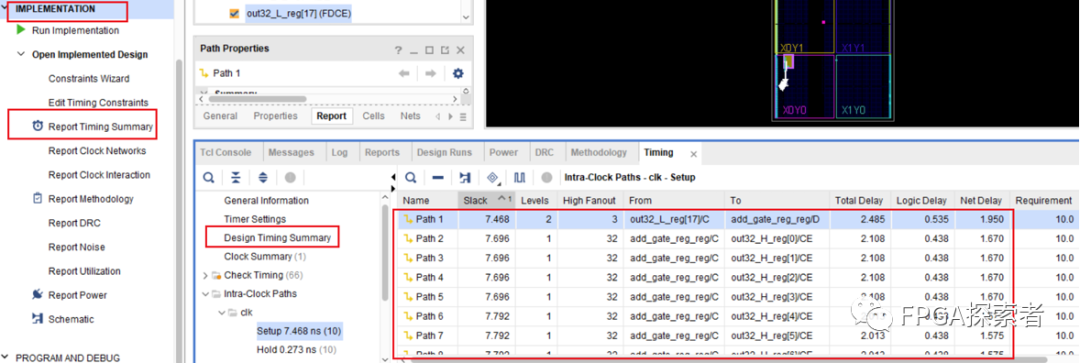

我們先從系統級角度看一下FPGA設計存在的4類時序路徑,如下圖所示。這4類路徑包括:上游芯片到FPGA管腳(用set_input_delay約束)、FPGA內部路徑(用create_clock約束)、FPGA管腳到下游芯片(用set_output_delay約束)和FPGA管腳到FPGA管腳(用set_max_delay約束)。就前三條路徑而言,如果把上游芯片、FPGA芯片和下游芯片作為一個整體看待,我們就會發現這三條路徑本質上是一類路徑,起點單元和終點單元都是觸發器。只是觸發器可能在FPGA外部而已。正因此,凡是適合于FPGA內部路徑的多周期路徑約束情形也適合于接口多周期路徑約束情形。同時,也能看出Vivado的這種系統級的時序分析引擎對接口時序約束極為便利。

情形1:數據每多個時鐘周期翻轉一次

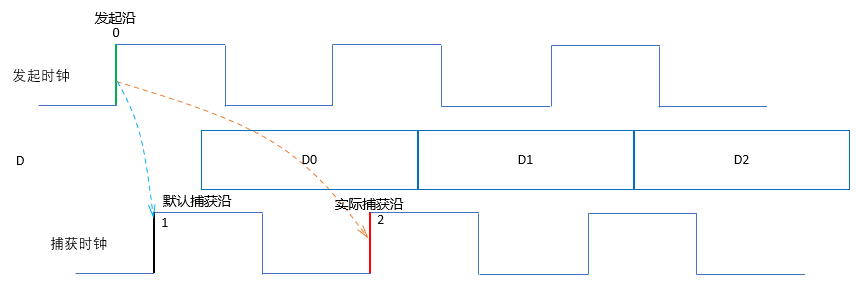

如下圖所示時序波形,數據每兩個時鐘周期翻轉一次。

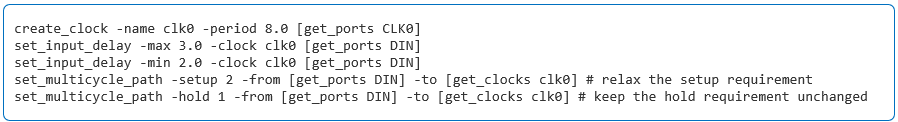

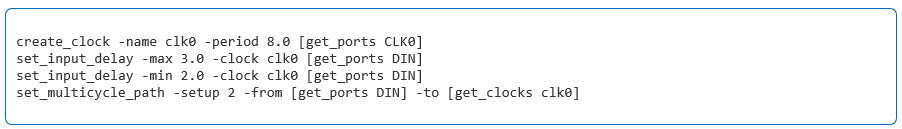

如果數據是由上游芯片發送給FPGA,那么就需要用set_input_delay結合set_multicycle_path一起對接口路徑進行約束,如下圖所示。這里最后兩行使用了set_multicycle_path,一個針對建立時間,一個針對保持時間。

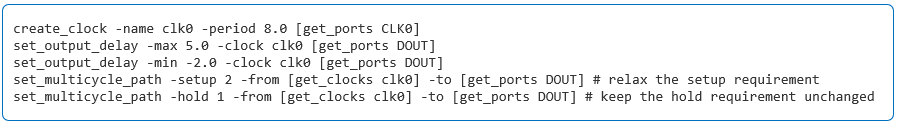

如果數據是從FPGA發送給下游芯片,那么就需要用set_output_delay結合set_multicycle_path一起對接口路徑進行約束,如下圖所示。

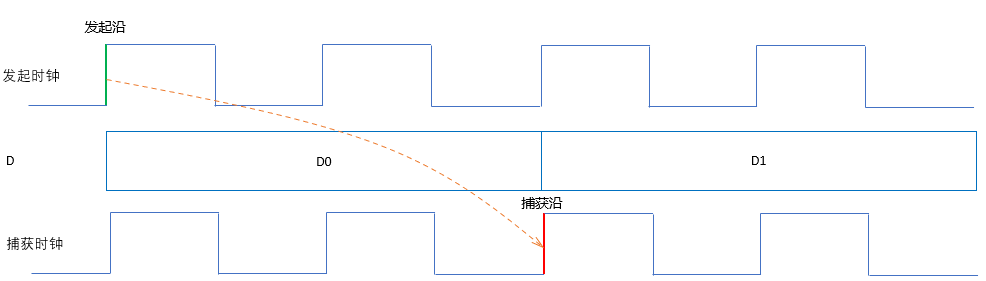

情形2:捕獲時鐘和發送時鐘同頻但有相差

如下圖所示,發起時鐘和捕獲時鐘同頻但不同相。默認情況下,Vivado會選擇兩個時鐘最為接近的邊沿作為發起沿和捕獲沿,如圖中的藍色箭頭所示。顯然,這種情況下,時序約束過緊且不符實際。這就要通過set_multicycle_path告訴工具真正的捕獲沿是在2號標記處。

如果該路徑存在于FPGA輸入接口處,那么可以采用set_input_delay結合set_multicycle_path一起約束,如下圖所示。

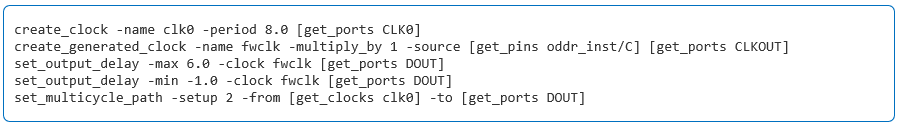

如果該路徑存在于FPGA輸出接口處的源同步設計,那么可以采用set_output_delay結合set_multicycle_path一起約束,如下圖所示。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1630文章

21794瀏覽量

605129 -

FPGA設計

+關注

關注

9文章

428瀏覽量

26578 -

命令

+關注

關注

5文章

695瀏覽量

22073 -

約束

+關注

關注

0文章

82瀏覽量

12756

原文標題:對于輸入/輸出路徑什么場合需要用set_multicycle_path?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

詳細解析vivado約束時序路徑分析問題

FPGA時序約束之偽路徑和多周期路徑

FPGA時序分析之關鍵路徑

fpga時序分析案例 調試FPGA經驗總結

FPGA實戰演練邏輯篇52:基本時序路徑

全面解讀時序路徑分析提速

FPGA設計存在的4類時序路徑

FPGA設計存在的4類時序路徑

評論