我們華林科納通過光學反射光譜半實時地原位監測用有機堿性溶液的濕法蝕刻,以實現用于線波導的氫化非晶硅(a-Si:H)膜的高分辨率厚度控制。由a-Si:H的本征各向同性結構產生的各向同性蝕刻導致表面粗糙度<1nm的均勻蝕刻。適度的蝕刻速率使得能夠在室溫下以≤1nm的分辨率進行精確的終點檢測。由蝕刻的A-Si:H薄膜制成的線波導具有1.2dB/cm的低傳播損耗,這幾乎相當于未蝕刻的線波導。

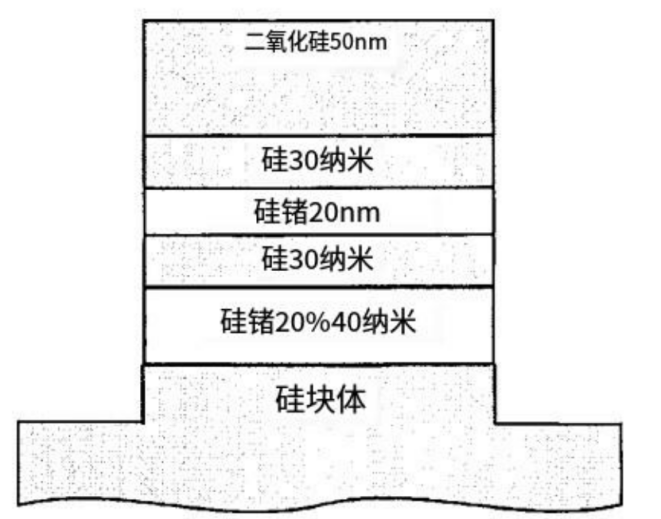

用硅材料制成的光波導部分取代全球金屬布線,有望在大規模集成器件中實現更快的信號傳輸和更大的節能。硅材料由于其高折射率和互補金屬氧化物半導體(CMOS)工藝兼容性,使得能夠低成本制造尺寸與布線電路相當的超小型光學電路。在硅材料中,氫化非晶硅(a-Si:H)是一個很有前途的例子,因為它允許通過低溫等離子體增強化學氣相沉積(PECVD)在現有的電層上連續形成硅波導。到目前為止,一些小組已經使用a-Si:H材料制造了高質量的線波導。

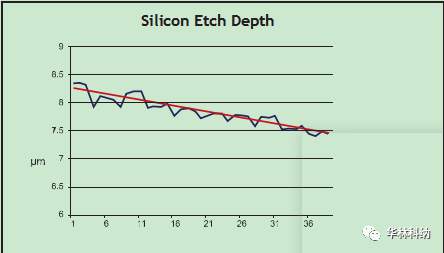

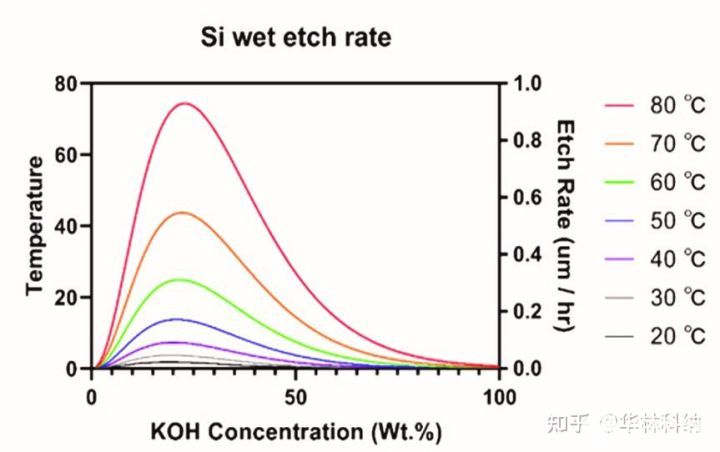

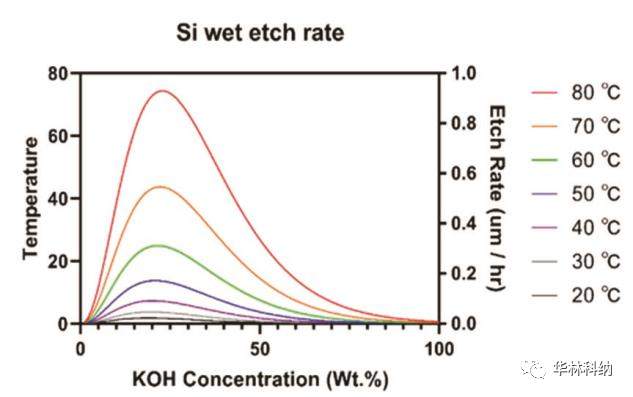

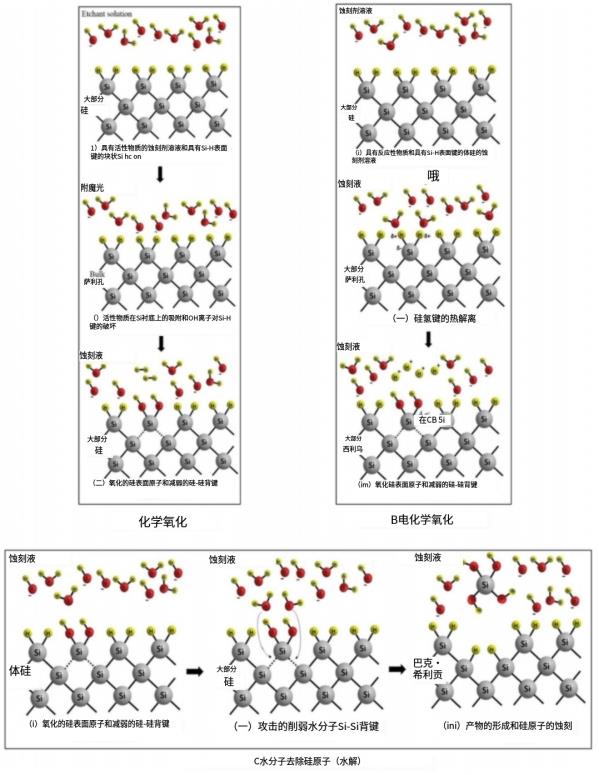

然而,用于生長a-Si:H膜的PECVD工藝通常在膜厚度上產生65%的偏差。對于厚度為200nm的膜,該偏差對應于610nm,這對于許多器件應用,尤其是那些對波長敏感的器件應用是不可接受的。因此,在PECVD之后需要額外的工藝來提供具有納米級分辨率的精確厚度控制。化學機械拋光(CMP)已被用于調整a-Si:H膜的厚度。1-3然而,通常很難高精度地檢測CMP的終點。在這封信中,作為CMP的替代方法,我們報告了濕蝕刻方法與半實時光學厚度監測器相結合的實用性,以提供分辨率為~1nm的精細厚度控制。這種方法不會顯著增加沉積態a-Si:H膜的表面粗糙度,從而能夠制造出具有低傳播損耗of~1dB/cm的線波導。

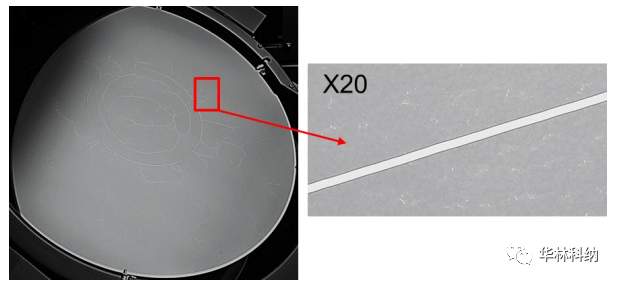

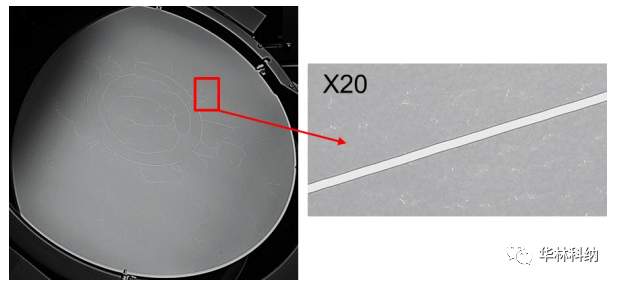

使用原子力顯微鏡的輕敲模式評估室溫下蝕刻前后的表面粗糙度。8蝕刻前膜的均方根表面粗糙度為0.739nm,蝕刻后膜的均均方根表面粗度為0.891nm,蝕刻在220nm的膜厚度處停止。因此,即使在通過蝕刻去除約100nm的膜之后,表面粗糙度也僅略有增加。對于薄膜上的幾個點獲得了一致的結果。

總之,我們華林科納為了實現PECVD沉積a-Si:H薄膜的高分辨率厚度控制,開發了一種使用TMAH溶液和光學反射光譜半實時原位厚度監測的濕法蝕刻方法。由于室溫下~4nm/min的適度蝕刻速率和~2s的測量響應時間相結合,蝕刻終點可以控制在≤1nm的分辨率。即使在通過蝕刻去除約100nm的膜之后,膜的表面粗糙度也僅略有增加。由蝕刻的a-Si:H膜制成的線波導的傳播損耗幾乎等于未蝕刻的線波導,并且是迄今為止報道的最低的。所開發的蝕刻方法可用于生產低傳播損耗波導器件,并且與CMOS工藝具有良好的兼容性。

為更好的服務客戶,華林科納特別成立了監理團隊,團隊成員擁有多年半導體行業項目實施、監督、控制、檢查經驗,可對項目建設全過程或分階段進行專業化管理與服務,實現高質量監理,降本增效。利用仿真技術可對未來可能發生的情況進行系統的、科學的、合理的推算,有效避免造成人力、物力的浪費,助科研人員和技術工作者做出正確的決策,助力工程師應對物理機械設計和耐受性制造中遇到的難題。

審核編輯 黃宇

-

半導體

+關注

關注

334文章

27687瀏覽量

221418 -

監測

+關注

關注

2文章

3653瀏覽量

44663 -

蝕刻

+關注

關注

9文章

419瀏覽量

15489 -

波導

+關注

關注

3文章

98瀏覽量

18877 -

光波導

+關注

關注

4文章

48瀏覽量

10225

發布評論請先 登錄

相關推薦

雷尼紹測頭為什么具有各向同性

《炬豐科技-半導體工藝》CMOS 單元工藝

《炬豐科技-半導體工藝》GaN晶體蝕刻的幾何方面和光子應用

用于硅片減薄的濕法蝕刻工藝控制

常見的各向同性濕法刻蝕的實際應用

鍺化硅(SiGe)和硅(Si)之間的各向同性和選擇性蝕刻機制

使用各向同性濕蝕刻和低損耗線波導制造與蝕刻材料對非晶硅進行納米級厚度控制

使用各向同性濕蝕刻和低損耗線波導制造與蝕刻材料對非晶硅進行納米級厚度控制

評論